Fターム[5J106HH01]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 制御量 (1,632) | 周波数 (367)

Fターム[5J106HH01]に分類される特許

121 - 140 / 367

温度補償型水晶発振器の温度補償値設定方法

【課題】 各温度におけるD/A変換器の温度補償値を短時間で取得できる温度補償型水晶発振器の温度補償値設定方法を提供する。

【解決手段】 PC23が、PLL回路21からロック信号が入力されるまでは、PLL回路21からの制御電圧出力を選択してVCXO16に入力するようSW15を制御し、PLL回路21からロック信号を入力すると、A/D変換器12からの検出温度の値とPLL回路21からの制御電圧出力についてバッファ18、A/D変換器19により得られた電圧値を記憶すると共に、CPU13の内部メモリにロック状態の検出温度の値と制御電圧の値として設定して、D/A変換器14への温度補償値を取得する温度補償型水晶発振器の温度補償値設定方法である。

(もっと読む)

広帯域PLL発振回路

【課題】周波数逓倍回路を含む広帯域PLL発振回路において、逓倍回路出力端に高調波等の不要周波数信号を除去するフィルタを必要とせず、簡単な構成によって不要周波数信号に起因して間違った周波数に同期することなく、安定した動作が得られる広帯域PLL発振回路を提供する。

【解決手段】

逓倍回路に同調周波数制御機能を備え、発振周波数に応じて適切な同調周波数になるように制御する。また、PLLロックインまでの時間短縮のためにメモリに記憶した制御電圧情報をVCOに印加する機能を備え、この制御電圧情報によって同時に逓倍回路の同調周波数を制御する。

(もっと読む)

タイム/デジタルコンバーター及びデジタル位相ロックループ

【課題】 本発明の目的は、入力される2つの信号の位相差だけでなく周波数の差まで検出することができるタイム/デジタルコンバーター及びこれを用いるデジタル位相ロックループを提供することを目的とする。

【解決手段】 タイム/デジタルコンバーターが開示される。本タイム/デジタルコンバーターは、第1信号及び第2信号を受信し、直列接続された複数の遅延素子を用いて第2信号を段階的に遅延させ、遅延された第2信号と第1信号とを比較して第1信号に対する第2信号の位相エラーを出力するコンバーターと、第1信号及び複数の遅延素子のノードのうち一つのノードから第3信号を受信し、第1信号及び第3信号に対する位相差を出力する位相周波数検出器と、位相周波数検出器の出力信号と第2信号を用いて、第1信号に対する第2信号の周波数エラーをデジタルコードに出力する周波数検出器と、を含む。これにより、本タイム/デジタルコンバーターは入力される2つの信号間の位相差だけでなく周波数の差まで検出することができる。

(もっと読む)

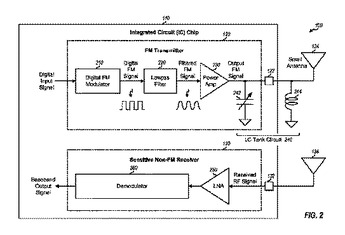

シングルチップ上に集積されたFM送信機及び非FM受信機

例示的な態様は、周波数変調(FM)送信機及び非FM受信機を含み、それらは同一のICチップ上にインプリメントされる。FM送信機は、デジタルFM変調器、ロウパスフィルタ、増幅器、及びLCタンク回路を含む。デジタルFM変調器は、デジタル入力信号を受け取り、デジタル入力信号によってFM変調を行い、デジタルFM信号を供給する。ロウパスフィルタは、デジタルFM信号をフィルタし、フィルタされたFM信号を供給する。増幅器は、フィルタされたFM信号を増幅し、出力FM信号を供給する。LCタンク回路は、出力FM信号をフィルタする。デジタルFM変調器は、PLL内のマルチモジュール分周器の可変分周比を変化させることによってFM変調を行う。デルタ−シグマ変調器は、デジタル入力信号を受け取り、可変分周比を得るために用いられる変調器出力信号を発生する。  (もっと読む)

(もっと読む)

PLL回路

【課題】PLL回路におけるPLL応答特性を、参照電圧に応じた所望の特性にする。

【解決手段】PLL回路は、入力された電圧に応じた周波数で発振することにより、内部信号を生成する発振部と、前記内部信号を分周して分周信号を生成する分周部と、外部から入力された基準信号の位相と前記分周部から受けた前記分周信号の位相とを比較し、比較結果に応じた位相誤差信号を出力する位相比較部と、前記位相誤差信号に基づいて制御電圧を生成する生成部とを有するPLL回路であって、前記生成部から出力された前記制御電圧が前記発振部へ入力される第1の状態と、参照電圧が前記発振部へ入力される第2の状態とを切り替える切り替え部と、前記第2の状態において、前記分周信号の周波数と前記基準信号の周波数とを比較し、前記分周信号の周波数が前記基準信号の周波数に等しくなるように、前記発振部に入力された電圧に対する前記発振部における発振する周波数を補正する補正部とを備える。

(もっと読む)

基準クロック周波数の決定および/またはループ発振器のロックを行うための方法、アルゴリズム、回路、およびシステム

【解決手段】 基準クロックの周波数を決定する装置、方法、システム、アルゴリズム、および回路を開示する。一実施形態によると、基準クロックの周波数を検出する回路であって、周波数が既知であり、精度は所定の値であるスリープクロックの所定の部分の間、基準クロックのサイクル数をカウントして、基準クロックサイクルカウント値を得るクロックカウンタと、基準クロックサイクルカウント値および既知であるスリープクロックの周波数に基づいて、基準クロックの周波数を推定する周波数推定部と、複数の許容周波数から、推定された基準クロックの周波数に最も近い周波数を選択する周波数選択部とを備える回路が提供される。 (もっと読む)

基準信号発生装置

【課題】、目的周波数の基準信号の異常を、確実且つ正確に検出することができる基準信号発生装置を実現する。

【解決手段】基準信号発生装置1は、位相比較器11、ループフィルタ12、電圧制御発振器13、分周器14からなるPLL回路を備える。基準信号発生装置1の波数計測部15は、PLL回路の調整用タイミング信号に基づく期間での復調用基準周波数信号の波数をカウントし、期間毎のカウント値を異常発振検出部16へ出力する。異常発振検出部16は、調整用タイミング信号の元となる基準信号と復調用基準周波数信号との仕様周波数範囲の関係に基づいて設定される正常発振カウント値範囲を予め記憶している。異常発振検出部16は、波数計測部15から取得したカウント値が正常発振カウント値範囲内に無ければ異常発振として検出し、外部へ通知する。

(もっと読む)

圧電発振器、および圧電発振器を用いた受信装置

【課題】温度補償回路を内蔵しない圧電発振器を用いて、GPS衛星の測位信号の捕捉時

間を短縮化させることができる圧電発振器、その圧電発振器を用いた受信装置および圧電

発振器を用いた受信装置の衛星捕捉制御方法を提供する。

【解決手段】圧電発振器用IC2と圧電振動子4を同一パッケージに組み立てて圧電発振

器1を構成すると、温度センサ7は精度よく圧電振動子4の温度を検出できる。圧電発振

器1を恒温槽に入れて、温度Tと出力周波数foutの周波数の関係を取得する。得られた

周波数−温度特性より、温度係数(A,B,C,D)とオフセット係数(E)を算出して

メモリ10に書き込む。この圧電発振器1を受信装置に組み込んだときにメモリ10から

温度係数とオフセット係数を抽出して近似曲線計算式から圧電発振器1の周波数偏差を求

め、周波数偏差分だけ、衛星からの探索範囲をオフセットさせて、GPS衛星の周波数を

捕捉する。

(もっと読む)

クロッククリーンアップ位相ロックループ(PLL)

【解決手段】スプリアスを低減し受信機性能を向上し得るクロッククリーンアップ位相ロックループ(PLL)が述べられる。典型的な一設計では、集積回路はPLL及びアナログ/デジタルコンバータ(ADC)を含む。PLLは、フラクショナル分周比で生成され、突発的周波数ジャンプによるスプリアスを有する第1クロック信号を受信する。第1クロック信号は、集積回路外部のフラクショナルNの周波数シンセサイザによって生成され得る。PLLは、整数の分周比で、低減されたスプリアスを有する第2クロック信号を生成する。ADCは、第2クロック信号に基づいてアナログベースバンド信号をデジタル化してデジタルサンプルを供給する。集積回路は更に、低ノイズ増幅器(LNA)を有し、これは第1クロック信号をクリーンアップするPLLの使用により、集積回路の基板を介して結合するより小さいスプリアスを観測し得る。 (もっと読む)

信号処理装置及び信号処理方法

【課題】ロック状態を維持したまま、発振周波数のVCO制御電圧特性を粗調整する。

【解決手段】VCO63は、トランジスタを内蔵し、入力されたVCO制御電圧に対応する発振周波数を発生させ、LPF131a乃至131dは、VCO63が内蔵するトランジスタのゲートに、予め決められた変化率でトランジスタのゲート電圧を変化させる入力電圧を入力し、VCO制御電圧に対する、発振周波数のVCO制御電圧特性を粗調整する。本発明は、例えばPLL回路やCDR回路に適用することができる。

(もっと読む)

発振回路、及び映像表示装置

【課題】小規模の回路追加により、既存の回路を有効に活用しながら映像信号のクロックの周期とサンプリングクロックの周期との齟齬を解消する発振回路、及び映像表示装置を提供することを課題とする

【解決手段】分周器33と位相比較器31とを有する生成回路3へ、所定の発振信号を供する発振回路4であって、位相比較器31における比較結果に応じた周期のクロック信号を生成するクロック信号生成部42と、クロック信号生成部42が生成したクロック信号の一部をマスクした信号を分周器33へ供するクロック信号マスク部43と、を備え、クロック信号マスク部43は、生成回路3が生成するサンプリング信号の周期が、映像信号を生成する際に用いられるクロックの周期と同じになるようにクロック信号の一部をマスクする。

(もっと読む)

信号の較正方法および装置

信号較正方式において、一連の複数の信号の間で所望の位相関係が維持される。たとえば、いくつかの態様では、高速度の基準クロック信号から発生したクロックツリーの所望の位相を、低速度の基準クロック信号と、クロックツリーの様々な位相に関連付けられた低速度のクロック信号との間の位相差を検出することにより、維持することが可能である。いくつかの態様では、クロックツリーの使用中に発生するフレーミングオフセットを検出することにより、クロックツリーの所望の位相を維持することが可能である。 (もっと読む)

CR発振クロック内蔵マイクロコンピュータ

【課題】CR発振クロックの周期調整が完了したかを判定できるCR発振クロック内蔵マイクロコンピュータの提供。

【解決手段】判定回路は、カウント数下限設定レジスタが示す値とカウント数上限設定レジスタが示す値との間に、外部発振パルスカウンタが示す値が収まっているかを判定する(S170)。収まっていると判定すると(S170でYes)、判定回路は、補正完了カウンタに格納されている値に1を足してカウントアップする(S180)。その後、出力回路が、補正完了カウンタのカウント数が補正完了カウント数設定レジスタに格納された値以上であるかを判断する(S190)。以上であると判断すると(S190でYes)、出力回路は、補正完了レジスタに「1」(周期調整が完了したことを示す情報)を入力する(S200)。そして、これらのステップを繰り返す。

(もっと読む)

受信回路

【課題】入力データに位相を合わせたクロック信号を安定的かつ低消費電力で得る受信回路を提供する。

【解決手段】受信回路において、制御回路30、発振回路40、分周回路50、フリップフロップ回路、第1および第2の位相比較回路などを備え、発振回路40の発振周波数は、入力データに信号情報が有る時にはクロック信号と入力データの位相比較結果に基づいて制御し、入力データに信号情報が無い時にはクロック信号を分周して得たフィードバック信号と一定の周期で変化するリファレンス信号の位相比較結果に基づいて制御する。発振回路40は、2系統の制御信号によって発振周波数を制御でき、一方の系統の制御信号の変化に対しては徐々にかつ大きく発振周波数が変化し、他方の系統の制御信号の変化に対しては直ちにかつ小さく(少しだけ)発振周波数が変化するように構成する。

(もっと読む)

半導体集積回路

【課題】チップ占有面積が低減され、ディジタル制御発振器DCOの制御ゲインのばらつきを低減する。

【解決手段】半導体集積回路はディジタル制御発振器DCOを具備し、DCOは発振素子NM1、NM2と共振回路20を含み、共振回路20はインダクタンスL11、L12と周波数粗調整用可変容量アレーCCT11と周波数微調整用可変容量アレーCFT11と含む。粗調整用可変容量アレーCCT11は複数個の粗調整容量ユニットセルCCT<0>、<1>…を含み、微調整用可変容量アレーCFT11は複数個の微調整容量ユニットセルCFT<0>、<1>…を含む。粗調整用アレーCCT11の複数個の粗調整容量ユニットセルの容量値はバイナリウェイト2M−1に従って設定され、微調整用アレーCFT11の前記複数個の微調整容量ユニットセルの容量値もバイナリウェイト2N−1に従って設定される。

(もっと読む)

無線通信端末および無線通信制御方法

【課題】クロック信号の周波数を大きく変更することなく、クロック信号の高調波による受信信号への影響を抑制する。

【解決手段】制御部13により、受信信号に影響を与えるクロック信号16Sの高調波17Sが持つ高調波周波数が、受信搬送波周波数と一致するように、PLL回路16Aの分周比を制御して前記クロック周波数を調整する。

(もっと読む)

PLL発振回路

【課題】ループ中に、バッファアンプや逓倍回路と、不要周波数成分を除去するフィルタを含むPLL発振回路において、広帯域に発振周波数を変化させた場合でも、簡単な構成によって、発振ループ中の不要周波数信号成分を除去し、安定化した発振出力を得ることが可能なPLL発振回路を提供する。

【解決手段】PLL発振回路において、電圧制御発振器と位相比較器との間に不要周波数成分を除去するフィルタ回路を挿入するとともに、電圧制御発振器の制御電圧情報を記憶した制御電圧メモリの出力信号によって、上記フィルタ回路の通過周波数帯域を変更するように構成する。

(もっと読む)

低電力無線周波数分周器

本開示によれば、高周波数で動作するように構成されたマルチモジュール分周器(MMD)回路は、入力クロック信号を分周してパルス信号を生成するカスケードの複数の2又は3分周セルを含む。MMD回路はまた、パルス信号の期間を伸張し、出力クロック信号を出力するパルスストレッチング回路を含む。カスケードの2又は3分周セル及びパルスストレッチング回路は、フルスイングの相補型金属酸化物半導体(CMOS)回路を用いてインプリメントされるかもしれない。各2又は3分周セルは、2又は3分周セルのクリティカルパスが、第1のダイナミックフリップフロップと、第2のダイナミックフリップフロップと、第1のダイナミックフリップフロップと第2のダイナミックフリップフロップとの間の2よりも多くないロジックステージとを備えるようにオーガナイズされている。  (もっと読む)

(もっと読む)

半導体集積回路

【課題】入力された信号の位相と内部クロック信号の位相との差を所定の範囲内で吸収する能力を正確に試験することができる半導体集積回路を提供する。

【解決手段】半導体集積回路は、入力された信号の位相によって制御された位相を有する信号を生成する信号生成回路と、制御値を生成する制御値生成ブロックとを備えており、制御値生成ブロックが生成した制御値に応じて信号生成回路が生成する信号の位相を強制的にずらすことによって信号生成回路を試験する。ここで、制御値生成ブロックは、内部クロック信号に同期して動作するとともに、外部から、内部クロック信号よりも低い周波数を有する外部クロック信号に同期して目標値を受信し、受信した目標値に基づいて、内部クロック信号に同期して変化する制御値を生成する。

(もっと読む)

PLL回路

【課題】面積増大や消費電流増大を伴うことなくPLLロック時の位相オフセット量により生じるクロックの位相ばらつきを極力小さし、またロック後の温度や電源電圧変動へも対応できるようにする。

【解決手段】基準クロックCLK1と帰還クロックCLK2の位相を位相周波数比較器41で比較した結果に応じて出力クロックCLK3の周波数を決定するPLL回路において、出力クロックCLK3がクロックバッファ6を介して入力する分周回路5と分周回路5の出力クロックが入力し帰還クロックCLK2を出力する可変遅延回路9と、その帰還クロックCLK2の位相と基準クロックCLK1の位相を比較する位相比較器8とを備える。可変遅延回路9は、位相比較器8における基準クロックCLK1の位相と帰還クロックCLK2の位相の位相差がキャンセルされるようにその遅延量が制御され、結果としてPLL出力クロックCLK3の位相を調整できる。

(もっと読む)

121 - 140 / 367

[ Back to top ]