Fターム[5J106HH01]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 制御量 (1,632) | 周波数 (367)

Fターム[5J106HH01]に分類される特許

101 - 120 / 367

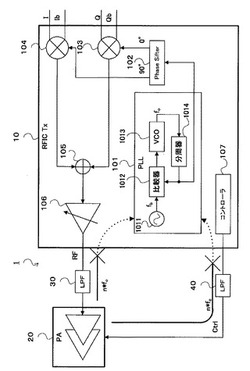

無線周波数集積回路

【課題】無線周波数集積回路において位相エラーを十分に低減する。

【解決手段】無線周波数集積回路は、与えられた電圧に応じた発振周波数の発振周波数信号を生成する電圧制御発振器を有し、発振周波数信号を分周して得られる搬送波に信号波を乗せた無線周波数信号を生成する送信部と、無線周波数回路からの前記無線周波数信号を増幅する電力増幅器と電力増幅器から送信部に回り込む、少なくとも前記発振周波数の同じ周波数の高調波成分を低減する低減手段と、

を有する。

(もっと読む)

シンセサイザと、これを用いたシンセサイザモジュール、受信装置、及び電子機器

【課題】位相雑音の劣化の少ないシンセサイザを提供すること。

【解決手段】シンセサイザ1の制御部7は、発振器5に電圧を出力するループフィルタ17の平滑回路に蓄積された電荷を予め設定された値に戻すことなく、温度を検出する温度検出部8の出力信号に基づいて分周器6の分周比を変化させる。これにより、シンセサイザ1は、温度変化に対応して制御部7が分周器6の制御を行う場合、ループフィルタ17の平滑回路に蓄積された電荷を予め設定された値に戻さないので、発振器5の発振周波数が大きく変動することを抑制し、これにより、シンセサイザ1における位相雑音を低減させることができる。

(もっと読む)

アキュムレータおよび位相デジタル変換器を使用する2ポイント変調のデジタル位相同期ループ

2ポイント変調をサポートするデジタル位相同期ループ(DPLL)が説明される。1つの設計において、DPLLは、位相デジタル変換器、ループ内で動作するループフィルタ、ローパス変調パスのための第1の処理ユニットおよびハイパス変調パスのための第2の処理ユニットを含む。第1の処理ユニットは、入力変調信号を受信し、位相デジタル変換器の後でループフィルタより前のループの内部の第1のポイントに対して第1の変調信号を供給する。第2の処理ユニットは、入力変調信号を受信し、ループフィルタより後のループの内部の第2のポイントに対して第2の変調信号を供給する。第1の処理ユニットは、周波数を位相に変換するために入力変調信号を累算するアキュムレータを含み得る。第2の処理ユニットは、可変利得で入力変調信号をスケールするスケーリングユニットを含み得る。 (もっと読む)

信号周波数変更回路及びその周波数変更方法

【課題】デューティサイクルエラーを最小化し、消費電流を減少させる。

【解決手段】信号周波数変更回路は、クロック信号を遅延制御信号に相応する第1遅延時間だけ遅らせて遅延信号を生成し、前記クロック信号を前記第1遅延時間に比べて小さい第2遅延時間だけ遅らせて予備周波数変更クロック信号を生成する遅延線;位相固定完了信号を生成する検出部;前記位相固定完了信号の活性化時点の以前まで供給される前記クロック信号を利用して、前記遅延制御信号及び多重化制御信号を順次シフトさせる制御部;前記多重化制御信号に応じて、前記予備周波数変更クロック信号のうちから1つを選択して出力するマルチプレクサ;及び前記クロック信号と前記マルチプレクサの出力信号を利用して、前記クロック信号の周波数と異なるように変更された周波数を有する周波数変更クロック信号を生成する出力部を備える。

(もっと読む)

量子周波数標準器及び時刻制御システム

【課題】簡素な回路構成で低消費電力の量子周波数標準器。

【解決手段】化学結合している原子核間のスピン−スピン相互作用によって複数に分裂したエネルギー準位を有する物質110を含む容器120と、容器120に磁場を与える磁場発生源MGと、容器120に電磁波を照射する発振器150と、を含む核磁気共鳴部100と、核磁気共鳴部100から出力される共鳴信号RSからエネルギー準位の核磁気共鳴周波数f1を検出し第1検出信号SD1として出力する第1検出部200と、共鳴信号RSから隣り合うエネルギー準位間のエネルギー差であるスピン結合定数Jを検出し第2検出信号SD2として出力する第2検出部300と、第1検出信号SD1と第2検出信号SD2に基づき核磁気共鳴部100を駆動する駆動信号DSを生成する駆動信号生成部400と、を含み、第2検出部300は、第2検出信号SD2に基づき標準周波数信号SOを出力する。

(もっと読む)

発振器

【課題】劣化が少なく目的とする周波数のクロックパルスを出力することのできる発振器を提供すること。

【解決手段】発振器1は、固定電極212と空隙を隔てて配置された可動電極214とを有する振動子21を用いた発振器であって、基準電圧を供給する基準電圧供給回路3と、

クロックパルスの入力によって作動する昇圧回路41を備え、基準電圧を所定の大きさの電圧に変換して出力する電圧調整回路4とを有し、前記振動子21は、電圧調整回路4から出力された前記所定の大きさの電圧が固定電極212と可動電極214との間に印加されるように構成されており、昇圧回路41に入力される前記クロックパルスは、振動子21を発信源として得られたものであることを特徴とする。

(もっと読む)

原子発振器

【課題】原子セルに入射するレーザー光の光量依存性を抑えた高精度の原子発振器を提供すること。

【解決手段】レーザー光源10から射出されるレーザー光の発光強度が変化しても、レーザー光源10と原子セル20との間に位置した透過光量可変手段40およびそれを制御する透過光量制御回路41によって原子セル20に入射するレーザー光の強度を一定にできる。したがって、基準発振周波数制御手段60によって、VCXO50の基準周波数をレーザー光検出器30で検出された射出光の強度に基づいて制御する際に、レーザー光の発光強度の変化に影響されることがなく、高精度な原子発振器100を得ることができる。

(もっと読む)

PLL回路

【課題】VCOのVT端子側から見えるバラクタダイオード数を減少させることによりリファレンスリークを低減するPLL回路を提供する。

【解決手段】PLL回路を構成するループフィルタから出力されるVCO制御電圧とVCOを予め関連付けて設定し、ループフィルタのVCO制御電圧に基づいて対応するVCOを選択し、該VCOの電圧制御発振器制御電圧端子とループフィルタの出力端子との接続を制御する切替信号を生成するVCO切替回路と、切替信号に基づいて、選択されたVCOのみの電圧制御発振器制御電圧端子とループフィルタの出力端子を接続し、他のVCOの電圧制御発振器制御電圧端子とループフィルタの出力端子との接続を解除するVT選択回路と、を備えるVCOの制御電圧端子にバラクタダイオードが接続された、発振周波数帯域の異なる複数のVCOを備えるPLL回路である。

(もっと読む)

半導体装置

【課題】リード動作時における位相調整精度を低下させることなく、DLL回路の消費電力を低減する。

【解決手段】ODT機能を有するデータ入出力回路80と、データ入出力回路80の動作タイミングを規定する内部クロックLCLKを生成するDLL回路100とを備える。DLL回路100は、内部クロックLCLKを高精度に位相制御する第1のモードと、低消費電力で動作する第2のモードとを有し、データ入出力回路80がODT動作を行っていない場合には第1のモードで動作し、データ入出力回路80がODT動作を行っている場合には第2のモードで動作する。このように、ODT動作の有無によってDLL回路100の動作モードを切り替えていることから、厳密な位相制御が不要なODT動作時における消費電力を低減することが可能となる。

(もっと読む)

自動調整発振器

【課題】チャージポンプを用いずに、出力周波数の精度を高くすることのできる自動調整発振器を提供する。

【解決手段】発振器10は、発振回路11、パルスカウンタ12、充電回路13、リセット回路14、調整回路15及びタイミング制御部を備えている。タイミング制御部から供給されたカウント開始信号に基づいてパルスカウンタ12は、発振回路11から出力される周波数f0のパルス信号をカウントし、この間、出力信号S1を充電回路13に供給する。充電回路13は、出力信号S1が供給されている間、定電流減PS1とコンデンサC1とを接続し、接続ノードND1の電圧V1を上昇させる。調整回路15は、出力信号S1の出力が終了した場合の電圧V1が、高電位基準電圧VHより高い場合には、周波数f0を高くする調整値を発振回路11に供給し、低電位基準電圧VLより低い場合には、周波数f0を低くする調整値を発振回路11に供給する。

(もっと読む)

PLL装置及びその制御方法

【課題】 基準入力期間に対して基準信号断期間が長期間継続しても、基準信号に同期して安定した信号を出力することが可能な、制御が容易で安価なPLL技術を提供する。

【解決手段】 基準発信源から入力される基準信号に対して所定の位相差を有する出力信号を生成するPLL装置は、前記基準信号と前記出力信号との位相を比較して、当該位相の位相差に対応する位相差信号を出力する比較手段と、基準となる位相差に対応する基準位相差信号を保持する保持手段と、前記位相差信号、又は、前記基準位相差信号を制御信号として選択する選択手段と、前記選択手段が選択した制御信号に応じた周波数の前記出力信号を発振して出力する発振手段と、を備え、前記選択手段は、前記基準発信源から前記基準信号が入力されている期間は前記位相差信号を選択し、前記基準発信源から前記基準信号が入力されていない期間は前記基準位相差信号を選択する。

(もっと読む)

発振回路、発振回路を持つ装置、および発振方法

【課題】局部発振周波数を制御する制御電圧を得る際に用いられる電源回路(DC/DCコンバータ)の内部発振周波数に起因する障害を回避する。

【解決手段】電源回路10と電圧制御発振器13と基準発振器15と電圧制御発振器の発振周波数f(VCO)を電圧制御する制御回路16を備える。電源回路10は内部発振器11の発振信号Voから所定電圧Vzを提供する。電圧制御発振器13は可変容量ダイオード14に印加される制御電圧Vcontによって発振周波数が変化する。制御回路16は、基準発振器15の発振周波数f(REF)に基づく比較周波数f(COMP)とf(VCO)に基づく検査周波数f(CHK)との比較結果によりVcontを制御する。Vcontは所定電圧Vzを用いて生成される。ここで、Nを自然数としたときに、内部発振器11の発振周波数f(DD)が比較周波数f(COMP)のN倍より高くN+1倍より低くなるようにする。

(もっと読む)

PLL回路、PLL回路無線通信機、及びPLL回路のロック検出方法

【課題】デジタル回路で構成出来、ロック検出のエラーやロストの発生を抑制することが出来ると共に、検出時間を短縮することが出来るPLL回路、無線通信機、及びロック検出方法を提供する。

【解決手段】ウィンドウ幅の異なる複数のロック検出部6b−1〜6b−nによる検出結果を用いて検出を行う。ロック判定部7は、複数のロック検出部6b−1〜6b−nによる検出結果に基づいて、ロック状態の検出を行う。

(もっと読む)

原子発振器

【課題】周波数基準を実現させると共に、光源駆動制御回路系を簡略化して装置を小型化

し、且つ安価な光源を利用することでコストを低減することができる原子発振器を提供す

る。

【解決手段】この原子発振器50は、アルカリ金属の一種であるCs原子の異なる遷移エ

ネルギーに対応する二種類の周波数の励起光対を発生させる光源1と、少なくとも気体状

のCs原子を封入したCsセル2と、光検出器3と、光検出器3により検出した光強度の

変化に応じてその出力値(電圧等)を制御する周波数制御手段4と、周波数制御手段4の

出力値によりその出力周波数を制御可能な基準発振源5と、基準発振源5の出力周波数を

光源1が発生する二種類の励起光対の周波数差の周波数に逓倍する逓倍手段6と、逓倍手

段6で発生した周波数差の二種類の励起光対を光源1から発生させる光源駆動電流の変調

手段7と、を備えて構成されている。

(もっと読む)

基準周波数制御回路

【課題】 基準周波数を生成する発振回路の発振周波数の変化を抑制可能な基準周波数制御回路を提供する。

【解決手段】 入力信号のレベルに応じた周波数で発振する発振回路からの発振信号が入力され、前記発振信号の周波数に応じた出力電圧を出力する周波数電圧変換回路と、前記出力電圧が所定レベルとなるよう前記入力信号のレベルを制御する制御回路と、を備えることを特徴とする基準周波数制御回路。

(もっと読む)

クロックリカバリ回路、及びそれを備えるクロックデータリカバリ回路

【課題】動作信頼性を向上させるクロックリカバリ回路、及びそれを備えるクロックデータリカバリ回路を提供すること。

【解決手段】受信信号を再生するタイミング情報が重畳された前記受信信号とリカバリクロックとの位相差に基づいて、前記受信信号とリファレンスクロックとの周波数オフセット情報を検知する周波数差検知部34と、前記周波数検知部34が検知した前記周波数オフセット情報に基づいて、前記受信信号と前記リカバリクロックとの位相差を補正する補正部30とを具備する。

(もっと読む)

リングオシレータ及びそれを用いたPLL回路

【課題】 リングオシレータで発生した高調波ノイズによる干渉を抑制できるリングオシレータ及びそのリングオシレータを備えたPLL回路を提供する。

【解決手段】 リングオシレータは、無線装置に内蔵され、複数段のインバータゲートからなる発振回路と、発振回路に接続された切り替えスイッチとを備える。発振回路が発生する高調波ノイズと無線装置の受信周波数とが干渉し、通信感度が低下する場合には、切り替えスイッチによりインバータゲートのリング状に接続される段数を切り替える。リングオシレータが発生する高調波ノイズの周波数を変えることで、無線装置の受信周波数との干渉を抑制する。

(もっと読む)

シンセサイザと、これを用いた受信装置及び電子機器

【課題】シンセサイザにおけるデジタル的な周波数制御に起因した位相雑音性能の悪化。

【解決手段】本発明のシンセサイザは、基準発振器から出力された基準発振信号が入力される比較器と、比較器の出力側に接続されたフィルタと、フィルタの出力側に接続されて発振信号を出力する発振器と、発振器の出力信号を制御部からの制御信号に基づいて分周する分周器とを備え、比較器は、分周器からの出力信号と基準発振器からの出力信号とを比較してこの比較結果を示す信号をフィルタに出力すると共に、制御部は、温度を検出する検出器の検出結果に基づいて分周器の分周比を時間間隔Tで制御し、時間間隔Tとフィルタのカットオフ周波数fcとの関係は、1/T≧fcを満たす構成である。

(もっと読む)

位相誤差検出装置、位相誤差検出方法、集積回路及び光ディスク装置

【課題】周波数誤差が生じているときでも±180度を越える位相誤差の検出を可能とし、PLLの安定性を向上させることができる位相誤差検出装置を提供する。

【解決手段】アナログ入力信号をサンプリングクロックに基づいてAD変換してデジタル再生信号を生成するAD変換部1の出力より位相誤差を検出する位相誤差検出装置は、AD変換部1の出力より前記位相誤差を生成する位相誤差生成部2と、位相誤差を補正する位相誤差補正部3とを含み、位相誤差補正部3は、過去の位相誤差により位相誤差検出範囲を決定し、位相誤差生成部2が生成した位相誤差が位相誤差検出範囲外であった場合に当該位相誤差を補正する。

(もっと読む)

原子発振器

【課題】ノイズに強く誤検出の可能性が極めて低い原子発振器を提供する。

【解決手段】各共鳴光を出射するコヒーレント光源1と、コヒーレント光源1の中心波長

を制御する中心波長可変手段4と、コヒーレント光源1の中心波長に変調を加えるサイド

バンド発生手段5と、コヒーレント光源1からの光の波長により光の吸収量を変化させる

ガスセル2と、ガスセル2から透過する光を検出する光検出手段3と、コヒーレント光源

1に変調がかかっていない状態で光検出手段3の出力を監視する吸収検出手段6と、光検

出手段3の出力を同期検波してEIT状態を検出するEIT検出手段7と、吸収検出手段

6により検出された光検出手段3の出力レベルに基づいて、中心波長可変手段4の中心波

長を設定し、EIT検出手段7により検出した周波数成分のレベルに基づいてサイドバン

ド発生手段5の出力周波数を制御する信号処理手段8と、を備えて構成されている。

(もっと読む)

101 - 120 / 367

[ Back to top ]