Fターム[5J106HH01]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 制御量 (1,632) | 周波数 (367)

Fターム[5J106HH01]に分類される特許

61 - 80 / 367

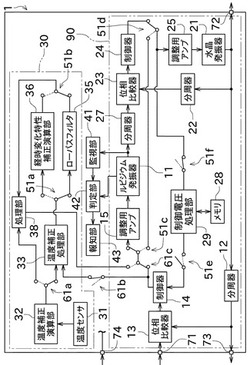

基準周波数発生装置

【課題】長時間にわたって基準周波数周波数の周波数安定度を維持可能で、かつ安価な基準周波数発生装置を提供する。

【解決手段】基準周波数発生装置1は、ルビジウム発振器11と、ルビジウム発振器11より周波数安定度が低い水晶発振器21と、判定部42と、切替スイッチ51a〜51fと、を備える。判定部42は、ルビジウム発振器11が正常な出力信号を出力している正常状態か、正常な出力信号を出力していない故障状態か、を判定する。切替スイッチ51c,51dは、ルビジウム発振器11が正常状態であると判定部42が判定しているときは、第1PLL回路を構成するように設定を行い、ルビジウム発振器11が故障状態であると判定部42が判定しているときは、第2PLL回路を構成するように設定を行う。

(もっと読む)

周波数ジェネレータ

【課題】 DDSを用いて高速スイープを可能にすると共に、周波数設定を容易に行うことができる周波数ジェネレータを提供する。

【解決手段】 スイープ制御部1が、スタート周波数やスイープ周波数ステップ設定値等の周波数設定値を入力して十進数の周波数設定データを出力し、周波数設定データ変換部2が、スイープ制御部1から入力された十進数に、動作周波数、DDS3への入力設定データのビット数、スイープ周波数のステップ設定値に基づく係数をスイープ制御部から入力される十進数の周波数設定データに乗算することで二進数に変換するbitデータ変換部21と、丸め処理を行う丸め処理部22とを備え、DDS3が、入力された二進数の周波数設定データに従って周波数信号を生成して出力する周波数ジェネレータである。

(もっと読む)

周波数−電流フィードバックを有する温度安定形発振回路

フェーズロックループや低周波温度安定形発振器を必要としない信号生成回路(600)および方法が開示される。この方法は、振動出力信号の周波数を制御するフィードバック信号(608)に応じて振動出力信号(CLK1〜CLKN)を生成することと、振動出力信号の周波数に対応する大きさを有する電流出力信号を生成することと、フィードバック信号を生成するために電流出力信号を基準信号(654)と比較することとを含んでよい。信号生成回路(600)は、フィードバック信号(608)に反応する発振回路(602)と、振動出力信号の周波数に対応する周波数依存性電流信号を生成する周波数−電流変換回路(620)とを含んでよい。発振回路へ向けてフィードバック信号(608)を生成するため、フィードバック変換回路(612)は出力信号を基準信号(654)と比較する。  (もっと読む)

(もっと読む)

同期装置および同期方法

【課題】同期源からの信号を捕捉できない状態になっても、可能な限り同期を維持することができる同期装置および同期方法を提供する。

【解決手段】選択部20は、内蔵GPSユニット2からの第1の基準信号およびGPSユニット3からの第2の基準信号のいずれかを選択する。PLL回路6は、選択部20で選択された基準信号に同期した同期信号を生成して内部の回路へ供給する。、内蔵GPSユニット2のホールドオーバー時間は、GPSユニット3のホールドオーバー時間よりも短い。選択部20は、GPSユニット3がホールドオーバー可能な状態となった後は、GPSユニット3を選択する。

(もっと読む)

信号処理装置

【課題】 外部からの基準信号の周波数変化が安定している状態であるかどうかをユーザが容易に判別可能とする。

【解決手段】 外部機器から供給された基準信号を入力する入力手段と、前記入力手段により入力された基準信号とクロックとの位相差を検出する位相検出手段と、前記位相検出手段の出力に応じた周波数の前記クロックを発生する発生手段と、前記位相検出手段の出力に基づいて前記入力手段により入力された基準信号の周波数と前記クロックの周波数との誤差を検出し、前記検出した誤差に基づいて前記基準信号の周波数変化の状態を示す情報を表示装置に表示する制御手段とを備える。

(もっと読む)

内部コマンド生成回路

【課題】電流消耗を減少させることができる内部コマンド生成回路を提供する。

【解決手段】本発明の内部コマンド生成回路は、読出しまたは書込み動作のためのコマンドを受信して、所定の周期で発生する複数のパルスを含む第1バーストパルスを生成するバーストパルス発生部と、前記第1バーストパルスをシフトして内部コマンドを生成するパルスシフト部と、を含み、前記内部コマンドは、バースト終了信号またはバーストコマンドのパルスが入力されるとディセーブルされる。

(もっと読む)

クロックデータリカバリ回路

【課題】ジッタに高速に追従可能なCDR回路を提供する。

【解決手段】フリップフロップFF1〜FF4はそれぞれ、入力データDINを対応するクロック信号CKのタイミングでラッチする。i(iは自然数)番目の第1論理ゲートG1iは、(2×i−1)番目のフリップフロップFFの出力と(2×i)番目のフリップフロップFFの出力とが不一致のときアサートされる内部アップ信号UPを生成する。j(jは自然数)番目の第2論理ゲートG2jは、(2×j)番目のフリップフロップFFの出力と(2×j+1)番目のフリップフロップFFの出力とが不一致のときアサートされる内部ダウン信号dnを生成する。第3論理ゲートG3は、複数の内部アップ信号up1〜up2にもとづきアップ信号UP_Aを生成する。第4論理ゲートG4は、複数の内部ダウン信号dn1、dn2にもとづきダウン信号DN_Aを生成する。

(もっと読む)

信号処理装置

【課題】 ジッタの少ないクロックを発生させる

【解決手段】 第1の発振器と、前記第1の発振器から出力される第1のクロックの周波数とは異なる周波数の第2のクロックを出力する第2の発振器と、前記第1の発振器からの第1のクロックと前記第2の発振器からの第2のクロックのうちの一方を選択する選択手段と、前記選択手段により選択された第1のクロックまたは第2のクロックの周波数を逓倍し、出力クロックを生成する生成手段と、前記第1の発振器からの第1のクロックを逓倍する逓倍回路と、前記逓倍回路からの出力信号と前記生成手段からの出力クロックとの位相差を検出し、前記位相差を示す信号を前記第2の発振器に出力することにより前記第2の発振器からの第2のクロックの周波数を変更する位相検出手段とを備える。

(もっと読む)

無線回路、集積回路装置及び電子機器

【課題】安定したデータ送信ができる無線回路、集積回路装置及び電子機器等を提供すること。

【解決手段】無線回路100は、電圧制御発振回路を有するPLL回路120を有し送信信号を生成して出力する送信信号生成回路110と、送信信号を増幅するパワーアンプ130と、周波数測定回路140とを含む。PLL回路120は、送信データ出力期間の前の期間ではクローズドループ動作に設定され、送信データ出力期間ではオープンループ動作に設定される。周波数測定回路140は、クローズドループ動作からオープンループ動作への切り換え時における送信信号の搬送波信号の周波数シフト量、及び送信データ出力期間における搬送波信号の周波数ドリフト量の少なくとも一方を測定する。

(もっと読む)

周波数シンセサイザ

【課題】設計が容易で、かつノイズ特性を良好にする。

【解決手段】周波数foutの出力信号Soutを生成するVCO5、周波数f1の低周波信号S1を生成する低周波信号生成部3、周波数f2の高周波信号S2を生成する高周波信号生成部4、ミキサ部6、ミキシング信号Smix中の差周波数信号Sdiを通過させる低域フィルタ部7、比較用信号S4を出力する信号処理部10、位相比較部8およびループフィルタ9を備え、信号処理部10は、周波数f2が新たに設定された際に、fout<f2のときには比較用信号S4の出力を停止し、fout≧f2で、かつ差周波数信号Sdiの絶対周波数fdiが低域フィルタ部7のカットオフ周波数fco以上のときには周波数f3(>f1)の基準信号S3を比較用信号S4として出力し、fout≧f2で、かつfdi<fcoのときには差周波数信号Sdiを比較用信号S4として出力する。

(もっと読む)

原子発振器及び原子発振器の制御方法

【課題】最大強度のEIT信号が検出でき、S/Nを向上して周波数の安定化を図ること

ができる原子発振器を提供する。

【解決手段】この原子発振器100は、アルカリ金属原子に電磁誘起透過現象(EIT現

象)を発生させるための共鳴光対を生成する光源1と、光源1からの光の波長により光の

吸収量を変化させるアルカリ金属入りセル2と、光源1に高周波信号を供給して共鳴光対

を生成するサイドバンド発生手段5と、光源1に直流信号を供給して共鳴光対の中心周波

数を可変する中心波長可変手段4と、アルカリ金属原子を透過した共鳴光対を検出し、透

過した共鳴光対の強度に応じた検出信号を出力する光検出手段3と、共鳴光対の中心周波

数を可変したときの検出信号の最小値を検出する吸収検出手段6と、サイドバンド発生手

段5から出力される高周波信号の供給又は停止を制御する信号処理手段8と、を備えて構

成されている。

(もっと読む)

量子干渉装置、原子発振器及び磁気センサー

【課題】アルカリ金属原子に対するEIT現象の発現効率を高めることにより、レーザーパワーの利用効率を向上させることができる量子干渉装置、原子発振器及び磁気センサーを提供すること。

【解決手段】光源10は周波数がΔωずつ異なる複数の第1,第2の共鳴光を発生させ、光検出手段40は磁場発生手段30により磁場が与えられたアルカリ金属原子を透過した第1,第2の共鳴光を含む光の強度を検出する。制御手段50は、光検出手段の検出結果に基づき、所定の1対の第1,第2の共鳴光の周波数差がアルカリ金属原子の2つの基底準位のエネルギー差に相当する周波数差に等しくなるように、かつ、アルカリ金属原子の2つの基底準位の各々に発生した、磁気量子数が互いに1だけ異なる2つのゼーマン分裂準位のエネルギー差に相当する周波数δに対して、2×δ×n=Δω及びΔω×n=2×δ(nは正の整数)の少なくとも一方を満足するように制御する。

(もっと読む)

同期伝送装置及びジッタ抑圧方法

【課題】同期伝送装置及びジッタ抑圧方法に関し、入力クロックとシステムクロックの周波数偏差のゼロ交叉点付近で発生するピークジッタを抑圧する。

【解決手段】入力クロックを自装置内のシステムクロックでリタイミングした基準クロックを生成するディジタル回路15_1と、基準クロックに同期した出力クロックを生成するPLL回路15_2と、入力クロックの周波数偏差とシステムクロックの周波数偏差との接近を検出する周波数偏差接近検出部1_1と、該周波数偏差の接近が検出されたとき、該周波数偏差の差が増大するよう、システムクロックの発振器1_3の発振周波数を調整する周波数調整部1_2を備える。

(もっと読む)

2分周インジェクションロックリング発振器回路

【解決手段】周波数分周器は、複数のインジェクションロックリング発振器(ILRO)を含む。第1ILROは、クロスカップルされたNチャネルトランジスタの対、負荷抵抗の対、インテグレイトキャパシタ、及び電流注入回路を含む。各トランジスタのドレインは、他方のトランジスタのゲートに結合される。各負荷抵抗は、各トランジスタのドレインを回路電圧源に結合する。インテグレイトキャパシタは、各トランジスタのソースに結合する。電流注入回路は、第1周波数の発振入力信号に応答して、各トランジスタのソースから回路グランドへのパスを交互にオープン及びクローズする。これに応答して、各トランジスタのドレインの電圧状態は交互にラッチ及びトグルされて、2分周された発振信号の差動対が生成される。逆位相で駆動される第1及び第2ILROは、位相直交する2つの差動出力信号を生成する。 (もっと読む)

PLL回路

【課題】拡散周波数が未知の拡散信号から拡散周波数成分を除去できるPLL回路を提供する。

【解決手段】一の信号の位相と他の信号の位相との差分に応じた差分信号を出力する位相比較器1、差分信号に応じた電流信号を生成するチャージポンプ回路2、電流信号を平滑化して信号n1を生成するループフィルタ9、信号n1をフィルタリングして信号n2、n5を生成するノッチフィルタ5、信号n1の位相と信号n2の位相との差分に基づいて、ノッチフィルタ5によって遮断される遮断周波数を調整する遮断周波数調整回路6、信号n5に基づいて所定の周波数の信号を発振する電圧制御発振回路3によってPLL回路を構成する。ノッチフィルタ5は、ループフィルタ9によって遮断される周波数よりも低い周波数の範囲に上限値と下限値が含まれる所定の範囲の周波数を遮断する。

(もっと読む)

クロック信号制御回路及びクロック信号制御方法

【課題】クロック信号の周波数制御をより好適に行うこと。

【解決手段】モニタ回路12のリングオシレータ16によるモニタ結果であるモニタ信号MSの周波数に応じて設定値記憶回路13からテーブル値TVALを出力させる。そして、そのテーブル値TVALに応じてクロック信号生成回路14のPLL回路15a,15bにより生成した発振信号と等しい周波数のクロック信号CLKを対象回路11に供給する。

(もっと読む)

位相ロックループ回路

【課題】ローカルクロック信号に同期し、入力クロック信号に基づく周波数の出力クロック信号を出力することができる位相ロックループ回路を提供することを課題とする。

【解決手段】ローカルクロック信号及び第1のクロック信号の位相を比較する第1の位相比較器(107)と、第1の位相比較器により出力される信号の電圧に応じた周波数の出力クロック信号を出力する電圧制御発振器(109)と、電圧制御発振器により出力される出力クロック信号を分周し、その分周した出力クロック信号を第1のクロック信号として第1の位相比較器に出力する第1の分周器(110)と、入力クロック信号及び電圧制御発振器により出力される出力クロック信号の位相を比較する第2の位相比較器(111)と、第2の位相比較器により出力される信号に応じて第1の分周器の分周比を制御する制御部(112,113)とを有する位相ロックループ回路が提供される。

(もっと読む)

送受信装置およびその動作方法

【課題】半導体チップ面積を低減して再生データと再生クロックの生成の誤動作の可能性を軽減する。

【解決手段】送受信装置7は、クロックデータリカバリ回路11、デシリアライザ15、シリアライザ14、PLL回路13、周波数検出器12を具備する。クロックデータリカバリ回路11は受信信号RXとPLL回路13から生成されるクロック信号TXCLKに応答して、再生クロックCLKと再生データDATAを抽出する。デシリアライザ15はCLKとDATAからパラレル受信データDTを生成し、シリアライザ14はパラレル送信データDRとTXCLKからシリアル送信信号TXを生成する。検出器12は受信信号RXとクロック信号TXCLKの周波数の差を検出して周波数制御信号FCSを生成して、信号FCSに応答して周波数の記差を低減するように、PLL回路13はTXCLKの周期を制御する。

(もっと読む)

受信部及び局側装置並びにクロック・データ再生回路における周波数校正方法

【課題】電圧制御型発振器を用いた受信部等において、温度補償用に容量素子を増やすことなく、温度変化による電圧制御型発振器の周波数特性を補償する。

【解決手段】本発明の受信部/局側装置は、受信信号からクロック信号及びデータ信号を再生するクロック・データ再生回路11を含むものであって、クロック・データ再生回路11に含まれる電圧制御型発振器17の発振周波数を校正する校正器16と、信号受信のスケジュールを管理する機能を有し、クロック信号及びデータ信号を再生すべき受信信号(上り信号)が無い状態の持続時間が校正器16による校正の所要時間を満たす時を選んで校正器16に対してリセット信号(校正指令信号)を出力する管理部104とを備えたものである。

(もっと読む)

クロックデータリカバリ回路及び表示装置

【課題】クロックデータリカバリにおいて擬似ロック発生の検出に要する時間を短縮すること。

【解決手段】クロックデータリカバリ回路は、レシーバ回路と、PLL回路と、擬似ロック検出回路とを備える。レシーバ回路は、所定のパターンを含むシリアルデータを受け取り、クロック信号に同期してシリアルデータをサンプリングしてサンプルドデータを生成する。PLL回路は、サンプルドデータに基づいてクロックデータリカバリを行い、クロック信号を生成する。ここで、擬似ロックパターンとは、PLL回路の擬似ロックが発生している場合にレシーバ回路が上記所定のパターンをサンプリングする結果得られるパターンである。擬似ロック検出回路は、サンプルドデータに含まれる擬似ロックパターンを検出することによって、PLL回路の擬似ロックを検出する。

(もっと読む)

61 - 80 / 367

[ Back to top ]