Fターム[5J106HH01]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 制御量 (1,632) | 周波数 (367)

Fターム[5J106HH01]に分類される特許

161 - 180 / 367

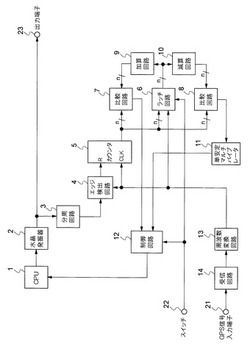

周波数補正回路及びそれを用いた無線通信装置

【課題】 発振器の出力周波数が増減した場合に自動補正を可能として常に出力周波数の精度を一定の範囲内に維持する周波数補正回路を得る。

【解決手段】 発振器2の発振周波数よりも高精度の基準周波数を、発振周波数を分周した分周周期毎に計数するカウンタ5と、発振周波数が正常な時のカウンタの計数値に相当する正常値に対して所定値Mを加算した値とカウンタの計数値とを比較して一致したときに発振周波数の減少を示す信号を生成する比較回路7と、正常値に対してMを減算した値とカウンタの計数値とを比較する比較回路8と、この比較回路8の一致結果に応答してこの一致結果を所定時間マスクするためのマスク信号を生成する単安定マルチバイブレータ11と、比較回路7の減少を示す信号に応じて発振周波数を減少方向に制御し、マスク信号の非生成時に発振周波数を増加方向に制御する制御回路12及びCPU1とを含む。

(もっと読む)

高分解能の時間/デジタル変換器

【解決手段】時間/デジタル変換器(TDC)は、インバータの伝播遅延よりも優れた分解能を有し得る。一例では、非整数遅延素子回路は、TDC入力信号を受信し、そこから、第1信号の時間シフトした複製である第2信号を生成する。第1信号は、第1遅延線タイムスタンプ回路(DLTC)に供給され、第2信号は第2DLTCに供給される。第1DLTCは、TDCへの参照入力信号のエッジと第1信号のエッジとの間の時間を示す第1タイムスタンプを生成する。第2DLTCは、参照入力信号のエッジと第2信号のエッジとの間の時間を示す第2タイムスタンプを生成する。第1及び第2タイムスタンプは合成されて、共に高い分解能の全体のTDCタイムスタンプを構成する。これは、第1または第2タイムスタンプよりも優れた分解能を有する。 (もっと読む)

クロック周波数安定化方法およびデータ受信装置

【課題】古い観測値を用いて再生クロックの周波数制御を行う場合に、制御が行き過ぎるのを抑制し、再生クロック周波数を安定化させる。

【解決手段】周波数安定化方法は、受信データをデータバッファに格納するステップと、データバッファに蓄積されているデータ量である蓄積データ量と、データバッファに蓄積されるデータ量の目標値との差である蓄積データ量と目標値との差分を算出するステップと、算出された差分に基づいて制御値を生成するステップと、現在の差分と以前の差分に基づいて前記制御値を補正するステップと、前記補正された制御値に基づいてクロック信号を出力するステップとを含んでいる。

(もっと読む)

シンセサイザと、これを用いた受信装置及び電子機器

【課題】周波数変動の大きな基準発振器を用いて、周波数変動を抑制した局部発振信号及び分周逓倍信号を出力するシンセサイザを小型に実現すること。

【解決手段】本発明のシンセサイザ2は、基準発振器3から出力された基準発振信号を基に局部発振信号を生成して周波数変換部5に入力するとともに、周波数補償部7から出力された周波数補償信号を基に局部発振信号の周波数補償を行うシンセサイザ2であって、局部発振信号を分周又は逓倍した分周逓倍信号を、周波数変換部5の出力側に接続された後段回路部6に入力する分周逓倍部2aを有する。この構成により、シンセサイザ2が周波数変動を補償した局部発振信号を出力するとともに、この局部発振信号を分周又は逓倍して分周逓倍信号を生成することにより、少なくとも1つのシンセサイザで、局部発振信号及び分周逓倍信号の周波数変動を補償することができる。

(もっと読む)

位相同期装置

【課題】本発明は、短いロッキングタイムを有しながらも、安定的に動作できる位相同期装置を提供する。

【解決手段】本発明の位相同期装置は、入力クロックを所定の分周比で分周した後、順次遅延させる動作により周波数を判別し、前記判別された周波数情報を用いて発振器ゲイン設定信号を生成する発振器ゲイン設定手段と、前記入力クロックに応じて、前記発振器ゲイン設定信号に対応する周波数を有する出力クロックを発振させるPLL回路を含むことを特徴とする。

(もっと読む)

発振周波数制御回路、その発振周波数制御回路を有するDC−DCコンバータ及び半導体装置

【課題】マイコン等の特別な制御回路が不要で、しかも無線送受信回路で使用する周波数に関係なく、スイッチングノイズの影響を無視できるレベルまでスイッチングノイズを軽減することができる発振周波数制御回路、その発振周波数制御回路を有するDC−DCコンバータ及び半導体装置を得る。

【解決手段】アップ/ダウン制御回路11は、第1クロック信号CLKAと第1分周クロック信号CLKB1との周波数を比較する第1周波数比較回路12と、第1クロック信号CLKAと第2分周クロック信号CLKB2との周波数を比較する第2周波数比較回路13の各出力信号UP及びDOWNに応じて、第2クロック信号CLKB2の周波数が所定の下限値から所定の上限値の間を連続的に変化しながら往復するように、発振回路2に対して、第2クロック信号CLKBの周波数制御を行うようにした。

(もっと読む)

デジタル位相ロックループを実施するためのシステム及び方法

【課題】デジタル位相ロックループを実施するシステム及び方法を提供する。

【解決手段】デジタル位相ロックループを実施する装置は、VCO制御電圧に応答して1次クロック信号を発生する電圧制御式発振器を含む。検出手段は、カウントアップ信号及びカウントダウン信号を含むカウンタ制御信号を発生し、1次クロック信号と基準信号の現在の関係を示す。アップ/ダウンカウンタは、次に対応するカウンタ制御信号に応答してカウンタ値を増分又は減分する。カウンタ値は、次に電圧制御式発振器により発生された1次クロック信号の周波数を調節するためにデジタル/アナログ変換器によってVCO制御電圧に変換される。代替実施形態では、上述のアップ/ダウンカウンタを利用して、デジタル/アナログ変換器でVCO制御電圧を発生する以外の適切な技術の利用により、カウンタ値に比例して電圧制御式発振器の周波数を調節することができる。

(もっと読む)

電圧制御装置およびクロック出力装置

【課題】電圧制御型水晶発振器(VCXO)から出力される信号の周波数をより高精度に制御することができる電圧制御装置20を提供する。

【解決手段】本発明の電圧制御装置20は、電圧制御型水晶発振器(VCXO)の温度毎の制御電圧値を、異なる条件下で予め2種類測定しておき、実際に温度補正を行う際には、現在のVCXOの温度に対応する制御電圧値を、それぞれの測定条件毎に1つずつ抽出し、抽出した制御電圧値を平均したものを現在の温度における制御電圧としてVCXOに供給する。

(もっと読む)

PLL回路

【課題】 高い線形性をもった電圧―電流特性を備え、ゲイン変動を抑えた電圧電流変換回路を有するPLL回路を提供する。

【解決手段】 電圧電流変換回路11は、制御電圧VCを受けるNチャネルMOSトランジスタN1と、NMOSトランジスタN1と直列に接続されたPチャネルMOSトランジスタP1と、PMOSトランジスタP1とミラー回路を構成するPMOSトランジスタP2と、PMOSトランジスタP1と並列に接続された電流源13を備える。PMOSトランジスタP2から出力される制御電流Ioutは、NMOSトランジスタN1に流れる電流から電流源13によって供給される電流の分だけ差し引かれる。

(もっと読む)

周波数制御回路およびCDR回路

【課題】調整のための外部接続端子を必要とする部品や外部接続部品を必要とする部品を不要にする。

【解決手段】CDR回路は、周波数制御回路と、制御電圧に応じて発振周波数が制御されかつ入力データにより発振位相が制御される再生クロックを生成する第1のVCO2と、再生クロックによって入力データのデータ識別を行うFF1と、制御電圧に応じて発振周波数が制御される第2のVCO3とを備える。周波数制御回路は、第2のVCO3の出力信号の周波数を参照クロックの周波数と比較し、検出した周波数差に応じた信号を出力する周波数比較器4と、周波数比較器4の出力信号に応じて出力するデジタル値を上下させるアップダウンカウンタ5と、アップダウンカウンタ5の出力をアナログ信号に変換してVCO2,3の制御電圧として出力するD/A変換器6とから構成される。

(もっと読む)

原子共振器を使用した周波数発生のためのデバイス、システム、および方法

固体原子クロックは、周波数標準を生成するために、超微細共振を示すことが可能な量子状態を利用する可能性がある。出力信号を生成するために自由走行発振器を超微細共振周波数に結合することが可能なデバイスが本明細書で述べられる。本発明のある態様では、原子クロックは、シリコン基材上で作製されてもよく、また、電子集積回路の一部として、チップスケールで集積化されてもよい。固体原子クロックを利用した動作原理、作製方法、およびシステムもまた開示される。 (もっと読む)

PLL回路、無線端末装置、および周波数検出方法

【課題】DCOの最低発振周波数を検出し、分周比Nに比例した制御データから、DCOの制御データへの変換を精度良く行うことが可能な、新規かつ改良されたPLL回路を提供すること。

【解決手段】ディジタル値を用いて制御される発振回路を有するPLL回路であって、搬送波周波数値を設定する搬送波周波数設定部と、搬送波周波数値が変化したことを検出する検出部と、搬送波周波数値が変化したことを示す信号に同期して、発振回路を最低周波数で発振させるための制御信号を送信し、基準周波数の1周期内の発振回路の出力クロック数を計測する計測部と、を含むことを特徴とする、PLL回路が提供される。

(もっと読む)

通信用半導体集積回路

【課題】周波数変調及び位相変調の高精度化を図ることが可能な通信用半導体集積回路を提供する。

【解決手段】通信用半導体集積回路は、ループフィルタの出力に第1の係数を乗算したキャリア周波数制御値を出力する第1の乗算器と、変調周波数データに第2の係数を乗算した変調周波数制御値を出力する第2の乗算器と、キャリア周波数制御値と変調周波数制御値とを加算し、その加算結果として前記発振器制御値を出力する第4の演算器と、を備える。第2の係数Kmは、Km=Kc+A×Fmod/Frefの関係にある(Kc:第1の係数、A:補正項(実数)、Fmod:前記変調周波数、Fref:前記基準周波数)。

(もっと読む)

PLL回路

【課題】PLL回路のロックアップ時間を短縮することである。

【解決手段】VCO選択回路15は、プログラマブル分周器14に設定される分周データに基づいて複数のVCOの内の1つを指定するVCO選択信号を出力する。また、VCO選択回路15は、VCOに与えられる周波数制御電圧と上限の基準値A及び下限の基準値Bを比較し、周波数制御電圧が基準値Aより大きいときには、発振周波数帯域が1つ上のVCOを選択する信号を出力し、基準値Bより小さいときには、1つ下のVCOを選択する信号を出力する。

(もっと読む)

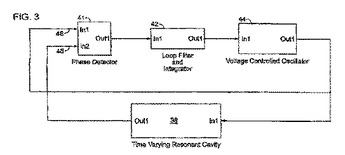

入力電圧の周波数に共振空胴の共振周波数を一致させる

シンクロサイクロトロンは、共振空胴を画定する磁気構造と、共振空胴に粒子を供給するイオン源と、共振空胴に高周波(RF)電圧を供給する電圧源と、RF電圧と時間とともに変化する共振空胴の共振周波数との間の位相差を検出する位相検出器と、この位相差に応答して、RF電圧の周波数が共振空胴の共振周波数と実質的に一致するように電圧源を制御する制御回路とを含む。電圧源が電圧制御発振器VCOを備え、フィードバック回路が、入力電圧の周波数と共振周波数との間の位相差を検出する位相検出器を備え、VCOが、位相差が所定値を逸脱したとき入力電圧の周波数を変化させるように構成される。  (もっと読む)

(もっと読む)

位相同期回路およびそれを用いた半導体集積回路装置

【課題】プロセスばらつき、環境変動によらず、所望の特性を満足する自動調整できる位相同期回路を提供すること。

【解決手段】位相同期回路は、位相周波数比較器1、チャージポンプ2、ループフィルタ3、分周器6、セレクタ7、電圧制御発振器8を備えている。分周器6は、出力信号と基準信号を入力して出力信号を分周して帰還信号を出力するとともに出力信号から選択信号とトリミング信号とリミット信号を出力する。電圧制御発振器8は、制御電圧と基準電圧とトリミング信号とリミット信号を入力して制御電圧に応じて出力信号周波数を変え、出力信号の上限周波数を制限できるとともに、トリミング信号によって制御電圧に対して出力する出力信号の周波数感度と、リミット信号によって出力信号の上限周波数を変えることができる。

(もっと読む)

注入同期型発振器

【課題】より小型化が可能な周波数逓倍器を提供する。

【解決手段】注入同期型発振器20は、インバータ(22a、22b、22c)を3段リング状に接続してリングオシレータを備えている。そして、2段目のインバータ22bの出力と、3段目のインバータ22cの出力とをnMOSトランジスタ24で接続する構成を採用している。このnMOSトランジスタ24のゲートは、外部から基準周波数信号が供給される。このような構成によって、、リングオシレータの自励発振周波数に近い周波数であって、注入された基準周波数信号と同期した整数倍の周波数で発振が行われる。このように、インジェクションロックを用いて、位相雑音を減らすことができるので、ループフィルタを必要とせず、より小面積で周波数逓倍器を構成することが可能である。

(もっと読む)

共振点追尾型駆動装置

【課題】 共振周波数を有する負荷の駆動中における該共振周波数の変動検知等を効率的にした共振点追尾型駆動装置を提供する。

【解決手段】 ステップS2及びS3において、共振周波数の変動検知動作開始前の駆動周波数(Fd)の位置より一定値の周波数だけ離れた2つの特定位置(周波数がFd+ΔFとFd−ΔFの位置)での負荷電流を計測し、それらをステップS5で比較して共振周波数の変動を検知し、その上で該変動に応じた追尾動作をするようにした。

(もっと読む)

データ受信装置およびマイクロコンピュータ

【課題】CR発振回路に温度変化や経年変化が生じても正確な周波数を持つクロック信号を生成する。

【解決手段】CR発振器12の温度を示すA/D変換値とCR発振回路8の逓倍数を決める逓倍数設定値FMULRとを対応付けてEEPROM3に記憶し、A/D変換値(検出温度T)に応じた逓倍数設定値FMULRを読み出してCR発振回路8のレジスタに設定する。通信回路7が同期信号を受信するごとにクロック信号CLKを計数して1ビット長を計測し、その計数値XAと正規の1ビット時間に対する基準周期に基づく基準計数値XBとに基づいて逓倍数設定値FMULRを補正し、補正後の逓倍数設定値FMULRを検出温度Tに対応させてEEPROM3に書き込む。

(もっと読む)

無線送信回路及びそれを用いた送受信機

【課題】 部品点数を削減でき、小型化に適した移動体通信機用の無線送信回路を提供する。

【解決手段】 従来の移動体通信機で必要とされていたTX,RF,IF周波数帯の3つの発振器のうちRF周波数帯PLLと、IF周波数帯PLLとを1つのPLLシンセサイザSSで兼用し、チップ内で大きな面積を専有する必要な発振器の個数を低減して部品点数を削減する。具体的には、RF周波数帯PLLのVCO21の出力を分周することにより、RF,IF周波数帯で用いる局部発振信号を生成する構成とする。

(もっと読む)

161 - 180 / 367

[ Back to top ]