Fターム[5J500AA48]の内容

Fターム[5J500AA48]に分類される特許

1 - 20 / 39

チャージアンプ

【課題】帰還抵抗の寄生容量による悪影響をなくして、半導体基板上で実用化が可能な、出力ノイズの小さいチャージアンプを提供する。

【課題の解決手段】チャージアンプ1は、非反転入力端子を増幅基準電圧6に接続し、反転入力端子に水晶振動子を有する振動型角速度センサ7から50KHzの周波数信号を入力するとともに、その出力端子は並列接続された帰還抵抗4,5及び帰還容量3を介して反転入力端子に接続したものであって、帰還抵抗4,5の反転入力端子側ほぼ半分に対応する寄生容量8の基板電極を反転入力端子に接続して、出力ノイズを低減したものである。

(もっと読む)

チャージアンプ

【課題】アナログスイッチとアナログスイッチ及びアナログスイッチと電荷信号を放電させるリセット回路とを備えることでオペアンプの入力端には流れこまないようにした、漏れ電流が信号に影響を与えないようにしたチャージアンプを提供する。

【解決手段】オペアンプ2の出力端子6とオペアンプ−入力端3に接続された積分コンデンサ7に、直列に接続したアナログスイッチS1とアナログスイッチS2を並列に接続し、更に前記アナログスイッチS1と前記アナログスイッチS2の接続点から接地点との間にアナログスイッチS3を接続し、前記積分コンデンサに充電した電荷信号を前記スイッチS1及びS2とで放電させるリセット回路とを備えたことを特徴とする圧電型センサの電荷信号を電圧信号に変換するチャージアンプにより提供される。

(もっと読む)

遅延制御回路、チャージポンプ回路、及びチャージポンプ回路における充放電電流制御方法

【課題】トランジスタがアンバランスであってもチャージポンプ回路に最適なバイアス電圧を与えられる遅延制御回路を提供する。

【解決手段】所定の信号を受けて電流入出力端子から充放電を行うチャージポンプ回路と、電流入出力端子の端子電圧に基づく電圧が電源として供給される遅延回路と、チャージポンプ回路の充放電電流の基準となるバイアス電圧を生成するバイアス生成回路と、を備え、チャージポンプ回路及び遅延回路が、それぞれ、第1導電型トランジスタと、第2導電型トランジスタを含んで構成され、バイアス生成回路が、第1導電型トランジスタの相互コンダクタンスと第2導電型トランジスタの相互コンダクタンスの和に基づいて、バイアス電圧を生成する。チャージポンプ回路の充放電により遅延回路の電源電圧を制御し、これにより遅延回路の遅延時間を制御する。

(もっと読む)

スイッチトキャパシタ積分および加算回路

【課題】単一の演算増幅器を使用して積分器と加算器の両方を実現するスイッチトキャパシタ回路を提供する。

【解決手段】1つの入力信号は、(1)1つまたは複数の積分ブランチと、(2)1つまたは複数の第1の加算ブランチとを介して演算増幅器の入力に送られる。第2の入力信号は、1つまたは複数の第2の加算ブランチを介して演算増幅器の入力に送られる。ブランチの各々は、キャパシタと、異なるクロック位相によって制御されるいくつかのスイッチとを含む。スイッチトキャパシタ回路はシングルエンドまたは差動とすることができる。

(もっと読む)

スイッチトキャパシタ回路

【課題】エスティメートフェーズとレベルシフトフェーズとで、レベルシフト用コンデンサCca、Ccbを、全差動演算増幅器AMP2の出力のサンプルと全差動演算増幅器のAMP2位相補償とに兼用する方式のCLS技術を適用したスイッチトキャパシタ回路100において、入出力コモン電圧の変動を抑止するこれにより、同相入力レンジの大きさに関する要求水準を低減させて、十分な低電圧化が図られて消費電力が低減されたスイッチトキャパシタ回路を実現する。

【解決手段】エスティメートフェーズからレベルシフトフェーズへの移行に際して、複数の全差動演算増幅器AMP1、AMP2のうちの初段の全差動演算増幅器および最後段の全差動演算増幅器の各出力コモン電圧が等しくなるように保持する出力コモン電圧保持回路110を備えた。

(もっと読む)

電荷検出回路

【課題】差動増幅回路の入力側のゲイン調整を容易に行うことができる電荷検出回路を提供する。

【解決手段】電荷発生型センサ及び容量変化型センサの何れかで構成される物理量検出センサ1A,1Bの一端が差動増幅回路1の負極入力端子に接続され、他端が前記差動増幅回路1の正極入力端子に接続され、前記差動増幅回路1の出力端子と前記負極入力端子との間にフィードバック抵抗Rf及びフィードバック容量Cfが並列に接続され、且つ前記差動増幅回路1の正極入力端子と基準電圧との間にキャンセル抵抗Rc及びキャンセル容量Ccが並列に接続された差動型の電荷検出回路であって、前記差動増幅回路1の正負の差動入力が個別入力される2つの電界効果トランジスタFET1,FET2の少なくとも一方のドレイン電圧を調整するドレイン電圧調整回路12,13を設け、前記正負の差動入力の少なくとも一方のゲイン調整を可能とした。

(もっと読む)

電荷電圧変換回路、検出装置及び電子機器

【課題】電荷電圧変換後の電圧信号のS/Nを向上する電荷電圧変換回路、検出装置及び電子機器等を提供すること。

【解決手段】電荷電圧変換回路は、キャパシターC1と、差動電流信号を構成する第1の信号ISPが供給される第1の入力ノードNI1と、キャパシターC1の一端側のノードである第1のノードN1との間に設けられる第1の入力用スイッチ素子NI1と、差動電流信号を構成する第2の信号ISMが供給される第2の入力ノードNI2と、第1のノードN1との間に設けられる第2の入力用スイッチ素子NI2と、キャパシターC1に蓄積された電荷に対応する電圧信号を出力するための出力用スイッチ素子SQ1と、を含む。

(もっと読む)

スイッチドキャパシタ増幅回路、パイプライン型AD変換器、および信号処理システム

【課題】精度および高速性能を損なうことなくアンプシェア動作を実現可能なスイッチドキャパシタ増幅回路、パイプライン型AD変換器、および信号処理システムを提供する。

【解決手段】複数のスイッチドキャパシタ回路210,220で共有される演算増幅器AMP11を有し、複数のスイッチドキャパシタ回路は演算増幅器の入力および出力と切り離すように複数のスイッチが制御されて複数の容量で第1のアナログ信号をサンプリングするサンプルモードと、サンプリングした容量を演算増幅器の入力および出力と選択的に接続するように複数のスイッチが制御されて、演算増幅器のサンプルモードでサンプリングした信号と第2のアナログ信号との差分を2N倍に増幅するホールドモードとが相補的に設定され、サンプルモード時に演算増幅器の入力および演算増幅器の内部における電圧が固定されていないノードを共通電位にリセットするスイッチswrを有する。

(もっと読む)

バイアス回路及びそれを有する増幅回路

【課題】

クロックによるノイズの影響を抑制したバイアス回路と,それを利用した増幅回路を提供する。

【解決手段】

バイアス回路は,トランジスタと可変抵抗を有し,トランジスタに電源電圧に依存せず前記可変抵抗に反比例したトランスコンダクタンスを発生させるバイアスユニットと,バイアスユニットが生成するバイアス電流をカレントミラーする第1の電流源と,第1の容量と,第2の容量と,第1の容量に第1の電流源の電流を充電する第1のスイッチと,第1の容量の電荷を前記第2の容量に転送する第2のスイッチとを有し,第2の容量に参照電圧を生成する参照電圧生成回路と,可変抵抗の電圧を参照電圧に一致させるように可変抵抗の抵抗値を制御する制御信号を出力する制御回路とを有する。

(もっと読む)

電荷信号をデジタル信号に変換するためのデジタル電荷増幅器および方法

本発明は、圧電測定素子によって出力された正および負の電荷信号Qを測定素子における現在の測定値に比例するデジタル信号Dに変換するための電荷増幅器回路に関する。回路は、検出された電荷Qを電圧U2に変換するための電荷入力および電圧出力を有する電荷増幅器V1を含み、2つの出力を有する補償回路Kが電荷増幅器V1の電圧出力の下流に接続されており、第1の出力は、電荷増幅器V1の電荷入力につながれ、第2の出力は、2つの入力Z+およびZ−を有するカウンタZに接続されている。一方で補償回路Kは、電圧U2に比例する補償電荷Qk+またはQk−を生成することができ、それは、第1の出力によって電荷増幅器V1の電荷入力へ送られて入力信号Qを補償することができ、また他方で補償回路は、生成された各々の補償電荷Qk+またはQk−の大きさに比例する複数のパルスP+、P1を生成することができる。前記パルスは、第2の出力によって補償電荷Qk+またはQk−と逆符号のカウンタZの入力Z−、Z+へ送ることができ、それまでに入力された電荷量子の和に比例する所望のデジタル信号DがカウンタZの出力に得られる。本発明は、さらにそのような回路上で実行される方法に関する。  (もっと読む)

(もっと読む)

電荷を電圧に変換するシステムおよびこのシステムを制御する方法

【課題】最終変換利得を低減させることなく、変換デバイスを制御する方法を提供する。

【解決手段】本発明は、増幅器と、増幅器の入力と出力の間に負帰還で取り付けられた少なくとも1つのキャパシタとを含み、それによって前記増幅器を、前記増幅器から電荷を受け取る少なくとも1つの入力段と前記増幅器へ電圧を送る少なくとも1つの出力段との間に接続でき、前記電圧が、入力で受け取った電荷を表す、電荷を電圧に変換するデバイスを制御する方法であって、前記方法が、入力で受け取った電荷の電圧変換を含む少なくとも1つの段階(62)を含む、方法に関する。本発明によれば、変換段階は少なくとも、増幅器が入力段に接続され、また増幅器が出力段から切断される、1つの第1の副段階(64)と、増幅器が入力段から切断され、また増幅器が出力段に接続される、その後の第2の副段階(66)とを含む。

(もっと読む)

出力回路

【課題】占有面積が小さい出力回路を提供する。

【解決手段】出力回路20は、制御部21、X軸増幅部31、Y軸増幅部32、Z軸増幅部33、第1共用回路CC1、第2共用回路CC2を含んで構成される。制御部21は、センサ出力の温度依存性を補正するための温度係数オフセットを出力する。第1共用回路CC1、第2共用回路CC2は、加速度センサ10からの出力を、軸毎に増幅する場合に利用される。リセットフェーズにおいては、第1、第2共用回路の容量に蓄積された電荷を放出する。増幅フェーズにおいては、第1、第2共用回路及びオペアンプにより、各軸の温度係数オフセット電圧を用いて加速度センサからの信号を較正し、増幅する。ホールドフェーズにおいては、蓄積された電荷を容量にそのまま維持させることにより、各軸の出力値を保持する。

(もっと読む)

容量−電圧インタフェース回路及び関連する動作方法

容量式感知セル402の動作に関連し得る検出される差の容量に相当する電圧を取得するために容量−電圧インタフェース回路400が用いられる。インタフェース回路400は、容量式感知セル402、容量式感知セル402に選択的に接続するように適合されている演算増幅器408、演算増幅器408用のフィードバックキャパシタ412,414、演算増幅器408用の負荷キャパシタ416,418、及び容量式感知セル402、演算増幅器408、フィードバックキャパシタ412,414、及び負荷キャパシタ416,418に関連する、スイッチングアーキテクチャ108を含む。使用中、スイッチングアーキテクチャ108は、容量−電圧インタフェース回路400を複数の様々なフェーズにおける動作のために再構成する。様々な動作フェーズによって、単一の演算増幅器408が容量−電圧変換及び電圧増幅の両方のために使用されることが可能となる。  (もっと読む)

(もっと読む)

チャージアンプ回路

【課題】 入力側にリーク電流が存在した場合であっても正確な出力を得ることが可能なチャージアンプ回路を提供する。

【解決手段】 積分回路101と増幅回路102との間に直流遮断容量103を設け、不要な直流成分であるリーク電流を遮断すると共に、直流遮断容量103の出力端にバイアス抵抗201を介して定電圧発生回路108を接続し、バイアス電圧を印加することで、増幅回路102の入力信号に増幅回路102で必要とされる適切な直流電圧レベルを与える。

(もっと読む)

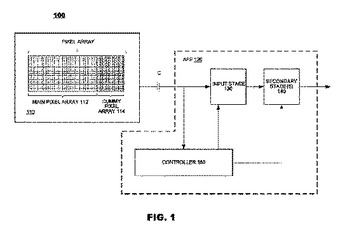

画像フロントエンド用のスイッチ式キャパシタ入力段

本発明の実施形態は、DC復元動作を制御するアナログフロントエンド(AFE)増幅器用の装置および制御方法を提供する。例示的な方法によると、AFEの第1の入力段が、高入力インピーダンスを有し、画像センサ画像アレイの第1の所定の領域における入力漏れ電流をほぼ引き出さない、連続時間増幅として動作するように制御される。第1の入力段は、画像センサ画像アレイの第2の所定の領域におけるDC復元機能を有するサンプルホールド増幅器として動作するように制御される。一実施形態によると、AFE入力段は、センサの作動状態画像アレイからの画素を読み出すとき、連続時間増幅として動作するが、いわゆる「黒レベル」画素に対応する画像アレイからの画素、または別途センサの作動状態画像フィールドの外部にある画素を読み出すときは、DC復元を有するサンプルホールド増幅器として動作する。  (もっと読む)

(もっと読む)

コンパレータベース/ゼロクロスベーススイッチドキャパシタ回路において非直線性を除去すると共にオフセット誤差をキャンセルするためのシステム及び方法

【課題】オフセット誤差を低減する。

【解決手段】方法は、コンパレータベース/ゼロクロスベース回路の出力信号における誤差を補償する。該方法は、コンパレータベース/ゼロクロスベーススイッチドキャパシタ回路によって、入力信号を用いて第1の出力信号を生成すること、コンパレータベース/ゼロクロスベーススイッチドキャパシタ回路によって、逆極性の入力信号を用いて第2の出力信号を生成すること、及び第2の出力信号を第1の出力信号から減算することであって、コンパレータベース/ゼロクロスベーススイッチドキャパシタ回路に関する最終出力信号を生成する、減算することを含む。

(もっと読む)

差動増幅回路

【課題】動作速度を低下させることなく安定した動作を行うことができる、スイッチトキャパシタ回路を使用した差動増幅回路を得る。

【解決手段】ゲインが比較的高いときには、スイッチSW11及びSW12をそれぞれオフさせて遮断状態にすると共に、第2差動増幅器3をパワーダウンさせて第1差動増幅器2だけが作動するようにし、ゲインが比較的低いときには、スイッチSW11及びSW12をそれぞれオンさせて導通状態にすると共に、第1差動増幅器2だけでなく第2差動増幅器3も作動させるようにした。

(もっと読む)

ピークホールド回路

【課題】 入力信号が高速な場合など、オペアンプの出力電圧レベルが不足の場合にも、ピーク電圧を出力できるピークホールド回路を得ること。

【解決手段】 入力コンパレータ、ホールドコンデンサ、充電電流制御端子を有し前記ホールドコンデンサに充電電流を供給する充電電流回路、放電回路を備えたピークホールド回路において、前記入力コンパレータを入力信号の電圧と前記ホールドコンデンサの保持電圧を比較するオペアンプで構成し、前記オペアンプの出力端子と前記充電電流回路の充電電流制御端子との間にレベルシフタを備えた。

(もっと読む)

電荷を電圧に変換するシステムおよびこのシステムを制御する方法

本発明は、増幅器と、増幅器の入力と出力の間に負帰還で取り付けられた少なくとも1つのキャパシタとを含み、それによって前記増幅器を、前記増幅器から電荷を受け取る少なくとも1つの入力段と前記増幅器へ電圧を送る少なくとも1つの出力段との間に接続でき、前記電圧が、入力で受け取った電荷を表す、電荷を電圧に変換するデバイスを制御する方法であって、前記方法が、入力で受け取った電荷の電圧変換を含む少なくとも1つの段階(62)を含む、方法に関する。本発明によれば、変換段階は少なくとも、増幅器が入力段に接続され、また増幅器が出力段から切断される、1つの第1の副段階(64)と、増幅器が入力段から切断され、また増幅器が出力段に接続される、その後の第2の副段階(66)とを含む。  (もっと読む)

(もっと読む)

クーロンカウンタ、そのダイナミックレンジ可変方法

【課題】回路規模を縮小し、測定電流のダイナミックレンジ及び電流分解能を可変にして最適化を図り、誤差の少ないカウント値を出力可能なクーロンカウンタを提供する。

【解決手段】センス抵抗両端に生じる電位差の入力電圧に比例したカウント値を出力するクーロンカウンタであって、そのIC部50は、基準電圧発生回路30からの電圧値可変で設定された基準電圧の印加、スイッチ素子の操作により、入力電圧をサンプリング容量Cs1、Cs2でサンプリングし、それに比例する電圧を積分容量Ci1、Ci2で積分する積分回路と、積分回路からの出力電圧Vout−をVCMと比較して、Vout−がVCM以上では信号Q、VCMよりも低い場合は信号QBを出力するコンパレータ5と、信号Q、QBとを一定時間カウントしてカウント値を出力する内部カウンタ、カウント値に含まれるオフセット値を保持するレジスタを含むロジック回路10と、を備える。

(もっと読む)

1 - 20 / 39

[ Back to top ]