Fターム[5J500AA53]の内容

増幅器一般 (93,357) | 増幅器の種類 (14,578) | 切換え構成を有する増幅器 (476) | 入力(出力)信号切換型増幅器 (61)

Fターム[5J500AA53]に分類される特許

1 - 20 / 61

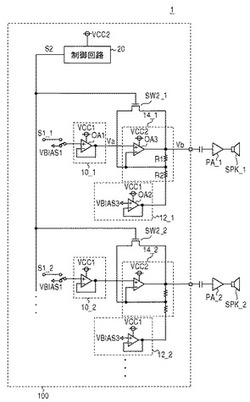

オーディオ信号処理回路およびそれを用いた電子機器

【課題】オーディオ信号処理回路100のノイズを抑制する。

【解決手段】非反転アンプ14は、第3演算増幅器OA3および分圧回路R1、R2を含み、第1バッファ10の出力電圧を非反転増幅する。スイッチSW2は、第3演算増幅器OA3の出力端子とその反転入力端子の間に設けられる。制御回路20は、第2電源電圧VCC2が所定のしきい値電圧より低いときにスイッチSW2をオンし、第2電源電圧VCC2がしきい値電圧より高いときにスイッチSW2をオフする。

(もっと読む)

F級増幅回路及びこれを用いた送信装置

【課題】基本波周波数の異なる複数の入力信号が入力する場合でも、各基本周波数に応じた高周波処理が行えるようにする。

【解決手段】 基本角周波数の異なる複数の信号をF級増幅し、該基本角周波数の信号成分及び、その高調波の信号成分を含んだ信号を出力するF級増幅器と、F級増幅器の後段に設けられて、当該F級増幅器に寄生する寄生回路のインピーダンスを取り込んで回路設定されることにより、信号の直流成分及び偶数次高調波の信号成分に対しては短絡状態とし、奇数次高調波の信号成分に対しては開放状態となる高調波処理部と、高調波処理部の後段に設けられて、高調波の信号成分に対しては短絡状態にする短絡部と、を備える。

(もっと読む)

増幅器

【課題】増幅器の出力雑音電圧を抑制する。

【解決手段】正転入力電圧と反転入力電圧の差分を増幅する差動入力回路1と、差動入力回路1の出力信号を増幅して出力端子に出力する出力回路2と、差動入力回路1の電流源MP3と出力回路2の電流源MP4にバイアス電圧を出力するバイアス回路5を備えた増幅器である。差動入力回路1の正転入力電圧と反転入力電圧が共に接地電圧のときに出力端子に現れる出力雑音電圧を検出し、該雑音電圧のレベルが高いほど、バイアス回路5が、電流源MP3,MP4の電流を増大させるバイアス電圧を出力するようにした。

(もっと読む)

増幅器、送信装置および増幅器制御方法

【課題】使用環境の変動により発生する電力効率の劣化を抑制すること。

【解決手段】増幅器は、エンベロープ検出部と、比較部と、選択部と、電圧制御部と、電流測定部と、基準電圧制御部とを備える。エンベロープ検出部は、送信信号のエンベロープを検出する。比較部は、エンベロープの電圧と基準電圧とを比較する。選択部は、比較部による比較結果に基づいて、動作電力が異なる複数の増幅素子から送信信号を増幅する増幅素子を選択する。電圧制御部は、選択部により選択された増幅素子における送信信号の増幅に用いる電圧をエンベロープに基づいて制御する。電流測定部は、電圧制御部により制御される電圧を供給する電源の電流を測定する。基準電圧制御部は、電流測定部により測定される電流が減少するように基準電圧を制御する。

(もっと読む)

高周波回路

【課題】 平衡型増幅器を用いて構成され、挿入損失の増大を抑え、回路の大型化を防ぎながらアンテナダイバシティが利用可能な電気的特性に優れた高周波回路を提供する。

【解決手段】

平衡型増幅器とスイッチ回路を備えた高周波回路であって、前記平衡型増幅器は複数の入力ポートと異なるアンテナと接続される複数の出力ポートを有し、各入力ポート及び各出力ポートとグランドとの間に、スイッチ素子と抵抗とを備えた終端回路を有する。

(もっと読む)

集積回路装置及び電子機器

【課題】センサーデバイスのチャネル信号が第1、第2信号で構成される場合に第1、第2信号の差分に対応する信号の精度の高いA/D変換を実現する集積回路装置等の提供。

【解決手段】集積回路装置は、センサーデバイスからの第1信号SG1が第1期間において入力され、第1信号SG1とペアーとなってセンサーデバイスのチャネル信号を構成する第2信号SG2が第2期間において入力され、第1信号SG1と第2信号SG2の差分に対応する信号を出力する増幅回路と、増幅回路の出力信号についてのA/D変換を行うA/D変換器を含む。増幅回路は、増幅回路が有する演算増幅器のオフセット電圧をキャンセルするスイッチドキャパシター回路により構成される。

(もっと読む)

アナログ入力モジュール保護装置

【課題】アナログ入力モジュールを過電圧から保護すること。

【達成手段】本発明の保護装置は、複数のプラス/マイナスアナログ信号の電圧レベルがアナログ入力モジュールのプラス/マイナス動作電圧よりも大きい場合、前記複数のプラス/マイナスアナログ信号の電圧を前記アナログ入力モジュールに供給する安定化部を含む。

(もっと読む)

ローカル周波数信号切替回路

【課題】複数のバンドグループの周波数を周波数ホッピングする無線通信システムにおいて、低消費電力なローカル周波数切替回路を提供する。

【解決手段】それぞれ異なる周波数のローカル周波数信号がゲートに接続されソースが電流源に接続された複数の入力トランジスタと、複数の入力トランジスタに対して共通に設けられた出力端子と、出力端子に接続された負荷回路と、を備え、複数の入力トランジスタのドレインと出力端子は、それぞれ、周波数バンドグループを選択する第1のスイッチトランジスタと、選択された前記バンドグループの中で周波数ホッピングをする周波数を選択する第2のスイッチトランジスタと、を介して接続され、複数の入力トランジスタにそれぞれ入力されたローカル周波数信号のうち、第1及び第2のスイッチトランジスタにより選択されたローカル周波数信号を出力端子から出力するように構成されている。

(もっと読む)

送受信モジュール

【課題】大きなパルス幅を有する大電力の高周波信号が入力された場合であっても、リミタ回路および受信回路の増幅器が破壊されることを抑制することができる送受信モジュールを提供する。

【解決手段】アンテナ11と、リミタ回路16および受信系電力増幅器17を備えた受信回路14と、送信系電力増幅器20を備えた送信回路15とが、送受信切替スイッチ13により接続され、アンテナ11と送受信切替スイッチ13の間に設けられた検波回路12により、送受信切替スイッチ13を制御する制御信号を生成する。送受信切替スイッチ13は、制御信号が入力されない状態ではアンテナ11と受信回路14とを導通させ、制御信号が入力されるとアンテナ11と送信回路15とを導通させる。制御信号は、送受信切替スイッチ13に信号が入力された時から、リミタ回路16の熱時定数よりも短い時間までの間に送受信切替スイッチ13に入力される。

(もっと読む)

増幅器、信号処理システム、および光ディスク装置

【課題】複数の入力パスの信号処理機能共有化を実現し、実用上求められる過渡応答の収束性を高めることが可能な増幅器、信号処理システムおよび光ディスク装置を提供する。

【解決手段】演算増幅器141と、演算増幅器の出力端子から第1の入力端子または第2の入力端子への帰還経路を含み、ゲイン制御信号に応じてゲインを調整可能なゲイン調整系142と、演算増幅器の第2の入力端子または第1の入力端子に接続された可変基準電圧源143と、演算増幅器の出力端子と制御端子間に接続され、位相補償制御信号に応じて位相補償量を調整可能な位相補償系144と、ゲインおよび位相補償量をゲイン制御信号および位相補償制御信号により制御する制御系と、を有し、演算増幅器の第1の入力端子に複数の入力要素が時分割的に入力され、制御系は入力される入力要素ごとにゲインの切り替え調整に合わせて、位相補償量を切り替えるように制御する。

(もっと読む)

初段増幅回路およびそれを用いた電子機器

【課題】初段増幅回路の回路面積の削減にある。

【解決手段】入力端子Piには外部からのオーディオ信号S2が入力される。第1抵抗R1は、その第1端子が入力端子Piと接続される。第2抵抗R2の第1端子は、第1抵抗R1の第2端子と接続される。演算増幅器10の反転入力端子(−)は第2抵抗R2の第2端子と接続され、その非反転入力端子(+)には基準電圧Vrefが印加される。第3抵抗R3は、演算増幅器10の出力端子とその反転入力端子(−)の間に設けられる。第1ダイオードD1は、第1抵抗R1の第2端子と電源端子Vddの間に、カソードが電源端子Vdd側となる向きで設けられる。また第2ダイオードD2は、第1抵抗R1の第2端子と接地端子Vgndの間に、カソードが第1抵抗R1の第2端子側となる向きで設けられる。

(もっと読む)

増幅器および通信装置

【課題】利得の変化を抑制しつつ、複数の周波数帯域で良好に動作するようにチューニングすることが可能な増幅器を提供する。

【解決手段】入力信号がゲートに入力される電界効果トランジスタM1と、電界効果トランジスタM1のゲートとソースの間に接続された可変キャパシタCgsと、電界効果トランジスタM1のソースに接続された可変インダクタLsを設ける。

(もっと読む)

高速多重化回路

【課題】高速動作時の出力波形品質を改善する。

【解決手段】高速多重化回路は、データ信号列(D1P,D1N),(D2P,D2N)毎に設けられ、入力されたデータ信号列を共通に接続された信号出力端子に選択的に出力する第1のトランジスタQ1P,Q1N,Q2P,Q2Nと、トランジスタQ1P,Q1Nから構成される差動対またはトランジスタQ2P,Q2Nから構成される差動対のいずれか一方をクロック信号CK1,CK2に応じてオンにする第2のトランジスタQ3,Q4と、トランジスタQ1P,Q1N,Q2P,Q2N,Q3,Q4にコレクタ電流を流す電流源となる第3のトランジスタQ6,Q7と、第3のトランジスタQ6,Q7のコレクタとエミッタ側の電源電圧VEEとの間に挿入されたコンデンサC1とを備える。

(もっと読む)

検出回路

【課題】アンプ(増幅器)に接続されたスピーカのインピーダンスが小さい場合、スピーカを駆動するアンプが発熱する。

【解決手段】

アンプ(増幅器)の出力端子に接続された検出回路において、アンプと、アンプからの出力信号の電流値を検出する電流検出回路と、アンプからの出力信号の電圧値を検出する電圧検出回路と、判定回路と、を有し、判定回路は、電流検出回路と電圧検出回路からの検出結果に応じて、アンプの動作を停止することとする。上記の構成により、接続されるスピーカのインピーダンスが規定より大きい場合には、アンプの動作を停止せず、アンプの能力の上限まで、動作を許可する。逆に接続されるスピーカのインピーダンスが規定より小さい場合には、発熱によるアンプが破損、発火の防止を優先する。

(もっと読む)

無線通信装置及び近距離無線通信回路の通信モード切り替え方法

【課題】相対的に通信可能距離が遠距離であり狭帯域を占有する通信モード(通常モード)と、通信可能距離が近距離であり広帯域を占有する通信モード(近接モード)との切り替えを可能とするとともに、広帯域を占有する近接モードでの利得周波数特性の劣化を抑制する。

【解決手段】通常モードから近接モードに切り替える場合に、バイパス路1005は、増幅回路1003及び1004を迂回する。さらに、インピーダンス素子1013は、近接モードに切り替える場合に信号経路上に接続され、バイパス路1005による増幅回路1003及び1004の迂回の有無によるリアクタンスの変化を補償する。

(もっと読む)

低雑音増幅回路

【課題】 低雑音で 100n秒以下の起動および停止による高速な間欠動作を可能とする。

【解決手段】 入力端子からトランジスタのゲートに容量を介して信号、第1の抵抗を介してバイアス電圧を入力し、ドレインから増幅した信号を出力する第1の増幅器と、第1の増幅器の出力信号を容量を介して差動接続された一方のトランジスタのゲートに、第2の抵抗を介して差動接続された他方のトランジスタのゲートに入力し、各ドレインから増幅した差動信号を出力する第2の増幅器と、第1および第2の増幅器と電源との間の接続状態を第1の制御信号に応じてオンオフし、第1および第2の増幅器の動作状態および休止状態を制御する間欠動作制御手段とを備えたLNAにおいて、動作状態から休止状態へ遷移するとき、または休止状態から動作状態に遷移するときに、第1および第2の抵抗の抵抗値を所定時間だけ下げた状態に設定して遷移させる状態遷移制御手段を備える。

(もっと読む)

サンプルホールド回路

【課題】アナログ電圧を、アナログスイッチ20を介してコンデンサ11に接続/切り離し、アナログ電圧をコンデンサ11に保持する構成のサンプルホールド回路では、アナログスイッチを構成するMOSFETのゲートの容量成分によってオンオフを制御する制御信号が変化したときに発生する漏れ電流のためにコンデンサに蓄積された電荷が変化し、正確な電圧を保持することができなかったという課題を解決する。

【解決手段】アナログスイッチ20と逆方向に動作するアナログスイッチ30をアナログスイッチ20に並列に接続するようにした。2つのアナログスイッチの漏れ電流の方向が逆なるので、漏れ電流がキャンセルされ、正確な電圧を保持することができる。

(もっと読む)

バッファ駆動能力制御装置

【課題】駆動力が互いに異なる負荷が、1つの端子に接続されている場合、大きな駆動力で負荷を駆動することによる放射ノイズの発生を抑制することができるバッファ駆動能力制御装置を提供することを目的とする。

【解決手段】駆動能力の大きな負荷を駆動するための駆動能力と駆動能力の小さな負荷を駆動するための駆動能力を切り替えることのできる出力バッファを持ち、駆動能力の大きな負荷を駆動するための制御期間と駆動能力の小さな負荷を駆動するための制御期間とを持ち、それぞれの制御期間に、それぞれの負荷に適した駆動能力に出力バッファの駆動能力を切り替える。

(もっと読む)

出力バッファー回路

【課題】出力バッファーの面積・体積・部品点数の増加を抑制するとともに、ドライブ能力を向上させることが可能な出力バッファー回路を提供する。

【解決手段】第一駆動信号LINを伝達する第一入力経路4a、第二駆動信号RINを伝達する第二入力経路4b、第一入力経路4aと対応する第一出力バッファー6a及び第二入力経路4bと対応する第二出力バッファー6bを備える出力バッファー回路1において、入力経路切り替え手段8が、ステレオモード及びモノラルモードのうち、モノラルモードでは、第一入力経路4aと第一出力バッファー6a及び第二出力バッファー6bとを電気的に接続させ、出力経路切り替え手段10が、第一出力バッファー6a及び第二出力バッファー6bと、第一入力経路4a及び第一出力バッファー6aと対応する第一負荷2aとを、電気的に接続させる。

(もっと読む)

差動制御回路

【課題】差動回路の入力トランジスタのホットキャリア劣化を遅らすことができる差動制御回路を提供する。

【解決手段】動作モード設定回路をなすアップダウンカウンタ24は、最上位ビット出力信号S0を動作モード設定信号として出力する。第1の分配回路28は、最上位ビット出力信号S0がHレベルとされる第1の動作モード時には、入力信号SINを第1の入力トランジスタ19のゲートに与えると共に、基準電圧VREFを第2の入力トランジスタ20のゲートに与え、最上位ビット出力信号S0がLレベルとされる第2の動作モード時には、入力信号SINを第2の入力トランジスタ20のゲートに与えると共に、基準電圧VREFを第1の入力トランジスタ19のゲートに与える。

(もっと読む)

1 - 20 / 61

[ Back to top ]