Fターム[5J500AC15]の内容

増幅器一般 (93,357) | 目的、効果 (9,357) | 素子のバラツキの影響低減 (230) | Tr、ダイオードのバラツキの影響低減 (128)

Fターム[5J500AC15]に分類される特許

1 - 20 / 128

半導体装置

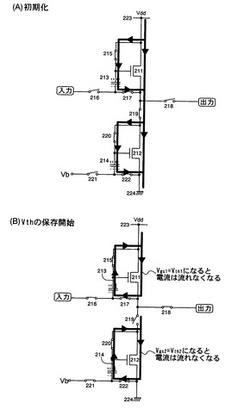

【課題】トランジスタは作製工程や使用する基板の相違によって生じるゲート絶縁膜のバラツキや、チャネル形成領域の結晶状態のバラツキの要因が重なって、しきい値電圧や移動度にバラツキが生じてしまう影響を排除する。

【解決手段】アナログ信号を入力するトランジスタ、及び定電流源としての機能を有するトランジスタのゲート・ソース間電圧又はしきい値電圧に応じた電圧を取得、保持し、後に入力される信号電位に上乗せすることで、トランジスタ間のしきい値電圧のバラツキやゲート・ソース間電圧のばらつきをキャンセルする半導体装置を提供する。ゲート・ソース間電圧又はしきい値電圧に応じた電圧の取得、保持には、トランジスタのゲート・ソース間及びゲート・ドレイン間に設けたスイッチ、及びゲート・ソース間に設けた容量を用いる。

(もっと読む)

電力増幅器

【課題】出力電力に応じて高電力モードおよび低電力モードを切り替え可能で、FETの製造ばらつきを両モードで補償可能な電力増幅器を提供する。

【解決手段】本発明の電力増幅器によれば、高電力モードおよび低電力モードで回路状態を切り替えることによって、バイアス回路部に供給される基準電圧を切り替え、トランジスタのばらつきを補償する。低電力モードでは電源電圧が基準電圧の1/2となるように調整し、高電力モードでは基準電圧をバイアス回路部に伝達する抵抗の値を調整することでアイドル電流の調整を実現する。

(もっと読む)

自動利得調整回路

【課題】利得可変回路の出力振幅の温度依存性を低減する。

【解決手段】自動利得調整回路は、利得可変回路3の出力信号のピーク電圧を検出するピーク検出回路10と、利得可変回路3の出力信号の平均値電圧を検出すると共に、平均値電圧に利得可変回路3の所望の出力振幅の1/2の電圧を加える平均値検出・出力振幅設定回路11と、ピーク検出回路10の出力電圧と平均値検出・出力振幅設定回路11の出力電圧との差分を増幅して、増幅結果を利得制御信号として利得可変回路3の利得を制御する高利得アンプ12とを備える。ピーク検出回路10の入力端子から出力端子までの経路に挿入されるトランジスタのベース−エミッタ接合の数と、平均値検出・出力振幅設定回路11の入力端子から出力端子までの経路に挿入されるトランジスタのベース−エミッタ接合の数とは同一である。

(もっと読む)

電圧レギュレータ回路

【課題】複雑な制御を必要とせず、集積回路のトランジスタの閾値電圧バラツキに応じて所望の動作速度に適した電源電圧を提供することができる。

【解決手段】被安定電圧が入力される入力端子1と、安定化された電圧が出力される出力端子2と、入力端子1および出力端子2と電位差を有する一定電圧に設定される共通端子3と、正入力端子および負入力端子を有する差動増幅器4と、差動増幅器4の出力に基づいて入力端子1から出力端子2に流れる電流を制御する電流制御素子5と、出力端子2と共通端子3との間の電位差を分圧し、差動増幅器4の正入力端子に帰還させる分圧回路6と、出力端子2から電力を供給されるが出力端子2の電圧に依存せず、共通端子3の電圧を基準とする当該集積回路のトランジスタの閾値電圧に比例した電圧を差動増幅器4の負入力端子に出力する閾値参照電圧源7とを備える。

(もっと読む)

半導体装置

【課題】トランジスタは作製工程や使用する基板の相違によって生じるゲート絶

縁膜のバラツキや、チャネル形成領域の結晶状態のバラツキの要因が重なって、

しきい値電圧や移動度にバラツキが生じる。

【解決手段】本発明は、容量素子の両電極がある特定のトランジスタのゲート

・ソース間電圧を保持できるように配置した電気回路を提供する。そして本発明

は、容量素子の両電極間の電位差を定電流源を用いて設定できる機能を有する電

気回路を提供する。

(もっと読む)

バイアス回路を備えたパワーアンプ装置

【課題】ゲート電圧固定バイアス制御方式の歪み特性に優れている利点と、オートバイアス制御方式の個体差や温度変化によらずオペレーションのセット電流値を一定にすることが出来る利点を兼ね備えたパワーアンプ装置を提供する。

【解決手段】FETによる初段アンプ、後段アンプを含むパワーアンプと、入力段に第1のモニター抵抗を接続したオートバイアス回路とを備える。前記オートバイアス回路は前記初段アンプにだけオートバイアスを組み込むために、前記初段アンプ、後段アンプにそれぞれ、前記初段アンプのドレイン電流が一定になるようにセットされたゲート電圧がかかるように接続構成すると共に、主電源の電圧から前記初段アンプには前記第1のモニター抵抗を経由してドレイン電圧がかかり、かつ前記後段アンプには前記主電源の電圧を前記第1のモニター抵抗で分圧したドレイン電圧がかかるように接続構成した。

(もっと読む)

ドハティ増幅器及びドハティ増幅器のバイアス設定方法

【課題】ドハティ増幅器において、デバイスにばらつきがある場合にも、バイアス電圧を最適に設定できると共に、調整工数を削減できるようにする。

【解決手段】キャリア増幅器12とピーク増幅器13とで、ウェハロットや製造時期等のデバイスに関する共通要素を持つものを用い、ピーク増幅器13に対するバイアス電圧Vg2を、キャリア増幅器12に対するバイアス電圧Vg1と、所定のオフセット電圧Voffsetとから生成する。デバイスのばらつきに係わらず、ピーク増幅器13に対するバイアス電圧とピンチオフ電圧との差は同じになり、ピーク増幅器13のバイアス電圧が最適に設定される。また、キャリア増幅器12を構成するFETのゲートに印加するバイアス電圧を調整することで、同時に、ピーク増幅器13を構成するFETのゲートに供給するバイアス電圧も調整できる。

(もっと読む)

カレントミラー回路およびそれを用いた半導体装置

【課題】プロセス変動があった場合でも広い出力電圧範囲が得られるカレントミラー回路を提供する。

【解決手段】この低電圧カスコードカレントミラー回路は、NチャネルMOSトランジスタQ1〜Q5と抵抗素子1を備える。トランジスタQ3のオーバードライブ電圧Vov_Q3は、トランジスタQ4,Q5のオーバードライブ電圧Vov_Q4,Vov_Q5の和に等しい。定電流Icと抵抗素子1の抵抗値R1との積は、トランジスタQ5の飽和マージンVdsm_Q5となる。したがって、プロセス変動があった場合でも、トランジスタQ5の飽和マージンVdsm_Q5は変化しない。

(もっと読む)

送信器

【課題】電力増幅器を高効率化及び高信頼性化する。

【解決手段】一つの実施形態によれば、送信器は、第1のバッファ、第2のバッファ、論理回路、及びE級電力増幅器が設けられる。第1のバッファは、第1の正弦波信号が入力され、第1の正弦波信号を第1の矩形波信号に変換する。第2のバッファは、第1の正弦波信号よりも位相が遅れた第2の正弦波信号が入力され、第2の正弦波信号を第2の矩形波信号に変換する。論理回路は、第1及び第2の矩形波信号が入力され、第1及び第2の矩形波信号を論理演算して所定のデューティーを有するロジック信号を生成する。E級電力増幅器は、ロジック信号が入力され、ロジック信号に基づいて増幅動作する。

(もっと読む)

低雑音増幅器

【課題】製造上の素子の特性ばらつきや電源電圧の変更やばらつきに対しても安定化させる。

【解決手段】入力端子2と、入力端子に入力された入力信号を増幅するトランジスタ1と、トランジスタの出力信号を出力する出力端子3と、トランジスタの出力信号の帰還量として振幅を調整して出力する帰還量調整回路10と、トランジスタに供給されるバイアス電流を生成するバイアス回路9と、帰還量調整回路の出力電圧と参照電圧とを比較して入力信号が前記トランジスタの利得抑圧を発生させることを判定したときトランジスタのバイアス電流を増加させるようにバイアス回路を動作させる差動電圧比較器11と、参照電圧を生成して差動電圧比較器の一方の入力端に印加させる第1の第1の入力バイアス回路12と、帰還量調整回路の出力電圧にバイアス電圧を付加して差動電圧比較器の他方の入力端に印加させる第2の第2の入力バイアス回路13と、を備える低雑音増幅器。

(もっと読む)

単一のプロセスを用いて高性能ロジックおよびアナログ回路をイネーブルするプロセス/設計方法論

【課題】混合信号プロセスにおいてアナログ回路の性能を向上させる方法および装置を提供すること

【解決手段】順方向バイアスおよび修正された混合信号プロセスを用いた回路設計を用いて、アナログ回路性能を向上させる方法が提示される。複数のNMOSトランジスタおよびPMOSトランジスタを含む回路が規定される。NMOSトランジスタのボディ端子は、第1の電圧ソースに連結され、PMOSトランジスタのボディ端子は、第2の電圧ソースに連結される。回路内のトランジスタは、各選択されたNMOSトランジスタのボディ端子に該第1の電圧ソースを適用することと、各選択されたPMOSトランジスタのボディ端子に該第2の電圧ソースを適用することとによって、選択的にバイアスされる。一実施形態において、第1の電圧ソースおよび第2の電圧ソースは、順方向バイアスおよび逆方向バイアスをトランジスタのボディ端子に提供するように修正可能である。

(もっと読む)

電荷検出回路

【課題】差動アンプの入力側のゲイン調整を容易に行うことができる電荷検出回路を提供する。

【解決手段】電荷発生型センサ及び容量変化型センサの何れかで構成される物理量検出センサ1A,1Bの一端が差動アンプ3の負極入力端子に接続され、他端が前記差動アンプ3の正極入力端子に接続され、前記差動アンプ3の出力端子と前記負極入力端子との間にフィードバック抵抗Rf及びフィードバック容量Cfが並列に接続され、且つ前記差動アンプの正極入力端子と基準電圧との間にキャンセル抵抗Rc及びキャンセル容量Ccが並列に接続された差動型の電荷検出回路であって、前記差動アンプの負極入力端子及び正極入力端子の少なくとも一方に逆バイアス電源7,9によって逆バイアス電位が与えられた可変容量ダイオードD1,D2を接続してゲイン調整を可能とした。

(もっと読む)

定電圧回路

【課題】電界効果トランジスタの閾値電圧に対する依存性が抑制された定電圧を供給する定電圧回路を提供する。

【解決手段】本発明にかかる定電圧回路は、第1および第2のノードで互いのドレインおよびゲートが共通接続される電界効果トランジスタQ11およびQ12と、電界効果トランジスタQ11、12のゲートが共通接続される前記第2のノードと電界効果トランジスタQ12のソースとの間に接続される抵抗器R11と、コレクタが前記第2のノードに接続されるバイポーラトランジスタQ13と、電界効果トランジスタQ12のソースに接続し、バイポーラトランジスタQ13のベースにバイアス電圧を供給するバイアス回路101と、を備え、電界効果トランジスタQ11、12のドレインが共通接続される前記第1のノードに電圧源Vbatが接続され、電界効果トランジスタQ11のソースから定電圧を供給する。

(もっと読む)

多入力差動増幅器及び発光素子駆動装置

【課題】反転入力信号と非反転入力信号のうちの一方が複数であって、当該複数の入力信号を選択し、この選択した信号と反転入力信号と非反転入力信号のうちの他方との差を増幅することができる多入力差動増幅装置を提供する。

【解決手段】 反転入力端子と非反転入力端子とを有する差動増幅器1と、反転入力端子及び非反転入力端子の一方の入力端子(以下、第1の入力端子)に複数の該第1の入力端子用の入力信号(以下、第1の入力信号)IN-1~IN-3に応じた第1の入力電圧を印加し、かつ反転入力端子及び非反転入力端子の他方の入力端子(以下、第2の入力端子)に、1つの該第2の入力端子用の入力信号(以下、第2の入力信号)IN+に応じた第2の入力電圧を印加する入力部2と、を備え、入力部2は、第1の入力電圧と第2の入力電圧と間のオフセット電圧を補正するよう構成されている。

(もっと読む)

受光回路および受光回路を備える電子機器

【課題】受光回路における、素子のバラツキによる特性の劣化や、出力インピーダンスの劣化といった問題や、受光素子への正常なバイアス電圧を確保できないといった問題の、少なくとも1つを解決する。

【解決手段】施形態の受光回路は、電流源回路とローパスフィルタと電流検知回路とを持つ。電流源回路は、受光素子に対し直流電流を供給する。ローパスフィルタは、使用する信号帯域をカットする。電流検知回路は、前記電流源回路と同一種類のデバイスにより前記電流源回路とカレントミラー回路を構成し、流入電流を検知し、該検知結果に応じて、前記ローパスフィルタを介し前記電流源回路を制御する。

(もっと読む)

半導体装置及び電子機器

【課題】負荷(EL画素や信号線)に電流を供給するトランジスタにおいて、バラツキの影響を受けずに正確な電流を供給できる半導体装置を提供する。

【解決手段】増幅回路を使ったフィードバック回路を用いて、トランジスタの各端子の電圧を調節する。電流源回路から電流Idataをトランジスタに入力して、トランジスタが電流Idataを流すのに必要なゲート・ソース間電圧を、フィードバック回路を用いて設定する。フィードバック回路は、トランジスタが飽和領域で動作するように制御する。すると、電流Idataを流すのに必要なゲート電圧が設定される。そして、設定されたトランジスタを用いれば、正確な電流を負荷(EL画素や信号線)に供給できる。なお、必要なゲート電圧を設定するとき、増幅回路を用いるので、すばやく設定できる。

(もっと読む)

増幅器

【課題】変換効率及び/又は増幅線形性を向上させることができる増幅器を提供することである。

【解決手段】ソースが基準電位ノードに接続され、ドレインが出力ノードに接続される第1及び第2の電界効果トランジスタ(Tr1,Tr2)と、第1の電界効果トランジスタのゲート及び入力ノード間に接続される第1の容量(C1)と、第1の電界効果トランジスタのゲートに接続される第1のゲートバイアス電位ノード(Vg1)と、第2の電界効果トランジスタのゲート及び入力ノード間に接続される第2の容量(C2)と、第2の電界効果トランジスタのゲートに接続される第2のゲートバイアス電位ノード(Vg2)と、出力ノードに接続されるドレインバイアス電位ノード(Vdd)とを有し、第1の電界効果トランジスタのゲート幅は、第2の電界効果トランジスタのゲート幅より広く、第1の容量の容量値は、第2の容量の容量値より大きい増幅器が提供される。

(もっと読む)

高周波電力増幅器およびその動作方法

【課題】電力増幅電界効果トランジスタのゲート長の依存性による電力利得の変動を軽減する。

【解決手段】高周波電力増幅器は、バイアス制御回路112とカレントミラー接続のバイアストランジスタ516と増幅トランジスタ513と、複製トランジスタ421を有するゲート長モニタ回路101を半導体チップに具備する。513はRF信号を増幅して、516にバイアス制御回路112のバイアス電流が供給される。516、513、421は同一の半導体製造プロセスで形成され、同一のゲート長のばらつきを有する。ゲート長モニタ回路101はゲート長Lに依存した検出電圧Vmonを生成して、検出電圧に従ってバイアス制御回路112がバイアス電流を制御して増幅トランジスタ513のトランスコンダクタンスのゲート長依存性を補償する。

(もっと読む)

ディプレッション型FET用バイアス印加回路

【課題】単電源駆動の構成において常に所望のバイアス条件が得られると共に、生産性の向上、コストの低減を図ることができるようにする。

【解決手段】N−chディプレッション型FET1を単一の正電源3で駆動する構成において、FET1のソースと接地との間に、ソース電圧を制御するための第1(NPN)トランジスタQ1 が接続され、この第1トランジスタQ1 のベースには、このベースにFET1のドレイン電流の大きさに応じた調整用電流を供給するための第2(PNP)トランジスタQ2 が接続される。また、FET1のドレインと正電源3との間に、ドレイン電流検出用の抵抗R3が接続され、上記第1トランジスタQ1 によりFET1のソース電圧を制御することで、FET1のドレイン電流が常に一定となるように自動調整を行う。

(もっと読む)

出力バッファ回路、入力バッファ回路、及び入出力バッファ回路

【課題】スルーレートを適切に調整可能なバッファ回路を提供する。

【解決手段】

CMOS出力バッファ回路は、バッファ回路Buffer[1]〜[4]を備えている。各バッファ回路は、電源電圧端子又は接地端子と出力端子との間にトランジスタPO及びNOを有している。各バッファ回路中の複数個のトランジスタPO及びNOは、外部からの制御信号に従い選択的に動作可能な状態とされる。各バッファ回路中の3個のトランジスタPOは、所定のサイズ比を有するように形成されている。

(もっと読む)

1 - 20 / 128

[ Back to top ]