Fターム[5J500AC36]の内容

Fターム[5J500AC36]に分類される特許

81 - 100 / 1,415

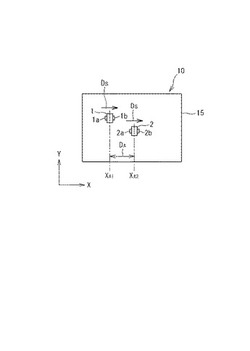

ドハティ増幅装置及び通信装置

【課題】ドハティ増幅装置の効率低下を防止する。

【解決手段】ドハティ増幅装置は、メインアンプを構成するメインアンプデバイス1と、ピークアンプを構成するピークアンプデバイス2と、メインアンプデバイス1及びピークアンプ2が実装された基板15とを有している。メインアンプデバイス1は、第1デバイス本体1c、第1入力端子1a、及び、第1出力端子1bを備え、第1入力端子1a及び第1出力端子1bが第1デバイス本体1cを挟んで対向して配置されている。ピークアンプデバイス2は、第2デバイス本体2c、第2入力端子2a、及び、第2出力端子2bを備え、第2入力端子2a及び第2出力端子2bが第2デバイス本体2cを挟んで対向して配置されている。ピークアンプデバイス2は、メインアンプデバイス1の位置に対して、メインアンプデバイス1の第1入力端子から第1出力端子に向かう入出力方向Dsにずれた位置に、実装されている。

(もっと読む)

増幅装置、送信装置

【課題】出力信号の歪みを抑えつつ効率を向上することのできる増幅装置、送信装置を提供する。

【解決手段】実施形態に係る増幅装置は、飽和出力電力が互いに異なる複数の増幅回路を具備している。実施形態に係る増幅装置は、入力端子に入力された入力信号の包絡線信号を検出する検波器と、前記検波器が検出した包絡線信号の信号電圧を、それぞれ異なる参照電圧と比較する複数の比較器と、前記複数の比較器の比較結果に基づいて前記複数の増幅回路のいずれか一つを選択する切替制御部とを具備している。そして、実施形態に係る増幅装置は、前記入力端子を前記切替制御部が選択した増幅回路の入力に接続するとともに、前記切替制御部が選択した増幅回路の出力を出力端子に接続する切替部とを具備することを特徴としている。

(もっと読む)

利得制御装置および回路モジュール

【課題】本発明は、利得制御装置および回路モジュールに関し、構成の大幅な変更と性能の低下とを伴うことなく、ハードウェアの規模の縮小を可能とすることを目的とする。

【解決手段】回路に入力された入力信号、または出力された出力信号の周波数に対応して、前記回路に対する前記出力信号の負帰還に供される帰還路に設定されるべき利得が予め登録された記憶手段と、前記周波数に対応して前記記憶手段に登録された利得を前記帰還路に設定する制御手段とを備え、前記記憶手段には、前記周波数が分布し得る帯域の内、前記負帰還の下で前記出力信号のレベルが既定の範囲内に維持される部分帯域毎に、前記利得が共通の利得として登録され、前記制御手段は、前記部分帯域の内、前記周波数が属する特定の部分帯域に対応して登録された共通の利得を前記帰還路に設定する。

(もっと読む)

電力増幅回路

【課題】F級増幅器における効率を改善することができる電力増幅回路を提供する。

【解決手段】電力増幅回路は、予め定められた周波数の基本波を含む信号を増幅する増幅素子と、増幅素子が増幅した信号に含まれる基本波と、基本波の2倍波と、基本波の3倍波とそれぞれの特性インピーダンスとのインピーダンス整合をとる出力整合回路と、2倍波の反射位相を変化させる2倍波用チューナーと、3倍波の反射位相を変化させる3倍波用チューナーと、出力整合回路が出力する信号に含まれる基本波を通過させるとともに、信号に含まれる2倍波及び3倍波を反射する高調波反射フィルタであって、2倍波用チューナー及び3倍波用チューナーが接続され、2倍波用チューナー及び3倍波用チューナーを用いて2倍波及び3倍波の反射位相を独立に変化させる高調波反射フィルタとを備える。

(もっと読む)

スイッチング回路

【課題】整数倍の信号成分に起因して、負荷回路やスイッチング素子に余分な電流が流れない電力効率を向上したスイッチング回路を提供する。

【解決手段】スイッチング回路1は、第1端子50a及び第2端子50bを有しており、パルス信号により駆動されて第1端子及び第2端子の導通状態をスイッチするスイッチング素子10と、スイッチング素子の第1端子13に電圧を供給する電源部30と、電源部に並列に接続される負荷回路40と、電源部と負荷回路との接続点Pと、スイッチング素子の第1端子との間に接続され、パルス信号のクロック周波数のN倍(Nは1以上の整数)の周波数において、接続点からスイッチング素子へ流れる電流を抑制する受動回路部50と、受動回路部と接続点との間に接続され、N倍の周波数において共振する共振回路部60と、を備える。

(もっと読む)

駆動用ドライバ、駆動用アンプおよび情報機器

【課題】圧電素子等の容量性負荷にチャージされたエネルギーを無駄に消費することなく、容量性負荷を低消費電力で駆動することのできる駆動用ドライバ、駆動用アンプおよび情報機器を提供する。

【解決手段】スイッチング駆動回路24は、容量性負荷である圧電スピーカ15に転送されたエネルギーを抵抗等でなるべく消費させずに、インダクタ42を介してキャパシタ41に再びチャージし、容量性負荷の駆動に再利用する。これにより、圧電スピーカ駆動用アンプ14は、圧電スピーカ15を低消費電力で駆動することができる。その際、圧電スピーカ15を駆動するために必要なエネルギーは、ダイオード48を介して、電源から自動的にキャパシタ41に補充される。従って、ゲートドライバ23は、スイッチング素子の制御を簡潔に行うことができる。

(もっと読む)

電力増幅器

【課題】素子ばらつきや周波数特性に対して鈍感であり低損失な電力増幅器を得る。

【解決手段】入力端子INから入力した入力信号を増幅素子Tr1が増幅する。増幅素子Tr1の出力信号を増幅素子Tr2が増幅する。増幅素子Tr2の出力信号は出力端子OUTから出力される。増幅素子Tr2の出力と出力端子OUTとの間に整合回路M3a,M3bが接続されている。増幅素子Tr1の出力と増幅素子Tr2の入力との間にスイッチSW1が接続されている。増幅素子Tr1の出力にスイッチSW2の一端が接続されている。整合回路M3a,M3bは、増幅素子Tr2の出力と接地点との間に直列に接続されたインダクタL5及びキャパシタC1を有する。インダクタL5とキャパシタC1を接続する接続点Xに、スイッチSW2の他端が接続されている。

(もっと読む)

トンネル電流回路

【課題】消費電力の少ない基準電圧を発生する回路を、従来並みのサイズで提供することを目的とする。

【解決手段】

半導体接合に異なる電流密度の電流を流したときの差電圧に比例する電圧と、半導体接合に生ずる順方向電圧に比例する電圧とを加算して出力電圧とするバンドギャップリファレンス回路において、

前記差電圧が印加される第一のトンネル電流素子と、

第二のトンネル電流素子もしくは第二の複数のトンネル電流素子を直列接続した回路と、

前記第一のトンネル電流素子に流れる電流に比例した電流を前記第二のトンネル電流素子に流す手段によって、

上記「差電圧に比例する電圧」を発生させることを特徴とする。

(もっと読む)

パルス幅変調回路およびスイッチングアンプ

【課題】 蓄積手段に蓄積された電圧が無駄に放電されることを防止する。

【解決手段】 コンパレータCOMP1の出力がハイレベルのときに、コンデンサC3は、コンデンサC1の電圧によって充電される。次に、コンパレータCOMP1の出力がローレベルのときに、コンデンサC3の電圧が定電流Iの生成に使用される。同様に、コンパレータCOMP2の出力がハイレベルのときに、コンデンサC4は、コンデンサC2の電圧によって充電される。コンパレータCOMP2の出力がローレベルのときに、コンデンサC4の電圧が定電流Iの生成に使用される。従って、コンデンサC1、C2の電圧が無駄に放電されることが無く、定電流Iの生成に再度利用することができる。

(もっと読む)

半導体集積回路

【課題】効果的に雑音レベルを低減した半導体集積回路を提供する。

【解決手段】差動入力トランジスタであるPチャネル型MOSトランジスタM1,M2は、雑音レベルを低減するために薄いゲート酸化膜を有している。これらのPチャネル型MOSトランジスタM1,M2を過電圧から保護する保護回路は、Pチャネル型MOSトランジスタM3,M4を含んで構成されている。Pチャネル型MOSトランジスタM3はPチャネル型MOSトランジスタM1を過電圧から保護する第1の保護トランジスタであり、Pチャネル型MOSトランジスタM1のドレイン側に直列に接続されている。Pチャネル型MOSトランジスタM4は、Pチャネル型MOSトランジスタM2を過電圧から保護する第2の保護トランジスタであり、Pチャネル型MOSトランジスタM2のドレイン側に直列に接続されている。

(もっと読む)

自動利得調整回路

【課題】利得可変回路の出力振幅の温度依存性を低減する。

【解決手段】自動利得調整回路は、利得可変回路3の出力信号のピーク電圧を検出するピーク検出回路10と、利得可変回路3の出力信号の平均値電圧を検出すると共に、平均値電圧に利得可変回路3の所望の出力振幅の1/2の電圧を加える平均値検出・出力振幅設定回路11と、ピーク検出回路10の出力電圧と平均値検出・出力振幅設定回路11の出力電圧との差分を増幅して、増幅結果を利得制御信号として利得可変回路3の利得を制御する高利得アンプ12とを備える。ピーク検出回路10の入力端子から出力端子までの経路に挿入されるトランジスタのベース−エミッタ接合の数と、平均値検出・出力振幅設定回路11の入力端子から出力端子までの経路に挿入されるトランジスタのベース−エミッタ接合の数とは同一である。

(もっと読む)

変調電源回路

【課題】出力電圧誤差が少ない、多出力DC電源部およびその切り替え回路と誤差増幅器を用いた変調電源回路を提供する。

【解決手段】多出力DC電源部101と、それらの各出力経路に直列に接続され、エンベロープ信号アナログ入力部103から入力されるエンベロープ信号と閾値とを比較する切り替え電圧の閾値判定部114の出力で制御される切り替え回路102と、入出力をAC結合した誤差増幅器105と、切り替え電圧の閾値判定部114とこの切り替え電圧の閾値判定部114の出力に接続された任意電圧発生部106とを備え、切り替え電圧を任意電圧分だけずらすように構成する。これにより、高周波増幅器109に誤差の少ない電圧を出力することができる。

(もっと読む)

半導体装置

【課題】消費電力が低減された半導体装置を提供することである。

【解決手段】入力電位および基準電位が入力される差動増幅器、利得段および出力電位が出力される出力段を有する半導体装置において、該出力段にオフ状態でのリーク電流が低いトランジスタを配置することで、該利得段から供給される電位が一定に保持される半導体装置である。また、オフ状態でのリーク電流が低いトランジスタとしては、酸化物半導体層を有し、且つ酸化物半導体層にチャネル形成領域を有するトランジスタを用いることである。

(もっと読む)

電源制御回路

【課題】 G級増幅器の製造ばらつき、負荷の大きさに応じて、最適な条件で増幅部の電源電圧を低下させるモードダウンを実行し、無駄な電力損失を低減する。

【解決手段】 モード制御部301は、増幅部1の出力電圧VOUTに応じて、電源電圧+VBおよび−VBを現状より高い電源電圧に切り換えるモードアップを行うとともに、出力電圧VOUTが所定時間以上に亙って閾値電圧+Vdwn〜−Vdwnの範囲内の電圧値を維持した場合に電源電圧を現状より低い電源電圧に切り換えるモードダウンを行う。逐次比較型A/D変換部330は、モードアップが行われたときの増幅部1の出力電圧VOUTに基づいて閾値電圧+Vdwnおよび−Vdwnを設定する。

(もっと読む)

半導体装置とその動作方法

【課題】半導体装置において、消費電力を低減する。また、スタンバイ回路を少ない素子で構成し、半導体装置の回路面積の増大を防ぐ。

【解決手段】半導体装置に備えるスタンバイ回路をトランジスタ一つのみで構成し、該トランジスタに供給する電圧を切り替えることで、半導体装置の出力電流を制御する。これにより、スタンバイ状態での半導体装置の出力電流をほぼゼロにすることができるため、消費電力の低減が可能になる。なお、トランジスタの半導体層に酸化物半導体を用いることで、リーク電流を極小に抑えることができる。

(もっと読む)

能動回路

【課題】2倍波処理回路の動作の阻害を防ぎ、動作効率の劣化を防ぐ能動回路を得る。

【解決手段】バイアス回路5において、基本波整合回路4の出力側に接続され、基本波周波数成分を全通過させ、2倍波周波数成分を反射するフィルタ回路51と、基本波整合回路4の出力側とフィルタ回路51との間に接続され、基本波周波数で並列共振し、2倍波周波数に対してほぼ純抵抗となる2倍波吸収回路52と、2倍波吸収回路52に接続され、バイアス電圧を供給するバイアス電圧供給回路53とを備えた。

バイアス回路5において、2倍波周波数成分を高周波トランジスタ2側に反射させずに吸収することによって、2倍波処理回路3とバイアス回路5とで並列共振を起こすことがなく、その結果、2倍波処理回路3の動作の阻害を防ぎ、動作効率の劣化を防ぐ能動回路を得ることができる。

(もっと読む)

サンプルホールド回路

【課題】サンプルホールド機能とマルチプレクサ機能とを具備したサンプルホールド回路を互いに位相が反転した2相信号のみでサンプルホールド機能とマルチプレクサ機能とを提供する。

【解決手段】2つのサンプルホールド回路10,11は、非反転入力端が基準電位に接続された差動増幅器A1,A2と、制御信号φ1に従ってオンオフするスイッチ及びサンプリング容量C1,C3と、制御信号φ1に従ってオンオフするスイッチ及びホールド容量C2,C4と、制御信号φ2に従ってオンオフするスイッチと、を備える。マルチプレクサ回路12は、非反転入力端が基準電位に接続された差動増幅器A3と、制御信号φ1,φ2に従ってオンオフするスイッチと、差動増幅器A3の出力端と反転入力端との間に接続されたホールド容量C5と、を備える。

(もっと読む)

増幅回路

【課題】簡易な構成で歪を抑制しつつ消費電流を低減する。

【解決手段】増幅回路100は、正入力端子T1と負入力端子T2とに供給される電圧の差分を増幅し差分電圧Vaを出力する差動増幅部10と、入力信号Vinの電圧を検出し検出電圧Vbを出力する入力電圧検出部20と、正電源電圧+Vccが供給される正電源端子T6と出力端子Toutとの間に設けられ、出力端子Toutから電流を吐き出すPMOS31と、負電源電圧−Vccが供給される負電源端子T7と出力端子Toutとの間に設けられ、出力端子Toutから電流を吸い込むNMOS32とを有する出力部30とを備える。

(もっと読む)

半導体装置

【課題】レイアウト面積を大きくすることなく、差動対を高速/高消費電流と、低速/低消費電流の両方で動作させることができるようにした半導体装置を提供する。

【解決手段】差動回路5aは、差動対トランジスタN1,N2と、差動対トランジスタN1,N2に流れる電流量が少なくとも2つのレベルで切替わるように、切替可能なテール電流を供給するテール電流源68とを備える。差動対トランジスタN1,N2は、差動対トランジスタN1,N2に流れる電流の減少に伴って、σ(ΔI/gm)の値が単調に減少する特性を有する、ただし、σは標準偏差、ΔIは、差動対トランジスタN1,N2の電流量の差分、gmは、差動対トランジスタN1,N2のトランスコンダクタンスを表わす。

(もっと読む)

可変出力増幅器

【課題】低出力時の回路損失を低減し、低出力時の効率を高める可変出力増幅器を得る。

【解決手段】トランジスタ5と共に並列接続されたトランジスタ11と、信号出力される平均電力レベルを所定の値よりも小さくするときには、トランジスタ5のみ動作するようにバイアス電圧を印加し、信号出力される平均電力レベルを所定の値よりも大きくするときには、トランジスタ5,11の両方が動作するようにバイアス電圧を印加するバイアス制御回路12とを備えた。

このように構成したことにより、低出力時および高出力時に関わらずバイパス経路を用いずに、トランジスタ5,11の信号出力をそのまま出力するため、低出力時の回路損失を低減し、低出力時の効率を高めることができる。

(もっと読む)

81 - 100 / 1,415

[ Back to top ]