Fターム[5J500AC62]の内容

Fターム[5J500AC62]の下位に属するFターム

ピーキング (11)

Fターム[5J500AC62]に分類される特許

21 - 40 / 288

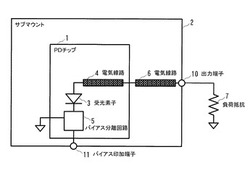

光受信回路

【課題】受光素子の直近にインダクタンス素子を配置することなしに光受信回路を広帯域化する。

【解決手段】光受信回路は、光信号を電気信号に変換する受光素子3と、受光素子3のアノードと出力端子10との間を接続する電気線路4,6と、受光素子3のカソードを交流的に接地すると共に、カソードに直流バイアスを印加するバイアス分離回路5とを備える。電気線路4,6の特性インピーダンスは、出力端子10に接続される負荷抵抗7の抵抗値よりも高い。

(もっと読む)

ドハティ増幅器

【課題】広帯域化と小型化を図ることのできるドハティ増幅器を得る。

【解決手段】単位ドハティ増幅器100a,100bにおけるピーク増幅器2a,2bの入力側に、これらピーク増幅器2a,2bが共用する1/4波長線路3を設ける。単位ドハティ増幅器100a,100bのキャリア増幅器1a,1bの出力側にはそれぞれ1/4波長線路6a,6bが設けられ、キャリア増幅器1a,1bの出力とピーク増幅器2a,2bの出力とは信号合成器7で合成される。これにより広帯域化を図ることができると共に、ピーク増幅器2a,2b入力側の1/4波長線路を削減することができるため、小型化を図ることができる。

(もっと読む)

広帯域マイクロ波増幅器

【課題】クラスEのHPAが広い帯域幅にわたって同時に高いPAE及び電力を維持することを可能にする。

【解決手段】スイッチングモード電力増幅器の出力に結合されたシャント誘導素子と、前記増幅器の前記出力に結合されている直列の誘導素子と、前記直列の誘導素子に結合されている直列の容量素子とを含む構成とした。

(もっと読む)

分布形増幅器

【課題】利得の低下を防止して、高利得、高出力、高効率及び広帯域特性を実現することができる分布形増幅器を得ることを目的とする。

【解決手段】並列に接続されている複数のトランジスタ1a〜1jと、複数のトランジスタ1a〜1jに対して入力側バイアス電圧を供給する電圧源2と、複数のトランジスタ1a〜1jに対して出力側バイアス電圧を供給する電圧源5,7とを備え、電圧源5,7から複数のトランジスタ1a〜1jに供給される出力側バイアス電圧のうち、トランジスタ1aに供給される出力側バイアス電圧が、トランジスタ1b〜1jに供給される出力側バイアス電圧と異なるように構成する。

(もっと読む)

検波対数増幅器

【課題】 可変減衰器を用いて、対数増幅器の動作点を制御することで、広帯域、広ダイナミックレンジにおいて良好な直線性を有する検波対数増幅器を提供する。

【解決手段】 外部制御電圧により減衰量を連続的に可変可能な可変減衰器と、前記可変減衰器の出力に接続された増幅器と、前記増幅器の出力に接続され、入力信号電力に応じ直流の検波出力を発生する検波器と、前記検波器の出力に接続された対数増幅器と、前記対数増幅器の出力電圧が第1の基準電圧よりも大きい時、前記可変減衰器の減衰量を増加させる制御信号が出力され、前記対数増幅器の出力電圧が第2の基準電圧よりも小さい時、前記可変減衰器の減衰量を減少させる制御信号を出力する機能を有する制御器と、前記可変減衰器への制御電圧を所定倍し出力する変換回路と、前記対数増幅器の出力と前記変換回路の出力とを加算する加算器とを備えた。

(もっと読む)

C級増幅器

【課題】高効率でかつ広帯域化されたC級増幅器を提供する。

【解決手段】本実施の形態に係るC級増幅器は、電源電圧がVdc、最大電流がImaxの増幅素子の流通角θoがπ(rad)未満において、前記増幅素子の等価回路の従属電流源から見た基本波の負荷インピーダンスをZ1=R1+j・X1、2倍波の負荷インピーダンスをZ2=R2+j・X2とし、X1とR1の関係を−R1≦X1≦R1、R1をR1=Vdc/Imax・π・{1−cos(θo/2)}/{θo/2−sin(θo)/2}、X2/X1をX2/X1=−{θo/2−sin(θo)/2}/{sin(θo/2)−sin(1.5・θo)/3}に、あるいはそれぞれの近傍にする。

(もっと読む)

利得可変差動増幅回路

【課題】広いダイナミックレンジを確保しつつ利得を変化させることが可能な利得可変差動増幅回路を提供すること。

【解決手段】この利得可変差動増幅回路12は、差動対トランジスタQ1,Q2,Q3,Q4とそれらのトランジスタのそれぞれのコレクタに接続された負荷抵抗14,15,18,19とそれらのトランジスタのエミッタに共通に接続された電流源16,20とをそれぞれ含む差動増幅回路17,21を有し、次段差動増幅回路21の出力を、帰還トランジスタQ5,Q6を介して初段差動増幅回路17に帰還させる利得可変差動増幅回路において、該初段差動対トランジスタQ1,Q2を流れるべき電流を分岐させる電流分岐回路部12Cと、差動対トランジスタQ1,Q2に電流を供給する電流供給回路部12Bとを備える。

(もっと読む)

低雑音増幅器

【課題】低雑音増幅器の周波数帯域を拡大すること。

【解決手段】入力信号がゲートに供給されるソース接地トランジスタと、前記ソース接地トランジスタのドレイン電流が供給される第1の負荷とを有する増幅回路と、前記入力信号がソースに供給されるゲート接地トランジスタと、前記ゲート接地トランジスタのドレイン電流が供給される第2の負荷とを有する終端回路と、前記ゲート接地トランジスタのソースとドレインの間に接続されたアクティブインダクタとを有すること。

(もっと読む)

2段のマイクロ波のE級電力増幅器

【課題】より広い周波数範囲で同時的な高電力と高電力付加効率(PAE)をもたらす改良されたE級増幅器を提供する。

【解決手段】2段のE級の高電力増幅器100は駆動装置段102、E級段間整合ネットワーク(ISMN)104、負荷回路を使用する高電力段106を含んでいる。負荷回路はスイッチングモード回路の出力に結合されている直列の誘導性−容量性ネットワークと、スイッチングモード回路の出力に結合されているキャパシタンスを提供するための回路を含んでいる。

(もっと読む)

誤差増幅回路及びスイッチングレギュレータ

【課題】位相補償回路を内蔵する誤差増幅回路と比較して、回路規模及び回路の消費電流を大きくすることなく、位相補償容量を外付けにすることができる誤差増幅回路及び当該誤差増幅回路を用いたスイッチングレギュレータを提供する。

【解決手段】所定の基準電圧Vref1と入力電圧Vfb1との誤差を増幅して出力する誤差増幅器12と、誤差増幅器12にバイアス電流Ibias1を供給する電流生成回路11とを含む集積回路10を備えた誤差増幅回路10aにおいて、集積回路10は、電流生成回路11に接続されたバイアス電流制御端子T1と、位相補償抵抗14を介して誤差増幅器12の出力端子T11に接続された位相補償端子T2とを備え、誤差増幅回路10aは、位相補償端子T2に接続された位相補償容量30を集積回路10の外部に備える。

(もっと読む)

全二重伝送回路、及び電子機器

【課題】消費電力を低減すること。

【解決手段】送信信号が入力される第1の内部入力端子と、送信信号に比べて振幅が1/2であり、かつ、送信信号と同相の信号が入力される第2の内部入力端子と、特性インピーダンスZを有する伝送路に接続された外部入出力端子と、外部入出力端子から入力された受信信号が出力される内部出力端子と、ソースが電流源及び外部入出力端子に接続され、ゲートが第1の内部入力端子に接続され、ドレインが第2のMOSトランジスタのソース及び内部出力端子に接続された第1のMOSトランジスタと、ソースが第1のMOSトランジスタのドレイン及び内部出力端子に接続され、ゲートが第2の内部入力端子に接続された第2のMOSトランジスタと、を備え、第1及び第2のMOSトランジスタのトランスコンダクタンスが1/Zとなる、全二重伝送回路が提供される。

(もっと読む)

光受信モジュールおよび光受信モジュールの製造方法

【課題】光受信モジュールにおいて、同一設計の受光素子を用いながら入力インピーダンスの異なるプリアンプを用いた場合にでも良好な周波数通過特性(S21)を実現する。

【解決手段】受光素子を搭載した半導体チップ6と、受光素子の出力信号を増幅するプリアンプ2と、受光素子を搭載する絶縁性キャリア基板3と、受光素子の出力信号がキャリア基板上の電極5を介してプリアンプに入力されるように接続し、受光素子を搭載しない状態でキャリア基板上の2電極間の容量値を40fF以上とした2電極4、5を有することより解決できる。

(もっと読む)

入れ子状のトランスインピーダンス増幅器

【課題】光ファイバ受信器やハードディスクドライブ向けに、大きい帯域幅及び高利得TIAを提供する。

【解決手段】入れ子状のトランスインピーダンス増幅器(TIA)回路は、入力及び出力を有する0次のTIAと、第1の演算増幅器(オペアンプ)と、を備えている。オペアンプは、0次のTIAの出力に接続する入力と、該入力によって駆動される第1のトランジスタと、第1のバイアス電圧によって駆動され且つ上記第1のトランジスタに接続する第2のトランジスタと、第2のトランジスタに接続する第1の電流源と、第1のトランジスタと第2のトランジスタの間のノードに存在する出力と、を備えている。

(もっと読む)

フィードフォワード歪み補償高周波増幅装置

【課題】マルチキャリア信号など複数の通過帯域からなる広帯域の信号の増幅に適用して低損失化が図れるようにしたフィードフォワード歪み補償高周波増幅装置を提供すること。

【解決手段】A帯域用第2の方向性結合器120の本線出力にBPF301を接続し、B帯域用第2の方向性結合器220の本線出力にはBPF302を接続し、これらBPF301とBPF302の出力を合成器30により合成することにより、A帯域用の歪み補償ループの本線とA帯域用の歪み補償ループの本線とを共通化した上で、遅延線306を介してAB共用の方向性結合器133に供給し、AB帯域共用信号出力端150からA帯域の信号とB帯域の信号が出力されるようにしたもの。

(もっと読む)

群遅延時間調整回路および電力分配合成回路

【課題】伝送線路の中心周波数での位相を維持した状態で、群遅延時間(位相の周波数特性の傾き)を任意に調整できる群遅延時間調整回路および電力分配合成回路を提供する。

【解決手段】群遅延時間調整回路10は、信号が入力する入力端子21、信号を出力するアイソレーション端子22、結合端子23および通過端子24を備えた3dBハイブリッド回路20と、片端が結合端子23に接続され、他端が接地された、第1の特性を有する第1のリアクタンス30と、片端が通過端子24に接続され、他端が接地された、第1の特性を有する第2のリアクタンス40と、アイソレーション端子22に接続され、第1の特性に対応する電気長が設定された調整用線路50と、を備える。

(もっと読む)

アンプ回路とそれを備える充電または放電制御回路とその制御方法

【課題】制御開始のタイムラグを低減したアンプ回路とそれを備える充電または放電制御回路とその制御方法とを提供することを目的とする。

【解決手段】誤差アンプと、誤差アンプの出力にベースが接続されたトランジスタと、トランジスタのコレクタとエミッタとの間に接続された負荷と、誤差アンプの出力と誤差アンプのマイナス側入力との間に接続された位相補償コンデンサと、を備えるアンプ回路において、位相補償コンデンサと直列に接続されたフォトモススイッチを備え、フォトモススイッチは、トランジスタのベース電流の有無に対応してオン・オフが制御されるアンプ回路とする。

(もっと読む)

駆動回路、及び、光送信装置

【課題】変調信号の大きさ及び応答速度を向上可能な駆動回路及び光送信装置を提供する。

【解決手段】差動信号の入力に応じて発光素子LDの駆動電流を増減する駆動回路3である。差動信号の正相信号Vinpが入力される端子と、差動信号の逆相信号Vinnが入力される端子と、発光素子LDのアノードに接続されている端子と、正相信号Vinpが入力される端子及びアノードに接続されている端子に接続されている正相信号処理回路と、逆相信号Vinnが入力される端子及びアノードに接続されている逆相信号処理回路と、を備える。正相信号処理回路は、正相信号Vinpに応じて、駆動電流を増加するように制御し、逆相信号処理回路は、逆相信号Vinnに応じて、駆動電流を減少するように制御する。

(もっと読む)

広帯域増幅器

【課題】高い周波数までの二次歪成分を除去し、出力電流信号の線形性を向上させることができ、二次歪耐性(IIP2)を向上させることができる広帯域増幅器を実現する。

【解決手段】第1及び第2のMOSトランジスタQ1,Q2による差動対が発生する二次歪成分電流と逆極性の電流信号を差動対の負荷電流源となる第3及び第4のMOSトランジスタQ3,Q4によって発生し、逆極性の二次歪電流を相互に打ち消し合うように作用させて線形性を向上させ、更に、第1及び第2のMOSトランジスタQ1,Q2の入力へのバイアスを設定する第1のバイアス回路を第1及び第2のMOSトランジスタのドレイン電流が流れるように、且つ、該ドレイン電流をゲート電圧で二回微分した成分の絶対値が極小となるようなバイアス値を得るようにし、且つ、第3及び第4のMOSトランジスタQ3,Q4のサイズを二次歪み成分が主成分である電流を生成するように設定する。

(もっと読む)

広帯域増幅器

【課題】RFで動作するシングルエンド出力であるフィードバック型の広帯域増幅器における二次歪み耐性を向上させる。

【解決手段】主増幅MOSトランジスタQ1を含むシングルエンド出力であるフィードバック型の主増幅器310における電圧−電流変換抵抗素子R1と並列に主増幅器310とは逆極性のMOSトランジスタで構成されたバイパス回路320を設け、このバイパス回路320の副増幅MOSトランジスタQ3へのバイアス値を所定値に合わせ込むことによって、主増幅器310に生じる二次歪成分のみに対し逆極性で且つ相似な特性を呈するバイパス作用信号を生成し、該バイパス作用信号で主増幅器310に生じる二次歪成分をバイパス回路320側に引き込むことによって、主増幅器310とバイパス回路320とを含む広帯域増幅器300の二次歪み耐性を向上させる。

(もっと読む)

スイッチトキャパシタ回路、サンプル・ホールド回路、および、A/D変換装置

【課題】CLS技術を用いたスイッチトキャパシタ回路に適用する演算増幅器の動作速度に関する所要水準を抑制しつつ比較的振幅の大きい入力信号にも適合するという優位性を維持したスイッチトキャパシタ回路等を実現する。

【解決手段】コンデンサCclsおよびスイッチSW104、SW105、SW106を含んでCLS回路120を構成する一方、スイッチSW107が介挿された導体部、および、SW104、SW105、SW106により切替え回路130を構成し、この切替え回路130によってレベルシフト用コンデンサCclsを、サンプリングフェーズで、アナログ入力信号Vinで充電されるように接続し、レベルシフトフェーズで、アナログ信号出力端子Vbと演算増幅器110の出力端子との間に介挿されるように接続関係を切替えるように構成する。

(もっと読む)

21 - 40 / 288

[ Back to top ]