Fターム[5J500AF08]の内容

Fターム[5J500AF08]に分類される特許

141 - 160 / 513

歪み補償装置

【課題】メモリ効果歪みを効果的に打ち消すことのできる歪み補償装置を得る。

【解決手段】直流電源(30)と、直流電源から供給される直流電圧をパラメータとして変化させることで入力電力に対する利得特性および通過位相特性を調整する歪み補償回路(20)と、変調波信号の偶数次高調波、奇数次高調波、またはベースバンド変調波周波数のうち、少なくとも1つに対して振幅と位相を制御することで、歪み補償回路の能動素子からみた負荷インピーダンスを決定する整合回路(10)とを備え、整合回路は、歪み補償装置の入出力端子を結ぶ信号路に対して縦続に接続され、振幅と位相を制御することで、歪み補償装置の前段または後段に接続される増幅器の歪み成分と逆特性を持つ歪み成分を歪み補償回路から発生させる。

(もっと読む)

べき級数型ディジタルプリディストータとその歪補償制御方法

【課題】べき級数型ディジタルプリディストータのベクトル調整器係数および周波数特性補償器係数の更新において、歪成分を測定する3個の係数の値を従来より適切に設定し、1回の計算で歪成分のレベルを最小にする又は従来の方法より小さくする。

【解決手段】

歪成分の係数依存性を示す新たな二次関数f2(W)を最小二乗法により特定する際に用いる各係数W0,W1,W2を、更新前の歪成分の係数依存性を示す二次関数f1(W)に基づき、f1(W0)=f1(W2)=f1(W1)+Pの関係式を成立させる値として求める。

(もっと読む)

電流センサを用いた平面オーディオ増幅器出力インダクタ

第1回路基板の層上に形成された第1複数巻線と、第2回路基板上の層に形成された第2複数巻線とを備えた平面インダクタ構造を有するオーディオ増幅器。前記平面インダクタ構造は、センサ巻線をさらに備えてもよい。  (もっと読む)

(もっと読む)

算出装置、歪み補正装置、増幅装置および算出方法

【課題】増幅器の歪み特性の計算量を低減すること。

【解決手段】温度モデル算出部121、ゲートラグモデル算出部122、ドレインラグモデル算出部123、ゲートバイアス電圧モデル算出部124およびドレインバイアス電圧モデル算出部125は、信号に歪み特性を与える増幅器の複数の状態変数であってメモリ効果を有する各状態変数を算出する。特性算出部130は、算出された各状態変数に基づいて増幅器による信号の歪み特性を算出する。特性算出部130は、算出された歪み特性を出力する。

(もっと読む)

温度補償回路及び電力増幅器

【課題】高精度な温度補償を実現できる温度補償回路を提案する。

【解決手段】バイアス回路20は、絶対温度に関して正の線形温度特性を有するトランジスタTr1,Tr2,Tr3の電流又は電圧の温度変化を相殺するように、絶対温度に関して負の線形温度特性を有する基準電流をベースバイアス電流としてそれぞれのトランジスタTr1,Tr2,Tr3に供給するCTAT回路30と、CTAT回路30の温度特性とトランジスタTr1,Tr2,Tr3の温度特性とのずれを補償するための温度特性補償回路40を備える。

(もっと読む)

メモリ効果評価プログラム、メモリ効果評価方法及びメモリ効果評価装置

【課題】増幅器のメモリ効果を容易かつ事前に評価すること。

【解決手段】増幅器に周波数が異なる2つの信号が入力され、増幅器の出力波形の測定により、基本波、3次IMD及び5次IMDが取得される(ステップS10)。そして、測定により得られる基本波、3次IMD及び5次IMDから、増幅器のメモリ効果とは無関係のメモリレス非線形歪みに対応する係数が算出される(ステップS20)。続いて、増幅器のメモリ効果に起因するメモリ非線形歪みの特性を表す値が算出される(ステップS30)。これらの係数及び特性値の算出に際しては、メモリレス非線形歪みとメモリ非線形歪みとを区別して考慮した増幅器の歪み発生モデルを表す演算式が用いられる。

(もっと読む)

前置歪み補償回路及び電力増幅器のメモリ効果歪み補償方法

【課題】より少ないハードウエア構成で確実に電力増幅器におけるメモリ効果歪みを低減できる前置歪み補償回路及び電力増幅器のメモリ効果歪み補償方法を得る。

【解決手段】電力増幅器50のメモリ効果歪みを補償するメモリ効果歪み補償部20を電力増幅器50の前段に設け、またメモリ効果歪み補償部20に与えるメモリ効果歪み補償係数C2を算出するメモリ効果歪み補償係数演算部40を設け、メモリ効果歪み補償部20は、メモリ効果歪み補償係数演算部40で算出されたメモリ効果歪み補償係数C2を格納するルックアップテーブルを有し、非線形歪み補償された変調波信号X2(t)の振幅成分を算出するとともに、算出した振幅成分を所定時間だけ遅延させた遅延成分を求め、求めた振幅成分とその遅延成分の差を計算して振幅成分の勾配を求め、求めた勾配に応じたメモリ効果歪み補償係数C2を非線形歪み補償された変調波信号X2(t)に加算する。

(もっと読む)

通信装置及び周波数補正方法

【課題】増幅器を備える通信装置とその通信相手装置との間の通信品質を向上することが可能な技術を提供する。

【解決手段】通信装置の送受信処理部10には、増幅器20、補正情報記憶部64及び周波数補正部601が設けられている。補正情報記憶部64は、増幅器20の過渡応答における、当該増幅器20の出力信号の周波数偏差を補正するための補正情報を記憶する。周波数補正部601は、補正情報記憶部64が記憶する補正情報に基づいて、増幅器20への入力信号の周波数を補正する。

(もっと読む)

増幅器

【課題】単相増幅器において、出力信号に含まれる2次歪み成分を除去する。

【解決手段】増幅器は、第1の導電型の半導体で形成され第1の出力電流ΔI1を出力する第1のMOSトランジスタNM12と、前記第1の導電型の半導体で形成される第2のMOSトランジスタNM13と、第2の導電型の半導体で形成され第2の出力電流ΔI2を出力する第3のMOSトランジスタPM12と、前記第1の出力電流ΔI1と前記第2の出力電流ΔI2との差電流により設定される負荷電流に応じて出力信号ΔIR1を生成する負荷抵抗RL1とを備える。

(もっと読む)

増幅装置とこれを備えた無線送信装置、及び、増幅装置の利得調整方法

【課題】 戻り系アナログ回路4の利得が変動してもこれを補正できるようにして、DPD20による歪補償処理を正確に行える増幅装置1を提供する。

【解決手段】 本発明は、増幅器11と、この増幅器11の歪補償処理を行うデジタルプリディストータ(DPD)20とを備えた増幅装置1に関する。この増幅装置1は、増幅器11を含む送信系アナログ回路3と、アッテネータ15を含む戻り系アナログ回路4と、増幅器11の出力電力を測定する電力測定回路16と、電力測定回路16の測定値に基づいて、戻り系アナログ回路4の利得Grxの変化量ΔGrxを算出する変化量算出部27とを備えている。

(もっと読む)

レベルシフト回路及びそれを用いた発振器

【課題】 出力波形の割れや抜けを無くし、回路の誤動作が防止される低電圧動作のレベルシフト回路を提供する。

【解決手段】 レベルシフト回路は、電源端子VDDにソースを接続した第1のPMOSトランジスタP1と、接地端子GNDにソースを接続したNMOSトランジスタN1と、PMOSP1のドレインとNMOSN1のドレインとの接続点に接続された出力端子OUTと、NMOSN1のゲートに接続された入力端子INと、電源端子VDDにソースを接続し、PMOSP1のゲートにドレイン及びゲートを接続し、このドレインを第2の抵抗R2を介して接地端子GNDに接続した第2のPMOSトランジスタP2とを有し、PMOSP1及びP2は、カレントミラー回路を構成している。レベルシフト回路の出力波形の割れや抜けが無くなって誤動作を防止することが可能になる。

(もっと読む)

信号処理回路とこの回路を有する通信装置

【課題】 電力増幅回路5のパワーアンプ16の電力効率をより確実に向上することができる信号処理回路9を提供する。

【解決手段】 本発明は、変調波信号を増幅する電力増幅回路5に含まれるパワーアンプ16の電力効率を向上させるための信号処理回路9に関する。この回路9は、パワーアンプ16の出力電力を増加方向にシフトさせるための、変調波信号のIQベースバンド信号に対する調整信号ΔI,ΔQを生成する信号生成部(補正信号算出部20)と、生成された調整信号ΔI,ΔQをIQベースバンド信号に重畳する信号入力部(加減算器25,26)とを備える。

(もっと読む)

誘導コモンモード減結合のあるプッシュプル増幅器

増幅すべき入力信号(e)を出力信号(a)に増幅するためのプッシュプル増幅器が一つの第1の及び一つの第2の増幅素子(1、1’)有する。前記2つの増幅素子(1、1’)のそれぞれが一つの電流放出電極(2、2’)、一つの集電電極(3、3’)、及び一つの電流制御電極(4、4’)を有する。前記増幅素子(1、1’)の前記電流制御電極(4、4’)に、それぞれの入力端子(6、6’)を介して、及び、それぞれの前記入力端子(6、6’)とそれぞれの前記電流制御電極(4、4’)との間に配置されたそれぞれの入力インダクタンス(5、5’)を介して、前記入力信号(e)が供給される。前記集電電極(3、3’)は、それぞれの供給インダクタンス(7、7’)を介して一つの共通の供給電圧(V+)に接続される。前記増幅素子(1、1’)の前記電流放出電極(2、2’)は、それぞれのコンデンサ(8、8’)を介してそれぞれもう一方の前記増幅素子(1’、1)の前記集電電極(3’、3)に接続される。前記電流放出電極(2、2’)は、前記出力信号(a)をピックアップ可能である出力端子(9、9’)に接続される。前記電流放出電極(2、2’)は、それぞれの出力インダクタンス(10、10’)を介して基準電位に接続されている。前記増幅素子(1、1’)の前記供給インダクタンス(7、7’)は、それぞれもう一方の前記増幅素子(1’、1)の前記入力インダクタンス(5’、5)及び前記出力インダクタンス(10’、10)に誘導結合される。  (もっと読む)

(もっと読む)

高周波電力増幅器および歪補償方法

【課題】高効率化の為に回路規模を大きくすることなく歪補償を行う高周波用電力増幅器、および歪補償方法を提供する。

【解決手段】カプラ2で分岐された入力信号の一方をカプラ4へ向けて出力し、他方を90°ハイブリッドの入力端子p1、他方を可変ATT6を介して歪み発生ダイオード11,12が接続される入力端子p2へ入力する。そして入力端子p3で位相調整を行い、出力端子p4から予歪を与える歪補償信号を生成し、カプラ4で一方の信号と重畳して増幅器5へ供給する。ダイオード11は歪みを発生すると共に入力信号を検波した信号を可変ATTを制御する制御部9へ出力することにより、ダイオードが発生する歪み量を調整して増幅器5に対する歪補償を行う。

(もっと読む)

雑音除去を備える広帯域LNA

雑音除去を備える低雑音増幅器(LNA)を改善するための技術が説明される。LNAは、入力ステージ回路において生成された雑音を除去するために協働する第1及び第2の増幅器を含む。入力ステージ回路は、RF信号を受信し、第1のノード及び第2のノードによって特徴付けられる。第1の増幅器は、第1のノードにおける雑音電圧を、第1の増幅器の出力において第1の雑音電流に変換する。第2の増幅器は、第1の増幅器の出力に直接結合され、第2のノードにおける雑音電圧の関数として第2の増幅器によって生成された第2の雑音電流と第1の雑音電流とを加算することによって、雑音除去を提供する。提案された技術は、大きな交流結合コンデンサへのニーズを排除し、LNAによって占められるダイ・サイズを低減する。LNAの増幅ステージ間での交流結合コンデンサの排除によって、電流の再利用が可能になり、その結果電流の消費が低減される。  (もっと読む)

(もっと読む)

マルチバンド電力増幅器

【課題】 インピーダンス不整合をなくしたマルチバンド電力増幅器を提供する。

【解決手段】 マルチバンド電力増幅器11の増幅器12,13間には、これらを整合させる段間整合回路14を設ける。また、入力段の増幅器12の入力側に入力段整合回路15を設けると共に、出力段の増幅器13の出力側には出力段整合回路16を設ける。そして、制御回路17は、基地局BSからの周波数設定情報Spによって第1,第2の送信信号TX1,TX2の通信周波数f11〜f1m,f21〜f2nを特定し、この特定した通信周波数f11〜f1m,f21〜f2nに応じて段間整合回路14、入力段整合回路15および出力段整合回路16のインピーダンス値Zm,Zi,Zoを最適な値に調整する。

(もっと読む)

分布ドハティ電力増幅器

【課題】第1ドハティ電力増幅器と第2ドハティ電力増幅器とを分布構造で連結して広域特性を表して、直線性を改善させる電力増幅器を提供する。

【解決手段】分布ドハティ電力増幅器は、第1増幅器303と、第1増幅器303と並列に連結された第2増幅器305と、第1増幅器303の入力と第2増幅器305の入力との間に連結されて、第2増幅器305の入力を位相反転させる第1シフト部301aと、第1増幅器303の出力と第2増幅器305の出力との間に連結されて、第2増幅器305の出力を位相反転させる第2シフト部306aと、を備え、第1増幅器303と第2増幅器305とはドハティ増幅器であり、ドハティ増幅器は、並列に連結されたキャリア増幅器303b、305bとピーキング増幅器と303c、305cを備える。

(もっと読む)

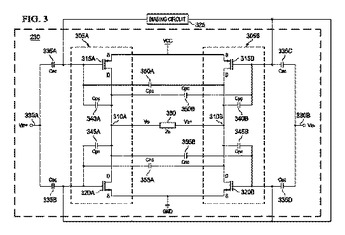

入力抵抗が改善され、コモンモード制御された増幅器

第1出力(Vo−)を規定し、第1入力端子(330A)に結合されるゲートを各トランジスタ(315A、320A)が有する第1対のトランジスタ(305A)、第2出力(Vo+)を規定し、第2入力端子(330B)に結合されるゲートを各トランジスタ(315B、320B)が有する第2対のトランジスタ(305B)、第2出力端子(310B)に及び第1対のトランジスタの第1トランジスタ(315A)のゲートに結合される第1キャパシタ(350A)、第2出力端子(310B)に及び第1対の第2トランジスタ(320A)のゲートに結合される第2キャパシタ(355A)、第1出力端子(310A)に及び第2対の第3トランジスタ(315B)のゲートに結合される第3キャパシタ(350B)、及び第1出力端子(310A)に及び第2対の第4トランジスタ(320B)のゲートに結合される第4キャパシタ(355B)を含む増幅器(230)。

(もっと読む)

(もっと読む)

プリディストーション方式の歪補償装置

【課題】増幅器で発生する歪をプリディストーション方式により補償する歪補償装置で、歪補償精度を向上させる。

【解決手段】メモリレスプリディストーション手段21〜23を有するとともに、メモリプリディストーション手段として、1段以上の遅延処理部、加算手段44、歪付与手段45を有する。遅延処理部のそれぞれは、入力信号のレベルの値を出力するか否かが切り替え可能である遅延選択手段32〜34、遅延選択手段から出力されたレベルの値に応じた補正値を出力するテーブル手段35、38、41、テーブル手段から出力された補正値をサンプル単位の所定時間だけ遅延させて出力する遅延手段36、39、42、テーブル手段から出力された補正値と遅延手段から出力された補正値との差分を検出して当該差分を加算手段44へ出力する差分検出手段37、40、43を備える。

(もっと読む)

電流電圧変換合成出力装置

【課題】負帰還回路を用いずにDAコンバーターの電流出力を電圧出力に高精度で変換しプッシュプル合成して高品質の信号出力を得る、構成簡易で安価な電流電圧変換合成出力装置。

【解決手段】夫々エミッタ入力・ベース電圧固定(接地)・コレクタ出力動作の第1、第2のトランジスタQ10、Q11と、第1〜第3のカレントミラー回路CM1〜CM3を組み合わせて用いる。 カレントミラー回路CM1、CM2は夫々トランジスタQ10、Q11の各コレクタ出力をカレントミラー電流出力する。カレントミラー回路CM3はカレントミラー回路CM1の出力をカレントミラー電流出力する。カレントミラー回路CM2、CM3の各出力の共通接続点とGND間に、抵抗とコンデンサの並列回路が接続される。DAコンバーターからの互いに極性が逆の電流出力信号を、各トランジスタQ10、Q11のエミッタに入力し、カレントミラー回路CM2、CM3の各出力の共通接続点に電流電圧変換された電圧出力信号を得る。

(もっと読む)

141 - 160 / 513

[ Back to top ]