Fターム[5J500AH19]の内容

Fターム[5J500AH19]の下位に属するFターム

ツェナーダイオード (97)

可変容量ダイオード、バラクタダイオード (26)

ガン、インパットダイオード

Fターム[5J500AH19]に分類される特許

1 - 20 / 837

スイッチングアンプ

コンデンサマイクロホン用インピーダンス変換器およびコンデンサマイクロホン

D級増幅器

電力増幅器

制御回路および位相変調器

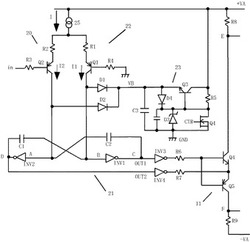

パルス幅変調回路およびスイッチングアンプ

【課題】 電源オフ状態に移行する際に、漏れ電流によって蓄積手段が充電され、2つの出力素子の入力が共にハイレベルになり、出力が共にローレベルになり、次に電源オン状態に移行する際に、パルス幅変調動作を開始することができないとい問題を解決でき、かつ、入力信号に正確に対応したパルス幅変調信号を出力することができるパルス幅変調回路を提供する。

【解決手段】 パルス幅変調回路20は、電源オン状態から電源オフ状態に移行する際に、オン状態に制御されることにより、漏れ電流の原因となる電源電圧V2を接地電位に瞬時に放電させ、0Vにさせるスイッチ手段Q4を備える。スイッチ手段Q4は、ダイオードD1、D2の各カソード側に接続されているので、電流I1、I2によってコンデンサC1、C2を充電する際に、コンデンサC1、C2から電気的に分離された状態になるので、C1、C2の充電に誤差を与えない。

(もっと読む)

電源回路

【課題】 広帯域無線通信を行う送信機に用いられ、電源変換効率を向上させると共に、電圧レベル切替の遷移時間の影響を低減し、出力信号の歪特性を改善することができる電源回路を提供する。

【解決手段】 入力信号をプッシュプル増幅方式で増幅するプッシュプル増幅部と、制御信号によりプッシュプル増幅部に提供する電源電圧の電圧レベルを可変とする可変電源部と、入力信号に基づいて電源電圧の電圧レベルを制御する制御信号を出力するスイッチ制御部83′と、入力信号を特定の時間遅延させるタイミング制御部121を備え、スイッチ制御部83′が、制御信号の立ち上げの場合に、タイミング制御部121での遅延時間に対して電圧レベル切り替えの遷移時間に応じた早いタイミングで制御信号を立ち上げ、立ち下げの場合には遅延時間のタイミングで立ち下げる電源回路としている。

(もっと読む)

トランスインピーダンスアンプ

【課題】入力電流の大きさに応じた量の電流を入力電流から分流することによりダイナミックレンジが拡大されたトランスインピーダンスアンプ(TIA)において、入力インピーダンスの変化を低減する。

【解決手段】TIA10は、光電流Iinの大きさに応じた出力電圧Voutを生成する。TIA10は、光電流Iinを出力電圧Voutに変換する利得可変増幅回路12と、光電流Iinが大きいほど大きな電流Icdを光電流Iinから分流する分流回路14と、光電流Iinが大きいほど利得可変増幅回路12の利得を小さくする利得調整回路20とを備える。

(もっと読む)

スイッチング回路及び包絡線信号増幅器

【課題】複数のスイッチング素子にて増幅したPWM信号を低損失で合成し、変調信号を復調することが可能なスイッチング回路、及び該スイッチング回路を備える包絡線信号増幅器を提供する。

【解決手段】本発明の一実施形態のスイッチング回路33は、N個(Nは2以上の整数)のトランジスタM1〜Mnのスイッチングを制御するための各制御端子をN−1個のコイルL1を介して縦続接続する接続回路と、一端が直流電源に電気的に接続されるコイルL2の他端及びトランジスタM1〜Mnの各一端の間に各別に接続されたコイルL3とを備え、接続回路の入力端子に入力されるPWM信号にて、スイッチング素子M1〜Mnを順次スイッチングさせるようにしてある。また、スイッチング回路33は、コイルL2の一端側又は他端側に縦続接続されるように挿入されたトランジスタM0を更に備える。

(もっと読む)

増幅回路

【課題】ノイズフィギュアの劣化を抑制しつつ、過入力信号を調整可能な上限電圧および下限電圧の範囲内に制限する。

【解決手段】入力トランジスタと、第1端が前記入力トランジスタのゲートに接続され、第2端がバイアス電圧に接続される抵抗素子と、前記入力トランジスタのゲートに接続され、前記入力トランジスタのゲートへの入力を、前記バイアス電圧を基準とする(調整可能な)上限電圧および下限電圧の範囲内に制限する保護回路と、を備える、増幅回路。

(もっと読む)

増幅回路および受光回路

【課題】回路の小型化を図ること。

【解決手段】増幅回路100は、パッド111と、TIA150と、オンチップインダクタ130と、シャント容量140と、を1つのチップに備えている。パッド111には電流信号が入力される。TIA150は、入力された電流信号を電圧信号に変換して出力する。オンチップインダクタ130は、パッド111とTIA150との間に直列に接続されている。シャント容量140は、一端がオンチップインダクタ130とTIA150との間に接続され、他端がグランドに接続されている。

(もっと読む)

出力回路及びそれを備えた増幅器

【課題】出力波形に付加される遅延の増大を抑制することが可能な出力回路を提供すること。

【解決手段】本発明にかかる出力回路は、高電位側電源端子と外部出力端子Voutとの間に設けられ、電源電圧VDD〜接地電圧VSS間の電圧範囲を振幅する一対の増幅信号の一方に基づいてソース−ドレイン間に流れる電流が制御される出力トランジスタMP11と、低電位側電源端子と外部出力端子Voutとの間に設けられ、一対の増幅信号の他方に基づいてソース−ドレイン間に流れる電流が制御される出力トランジスタMN11と、電源電圧VDDより低く接地電圧VSSより高い中間電圧VMLが供給されている低電位側電源端子と、出力トランジスタMP11のゲートと、の間に設けられ、出力トランジスタMP11のゲート電圧と中間電圧VMLとの電圧差に基づいて出力トランジスタMP11のゲートをクランプするクランプ用トランジスタMP12と、を備える。

(もっと読む)

送信増幅器

【課題】低ひずみ、低雑音、且つ小形な送信増幅器を得る。

【解決手段】多段接続した増幅器のうちの少なくとも1段以上に、バイポーラトランジスタ3のコレクタ電極とベース電極との間に接続された抵抗9を備え、出力電源10からインダクタ8および抵抗9を介してバイポーラトランジスタ3のベース電極に入力バイアスを供給する増幅器を備える。

バイポーラトランジスタ3の動作条件を決める入力バイアスを、抵抗9と出力電源10とにより決定するので、バイアス回路によるひずみがバイポーラトランジスタ3に重畳されないため、低雑音な送信増幅器を実現することができる。

また、入力バイアスを供給するためだけにインダクタを設ける必要がないため、小形な送信増幅器を実現することができる。

(もっと読む)

電力増幅回路

【課題】電力増幅回路の利得の温度依存性を抑制し、温度補償回路を有するバイアス回路を備えた電力増幅回路を提供する。

【解決手段】ドレインが高電位に接続され、ソースが接地された増幅用トランジスタを備え、ソースが接地され増幅用トランジスタGTrのゲートにゲートが接続されたカレントミラートランジスタCMTrによって増幅用トランジスタのバイアス電流を制御する電力増幅回路であって、アノードが制御電源端子に接続された第1のダイオードD1と、アノードが第1のダイオードD1のカソードに結合され、カソードがカレントミラートランジスタCMTrのドレインに接続された第2のダイオードD2と、一方の端子が第2のダイオードD2のカソードに接続され他方の端子が接地された第1の抵抗素子R1と、第2のダイオードD2と並列接続された第2の抵抗素子R2とを備える。

(もっと読む)

半導体集積回路、それを備えた受信装置及び無線通信端末

【課題】増幅回路を速やかに正常動作に復帰させることが可能な半導体集積回路を提供すること。

【解決手段】本発明にかかる半導体集積回路は、容量素子C1T,C1Bを介してそれぞれ供給される第1及び第2電圧信号の電位差を増幅し、第1及び第2増幅信号を出力する全差動増幅回路OPA1と、第1増幅信号を全差動増幅回路OPA1の反転入力端子に帰還する抵抗素子RFBTと、第2増幅信号を全差動増幅回路OPA1の非反転入力端子に帰還する抵抗素子RFBBと、所定電圧VBを生成する電圧生成部50と、電圧生成部50によって生成された所定電圧VBを、全差動増幅回路OPA1のそれぞれの入力端子に伝達する抵抗素子RBT,RBBと、を備える。

(もっと読む)

基準電圧発生回路

【課題】小規模の付加回路により、基準電圧の温度特性を簡易な調整によって十分に改善することができる基準電圧発生回路を提供する

【解決手段】バイポーラトランジスタ106、バイポーラトランジスタ106と並列に接続されるバイポーラトランジスタ107、バイポーラトランジスタ107のエミッタに一端が接続される抵抗素子104、バイポーラトランジスタ106のベース電位と、バイポーラトランジスタ107のベース電位との差分によって生じる差電圧を発生させる抵抗素子109、バイポーラトランジスタ106のエミッタ電位と抵抗素子104の他端の電位とが等しくなるように動作する演算増幅器105によって基準電圧発生回路を構成し、抵抗素子109が生成する差電圧が、温度によって変化する。

(もっと読む)

演算増幅器

【課題】消費電流の増加や最低動作電源電圧の上昇などを招くことなく出力位相反転を防止する。

【解決手段】入力部10の反転入力端子100と第2のトランジスタ2のコレクタとが第1のダ入力部用イオード11を介して、非反転入力端子200と第1のトランジスタ1のコレクタとが第2の入力部用ダイオード12を介して、それぞれ接続される一方、第9のトランジスタ9のエミッタと第3の負荷35の相互の接続点と反転入力端子100とが第5のダイオード15を介して、第9のトランジスタ9のエミッタと第3の負荷35の相互の接続点と非反転入力端子200とが第6のダイオード16を介して、それぞれ接続されて、消費電流の増加や最低動作電源電圧の上昇などを招くことなく出力位相反転が防止されるようになっている。

(もっと読む)

半導体装置、電子装置、車両、及び過熱検出方法

【課題】過熱検出回路の検出温度がばらつくことを抑制する。

【解決手段】コンパレータ170には、第1抵抗110と第1定電流源120の間の電圧Aと、ダイオード130と第2定電流源140の間の電圧Bが入力される。第1リーク電流源150は、ドレインが第1抵抗110と第1定電流源120の間に接続されており、ソース及びゲート電極が第1定電流源120と第2配線104の間に接続されている。第2リーク電流源160は、ドレインが第1配線102とダイオード130の間に接続されており、ソース及びゲート電極がダイオード130と第2定電流源140の間に接続されている。

(もっと読む)

RFパルス信号生成用スイッチング回路、RFパルス信号生成回路、および物標探知装置

【課題】安定動作させながら、RFパルス信号の波形を高速に立ち下げることができるRFパルス信号生成用スイッチング回路を提供することにある。

【解決手段】ドレインスイッチング回路21は、n型からなる第1、第2、第3のFET211,212,213を備える。第1、第3のFET211,213のゲートには、制御パルスが印加され、ソースは接地されている。第1のFET211のドレインは、第2のFET212のゲートに接続し、第2のFET212のドレインには、駆動電圧Vdsが印加される。第2のFET212のソースと第3のFET213のドレインは接続され、接続点がパワーFET31のドレインに接続されている。第2のFET212のゲートソース間には、第2のFET212がオフ状態からオン状態へ遷移する際のゲート電圧を補償するための電荷を供給するコンデンサ215が接続されている。

(もっと読む)

電子回路およびその制御方法

【課題】ドレインアイドル電流のドリフトを直接補償すること。

【解決手段】入力信号が入力するゲートと、出力信号が出力するドレインとを有するFETを含む電子回路の制御方法であって、前記FETのゲートに前記入力信号が入力してからの時間t経過後における前記入力信号x(t)に対応するドレインアイドル電流の変化量ΔIdq(t)を算出するステップS10と、前記変化量ΔIdq(t)を補償するためのゲートバイアス電圧Vgを算出するステップS12と、前記ゲートバイアス電圧を前記FETのゲートに印加するステップS14と、を含むことを特徴とする電子回路の制御方法。

(もっと読む)

1 - 20 / 837

[ Back to top ]