Fターム[5J500AK17]の内容

Fターム[5J500AK17]に分類される特許

101 - 120 / 652

トランスミッタ、インタフェイス装置、車載通信システム

【課題】電源電圧の変動に起因する入力信号と出力信号のデューティばらつきを抑制する。

【解決手段】トランスミッタ10は、一端から充電電圧Vaが引き出されるコンデンサ105と、コンデンサ105の充電電流I1を生成する第1定電流源103と、コンデンサ103の放電電流I2を生成する第2定電流源104と、送信入力信号INの論理レベル、及び、充電電圧Vaと基準電圧Vrefとの比較結果に基づいて、コンデンサ105の充放電制御を行う充放電制御部(101、102、106)と、充電電圧Vaに応じてスルーレートが設定され、出力側電源電圧V2に応じて信号振幅が設定される送信出力信号OUTを生成する出力段(109〜116)と、出力側電源電圧V2に依存して基準電圧Vrefを変動させる基準電圧生成部107と、基準電圧Vrefに依存して充電電流I1及び放電電流I2の各電流値を変動させる定電流制御部108と、を有する。

(もっと読む)

信号発生器の保護回路

【課題】出力信号経路に過電流が流れた場合でも信号出力回路の破壊または劣化を防ぎ、信号出力回路を保護することが可能な信号発生器の保護回路を実現する。

【解決手段】クロック信号またはデジタル信号である信号出力回路からの出力信号をリレーを介して出力する信号発生器の保護回路において、電源と信号出力回路の電源端子の間に接続された電流検出用抵抗と、電流検出用抵抗の両端電圧を増幅して出力する増幅器と、増幅器からの電圧が予め定められた閾値を超えた場合に検出信号を出力する電圧検出判定回路と、電圧検出判定回路からの検出信号に応じてリレーを切断し、出力信号の経路を断つリレー制御回路とを備える。

(もっと読む)

バイアス制御増幅器

【課題】負帰還ループを有するバイアス制御増幅器において、従来の1重ループで構成される負帰還ループで補償しきれない各種劣化を抑圧し、バイアス制御増幅器全体として線形性とバックオフ効率の向上を図る。

【解決手段】入力信号を増幅する高出力増幅器4と、入力信号の包絡線成分に応じて高出力増幅器4へ供給される電源電圧を制御するエンベロープ増幅器5,6,7と、エンベロープ増幅器の出力をエンベロープ増幅器の入力に負帰還する第一の負帰還ループ8,9と、第一の負帰還ループの外側に設けられ、エンベロープ増幅器の出力を第一の負帰還ループの入力に負帰還する第二の負帰還ループ10,11,12とを備えている。

(もっと読む)

A/D変換器およびそれを使用した受信装置

【課題】A/D変換器を構成するサンプル/ホールド回路、コンパレータを低消費電力化すること。

【解決手段】アナログ入力信号をクロック信号に応答してサンプルしてホールドするサンプル/ホールド回路(SHC)とその回路からのホールド出力信号の信号レベルを弁別するコンパレータ(COP)を含む。コンパレータは、サンプル/ホールド回路からのホールド出力信号を増幅するプリアンプ(AMP)、プリアンプから生成される差動出力信号をラッチするラッチ回路(LCH)、プリアンプから生成される差動出力信号のレベル差に応答してプリアンプのバイアス電流の電流値を制御するバイアス制御回路(BCC)を含む。差動出力信号のレベル差が小さい時にはバイアス制御回路はプリアンプのバイアス電流を大きな電流値に制御して、差動出力信号のレベル差が大きい時にはバイアス制御回路はプリアンプのバイアス電流を小さな電流値に制御する。

(もっと読む)

飽和増幅回路

【課題】小さい振幅の入力信号に対しては、飽和増幅部が有するDCオフセットの影響をキャンセルし、大きい振幅の入力信号に対しては、オフセットの帰還量を制限して飽和増幅出力の品質低下を抑制することが可能な飽和増幅回路を提供する。

【解決手段】DCオフセットをキャンセルするためのオフセットキャンセル回路12を備えた多段の差動増幅器からなる飽和増幅回路であって、差動増幅器への入力信号の振幅を判定するレベル判定回路15を有し、該レベル判定回路により予め定められた値より大きい振幅の入力信号と判定された場合は、前記のオフセットキャンセル回路12の帰還機能を無効とする。

(もっと読む)

遅延回路及びその制御方法

【課題】入力信号に精度の高い遅延を付加することが可能な遅延回路及びその制御方法を提供する。

【解決手段】遅延回路は、入力信号1001の立ち上がり又は立ち下がりの遷移時刻を、位相の異なる複数のクロック信号に基づいて検出するエッジ検出回路1004と、入力信号の遷移時刻に対応するクロック信号に基づいて、検出された入力信号の遷移時刻から所定の遅延時間経過後に、入力信号の信号波形を再現して出力する出力信号生成部1015と、を備える。

(もっと読む)

ミュート制御装置

【課題】 電源回路とアンプ回路との間にミュート制御信号を送受信するための制御ケーブルを別途設けることなく、アンプ回路をミュート状態、ミュート解除状態に制御する。

【解決手段】 電源回路は、電源オン時から所定時間経過する迄の間は、第1電圧値の電源電圧を第1アンプ回路および前記第2アンプ回路に供給し、電源オン時から所定時間経過した後は、第2電圧値の電源電圧を前記第1アンプ回路および前記第2アンプ回路に供給する。第1アンプ回路および前記第2アンプ回路は、電源回路から第1電圧値の電源電圧が供給されたときには、ミュート状態になり、第2電圧値の電源電圧が供給されたときには、ミュート解除状態になる。

(もっと読む)

無線装置および無線装置の過熱防止方法

【課題】小型で安価な部品からなり、かつ、より安全性の高い送信パワーアンプの過電流・過熱保護対策が可能な無線装置を提供する。

【解決手段】情報を無線信号として送信するための送信パワーアンプ2の温度、電流値に基づき、スイッチ部11にて電源の電池1から送信パワーアンプ2に供給される電流をON/OFFする。電源の電池1とは異なる電源部15からの低電圧の電力で動作する制御部11を送信パワーアンプ2の近傍に配置し、制御部12内の温度センサ12bにて検知した送信パワーアンプ2の温度があらかじめ任意に設定した温度閾値を超えた場合、または、制御部12内の電流検出部12aにて検知した送信パワーアンプ2の電流値があらかじめ任意に設定した電流閾値を超えた場合、制御部12は、FET13、電流モニタ部14、制御端子16を介して、スイッチ部11をOFFに設定し、送信パワーアンプ2への電流供給を停止させる。

(もっと読む)

差動増幅回路、サンプルアンドホールド回路、及び、全差動増幅回路のスタートアップ制御方法

【課題】動作開始時に出力コモン電圧が異常な電圧に固定されることのない全差動増幅回路を提供する。

【解決手段】一対の差動信号入力端子と、一対の差動信号入力端子間の電圧を増幅して出力する一対の差動信号出力端子と、一対の差動信号出力端子の出力コモン電圧が一定の電圧範囲に収まるように制御する同相帰還回路と、出力コモン電圧が一定の電圧範囲外のときに、一対の差動信号入力端子に同相入力電圧範囲内の固定電圧を与えるスタートアップ回路と、を備える。

(もっと読む)

スイッチング回路のノイズ低減装置

【課題】ノイズ低減効果が大きく、小型化が可能なスイッチング回路のノイズ低減装置を提供する。

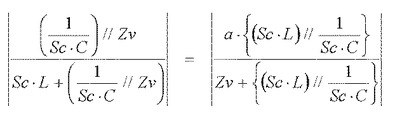

【解決手段】第1のスイッチングドライバの入力端に入力されるパルス信号と逆位相のパルス信号に基づいて動作する第2のスイッチングドライバと、一端が第2のスイッチングドライバの出力端に接続されるとともに他端がスイッチング回路の出力端子と接続されるインピーダンス素子とを具備し、インピーダンス素子のインピーダンス値Zvと、第1のコイルのインダクタンス値Lと、コンデンサの静電容量値Cと、第1及び第2のスイッチングドライバのスイッチング周波数fcとが、aを0以外の任意の定数として、(数3)の関係を満たす。 (もっと読む)

(もっと読む)

増幅回路、増幅回路のクリップ検出方法

【課題】クリップ発生の有無を正確に検出可能な増幅回路を提供する。

【解決手段】本発明に係るD級増幅回路100は、インダクタンス成分を有する負荷50が接続される出力端子Coutと、入力信号INに基づいて2値の駆動信号OUTPを生成し、その生成した駆動信号OUTPを出力端子Coutに対して供給する駆動部70と、駆動信号OUTPにクリップが発生しているか否かを検出するクリップ検出部40と、を備える。クリップ検出部40は、駆動信号OUTPの上限値を超える第1パルス、または、駆動信号OUTPの下限値を下回る第2パルスが、所定の時間長Txにわたって発生しない場合は、クリップの発生を検出する。

(もっと読む)

電源回路

【課題】比較的簡易な構成で、定電圧駆動と定電流駆動を所望に応じて選択可能な電源回路を提供する。

【解決手段】演算増幅器1の出力端子とグランドとの間に第1及び第2の抵抗器31,32が直列接続されて設けられ、演算増幅器1の非反転入力端子には、所定の基準電圧が印加され、演算増幅器1の出力端子には、外部からの信号により動作制御可能に構成されてなるバッファアンプ2が接続され、バッファアンプ2の出力端子とグランドとの間には、MOSトランジスタ11と第3の抵抗器33が順に直列接続されて設けられ、これらの接続が、切替制御回路4、及び、第1乃至第4のアナログスイッチ21〜24により切り替えられることで、定電圧駆動と定電流駆動が選択可能となっている。

(もっと読む)

シングルサプライD級アンプ

異常検出装置、保護装置、異常検出方法並びに保護装置用プログラム及び情報記録媒体

【課題】D級アンプにおいて、出力段のLPFの動作異常を確実に検出してスピーカを保護することが可能な異常検出装置を提供する。

【解決手段】スピーカ手段4から放音される音に対応するパルス状駆動信号Spwmを変換して変換信号Sdを生成し、当該生成された変換信号Sdをスピーカ手段4に出力する変換手段3の動作異常を検出する異常検出装置Sであって、変換手段3における変換信号Sdの出力端においてパルス状駆動信号Spwmが検出されるかを判定する判定手段2と、出力端においてパルス状駆動信号Spwmが検出されると判定されたとき、変換手段3の動作異常が発生したことを示す異常発生信号Sdtを生成する生成手段1と、を備える。

(もっと読む)

レール・ツー・レール入力電圧範囲を有する差動増幅器

半導体素子の駆動回路、および駆動回路を有する半導体装置

【課題】本発明は、ゲート−ソース間において所定電圧を超えると急峻な電流が流れるダイオード特性を示す半導体素子の高負荷時の消費電力低減および駆動回路の低負荷時の損失低減を図るだけでなく、過電圧、過電流、過消費電力を防止する保護機能と、当該半導体素子の損失を低減する機能を有する駆動回路の提供を目的とする。

【解決手段】駆動回路におけるゲート制御手段(2,12,22,32)は、ゲート−ソース間において所定電圧を超えると急峻な電流が流れるダイオード特性を示す半導体素子(1)の動作状態を検出する動作状態検出手段(4,5,6)から入力された半導体素子の動作状態を示す信号に応じて、半導体素子のゲートに供給する電圧または電流を制御するよう構成されている。

(もっと読む)

電源装置及び電源装置制御方法

【課題】効率よく電力消費を低減すること。

【解決手段】検出部2は、送信信号のピークを検出する。決定部3は、検出部2によって検出された送信信号のピークに対応する電圧値と、自装置が出力する可変電圧の変化率とに基づいて、当該ピークに対する可変電圧の変化を開始する時期を決定する。生成部4は、決定部3によって決定された時期に電圧の変化を開始させるための可変電圧制御信号を生成する。出力部5は、生成部4によって生成された可変電圧制御信号に基づいて電圧を出力する。

(もっと読む)

スイッチドキャパシタ回路のためのディスクリートタイムオペレーショナルトランスコンダクタンス増幅器

差動増幅回路及びA/D変換器

【課題】電源電圧が比較的小さい場合においても、性能劣化を起こさず、かつオーバードライブリカバリ可能な差動増幅回路を得る。

【解決手段】第1の出力部であるノードN1と電源Vddとの間にPMOSトランジスタMP1及びMP3が互いに並列に介挿され、第2の出力部であるノードN2と電源Vddとの間にPMOSトランジスタMP2及びMP4が互いに並列に介挿される。レプリカ回路4及びコンパレータ5によって、入力電圧Vinと基準電圧Vrefとの入力電位差が“0”のバランス状態時の出力電圧Voutp及びVoutnは共に基準出力コモン電圧Voutcm_idealに設定される。電源電圧Vddと出力コモン電圧Voutcmとの電位差がダイオード接続されたPMOSトランジスタMP1及びMP2の閾値電圧Vthよりも低い値となるように、レプリカ回路4の基準出力コモン電圧Voutcm_idealを設定する。

(もっと読む)

デジタルアンプ、DA変換器、増幅方法、変換方法

【課題】入力信号を変調する変調回路の構成を変更することなく、D級増幅回路における増幅歪を抑制することのできるデジタルアンプを実現する。

【解決手段】増幅された2つのパルス信号#5aおよび#5bの差信号によって負荷を差動駆動するD級アンプ(デジタルアンプ)1は、2つのパルス信号#2aおよび#2bに対して、上記D級増幅回路における増幅歪を低減させるための制御信号#rを加算する変換回路12を備えており、変換回路12は、2つのパルス信号#2aおよび#2bが何れもローレベルである期間において、2つのパルス信号#2aおよび#2bの各々に対して、同一波形の制御信号#rを同期して加算する。

(もっと読む)

101 - 120 / 652

[ Back to top ]