Fターム[5J500AK17]の内容

Fターム[5J500AK17]に分類される特許

121 - 140 / 652

増幅器

【課題】バッテリ電圧の瞬時減電が発生した場合においても、ポップノイズの発生を防止しつつ、音切れの発生時間を短縮する。

【解決手段】リップル制御回路5は、電源電圧Vbatが下がり電源電圧Vbatとリップル端子電圧Rippleとの電位差がヘッドルーム電圧Vhrに達した場合、電源電圧Vbatが一定のレベルを上回っている場合、リップル端子電圧Rippleが閾値Vth1に達するまで入力カップリング容量C1、ACカップリング容量C3およびリップル容量C2を放電させ、電源電圧Vbatが一定のレベル以下の場合、リップル端子電圧Rippleが閾値Vth2に達するまで入力カップリング容量C1、ACカップリング容量C3およびリップル容量C2を放電させる。

(もっと読む)

温度補償回路及び電力増幅器

【課題】高精度な温度補償を実現できる温度補償回路を提案する。

【解決手段】バイアス回路20は、絶対温度に関して正の線形温度特性を有するトランジスタTr1,Tr2,Tr3の電流又は電圧の温度変化を相殺するように、絶対温度に関して負の線形温度特性を有する基準電流をベースバイアス電流としてそれぞれのトランジスタTr1,Tr2,Tr3に供給するCTAT回路30と、CTAT回路30の温度特性とトランジスタTr1,Tr2,Tr3の温度特性とのずれを補償するための温度特性補償回路40を備える。

(もっと読む)

電流源、電流源回路、およびこの電流源回路の使用

【課題】MOS技術を使ったパワー素子を用いなくても、正確な負荷電流を供給しうる電流源を提供する。

【解決手段】電流源10が、制御端子および制御パスを有するバイポーラトランジスタ1と、バイポーラトランジスタ1の制御パス上にあって、電気負荷D1と接続される第1の端子と、抵抗器4経由で基準電源端子と接続される第2の端子と、バイポーラトランジスタ1の制御端子に接続され、この制御端子に送られる制御電流を測定する測定装置2と、バイポーラトランジスタ1の制御電流が制御パス上に位置する第1の端子において補償されるように、測定装置2およびバイポーラトランジスタ1に接続された補償電流源3とを備える。

(もっと読む)

増幅装置

【課題】高周波電力増幅器の電源電圧を制御した場合の増幅装置全体の利得(増幅装置の利得)を一定にすることにより、高効率に動作させることができるとともに、高周波電力増幅器の非線形歪みを低減することができる増幅装置を得る。

【解決手段】入力された信号を増幅して出力する増幅装置であって、印加される電源電圧に基づいて入力信号を増幅する高周波電力増幅器と、入力信号の包絡線成分を検出する包絡線検出手段と、包絡線成分に応じた電源電圧を高周波電力増幅器に印加する電圧印加手段と、増幅装置の利得が一定となるように、高周波電力増幅器への入力を制御する制御手段とを備えたものである。

(もっと読む)

検出回路とそれを用いた半導体装置

【課題】本発明は、安価かつ容易に歪特性の劣化を抑制できる検出回路とそれを用いた半導体装置を提供することを目的とする。

【解決手段】電力増幅器とアンテナの間に配置された方向性結合器の結合線路両端の信号を用いて、該電力増幅器の歪特性劣化を検出する回路であって、該結合線路の結合端子の電力を移相および減衰する移相・減衰器と、該移相・減衰器からの出力電力と、該結合線路のアイソレーション端子の電力の差分を出力する手段と、該差分をDC信号に変換する検波回路と、該DC信号の電圧レベルが所定値よりも高いかを判定する比較回路とを備える。そして、該移相・減衰器は、該電力増幅器の歪特性が劣化する該アンテナ端の負荷状態において、該移相・減衰器が出力する信号の位相が該アイソレーション端子の信号の位相と180°の位相差になるように該結合端子の電力を移相することを特徴とする。

(もっと読む)

アナログ高速増幅器及びそれを使用するイメージセンサ

【課題】消費電力の増加を抑制しつつスルーレートを向上させる一方飽和画素の影響を低減し、高い線形性を実現することができるアナログ高速増幅器を提供する。

【解決手段】本発明に係るアナログ高速増幅器は、所定のクロック周期で独立したレベルの信号を入力し増幅するアナログ高速増幅器において、増幅部本体と、前記クロック周期をサンプリング期間とリセット期間に分割し、前記信号を前記サンプリング期間中に前記増幅部本体に入力するサンプリング手段と、前記リセット期間中に、前記増幅部本体の出力を所定のリセット電位にリセットするリセット手段と、前記サンプリング期間のうち、前記サンプリング期間の開始時点から前記サンプリング期間よりも短い所定の期間を電流増加期間とし、前記電流増加期間中は、前記増幅部本体に供給する動作電流を前記電流増加期間以外の期間よりも増加させる、動作電流制御手段と、を備えたことを特徴とする。

(もっと読む)

信号補償装置及び通信装置

【課題】例えばフィルタの設計に必要な高度な専門知識を必要とすることなく、フィルタを含む増幅器を通信装置に対して適用する。

【解決手段】信号補償装置(200)は、(i)入力される信号に対して、可変な帯域設定値に基づく帯域制限を行うと共に、(ii)帯域制限が行われた信号を増幅手段(100)に対して出力する帯域制限手段(205、206)と、増幅手段の出力の一部を帰還信号として帯域制限手段に負帰還する帰還手段(210)と、帰還信号のうち、(i)帯域設定値を小さくするにつれて信号レベルが小さくなる特性を有する第1信号成分及び(ii)帯域設定値を小さくするにつれて信号レベルが大きくなる特性を有する第2信号成分の夫々の信号レベルを測定する測定手段(223、224)と、第1信号成分及び第2信号成分の夫々の信号レベルに基づいて帯域設定値を調整する調整手段(227)とを備える。

(もっと読む)

オペアンプ回路

【課題】差動入力信号の伝達遅延時間を小さくすることができるオペアンプ回路を提供することである。

【解決手段】本発明にかかるオペアンプ回路10は、第1の差動対を構成するトランジスタ11、12を備える第1の差動入力部1と、第1の差動対を構成するトランジスタ11、12よりもトランジスタサイズが大きい第2の差動対を構成するトランジスタ21、22を備える第2の差動入力部2と、第1および第2の差動入力部1、2からの出力に応じて信号を生成する中間段3と、中間段3で生成された信号に応じて出力信号を生成する出力段トランジスタMP1、MN1を備えた出力段8と、中間段3で生成された信号に応じて、第1の差動入力部1を使用する場合または第1の差動入力部1および第2の差動入力部2を使用する場合のいずれかを選択する差動入力部選択回路と、を有する。

(もっと読む)

電流源回路及びそれを用いた遅延回路及び発振回路

【課題】簡単な構成でデプレッション型MOSトランジスタの温度特性を補償する電流源回路を提供する。

【解決手段】2つのエンハンスメント型MOSトランジスタQ2、Q3から構成されたカレントミラー回路と、前記カレントミラー回路の入力側の前記エンハンスメント型MOSトランジスタQ2のドレインに接続され、定電流源として機能するデプレッション型MOSトランジスタQ1と、前記カレントミラー回路の入力側の前記エンハンスメント型MOSトランジスタQ2のソースに接続された負の温度特性を有する抵抗と、を含むことを特徴とする。

(もっと読む)

半導体装置及びオフセット補正方法

【課題】コンパレータの比較速度の悪化や消費電力の増加を抑えて入力信号に加わるオフセットを補正する。

【解決手段】比較回路部11において、比較対象の2つの差動入力信号VIP,VIMを入力するトランジスタNM1,NM2のバックゲートBG1,BG2のそれぞれに可変容量C1,C2と抵抗R1,R2を並列に接続し、可変容量C1,C2と抵抗R1,R2の少なくとも一方の値を可変することで差動入力信号VIP,VIMに加わるオフセットを補正する。

(もっと読む)

電流ロック回路

【課題】異なる電流源の電流をロックする。

【解決手段】電流ロック回路1は、基準電流の電流値Irefと調整対象の電流である調整対象電流の電流値Iout2とを比較して、調整対象電流の電流値Iout2が基準電流の電流値Irefの所定倍となるように制御信号を生成する電流比較回路10と、電流比較回路10が生成した制御信号LIMIT_TOP,LIMIT_BTMに基づき調整対象電流の電流値Iout2を調整するチャージポンプ回路50及びV/Iコンバーター60とを備える。

(もっと読む)

受信回路

【課題】増幅率を損ねることなく同相入力範囲を拡大することができる受信回路を提供する。

【解決手段】受信回路は、第1の抵抗R3と第2の抵抗R4との抵抗比に基づき差動信号の一方の信号BPを分圧した第1の入力信号を出力する第1の分圧回路10と、第3の抵抗R5と第4の抵抗R6との抵抗比に基づき差動信号の他方の信号BMを分圧した第2の入力信号を出力する第2の分圧回路11と、第1、第2の入力信号を増幅して出力する差動増幅器12と、差動信号の同相電圧Vcmを検出する同相電圧検出回路13と、同相電圧Vcmに基づきバイアス電圧Vbの電圧値を切り替えるバイアス電圧切替回路14と、を有する。

(もっと読む)

ポーラフィードバックを備える線形RF増幅器

【課題】RF信号の線形増幅のための効率的なシステムを提供する。

【解決手段】RF信号の電力増幅のためのシステム100はポーラフィードバック制御を有する。システムは、フィードバック補正をされた制御信号に基づいてRF信号を変調するよう構成されるフィードバック制御型変調器110を有する。変調器110は、更に、変調RF信号を生成するよう構成される。システムは、また、フィードバック位相制御信号に基づいて変調RF信号の位相を補正するよう構成される位相シフタと、変調器及び/又は位相シフタと通信を行う電力増幅器112とを有する。増幅器112は、変調RF信号を増幅して増幅RF出力信号を生成するよう構成される。システムは、また、フィードバック補正をされた制御信号及び/又はフィードバック位相制御信号を含むポーラフィードバック信号を生成するよう構成されるフィードバックネットワーク116を有する。

(もっと読む)

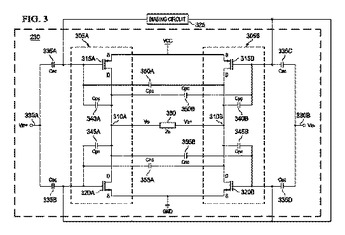

入力抵抗が改善され、コモンモード制御された増幅器

第1出力(Vo−)を規定し、第1入力端子(330A)に結合されるゲートを各トランジスタ(315A、320A)が有する第1対のトランジスタ(305A)、第2出力(Vo+)を規定し、第2入力端子(330B)に結合されるゲートを各トランジスタ(315B、320B)が有する第2対のトランジスタ(305B)、第2出力端子(310B)に及び第1対のトランジスタの第1トランジスタ(315A)のゲートに結合される第1キャパシタ(350A)、第2出力端子(310B)に及び第1対の第2トランジスタ(320A)のゲートに結合される第2キャパシタ(355A)、第1出力端子(310A)に及び第2対の第3トランジスタ(315B)のゲートに結合される第3キャパシタ(350B)、及び第1出力端子(310A)に及び第2対の第4トランジスタ(320B)のゲートに結合される第4キャパシタ(355B)を含む増幅器(230)。

(もっと読む)

(もっと読む)

演算増幅器

【課題】ジッタ特性に優れる演算増幅器を提供すること。

【解決手段】各ゲートに差動入力信号が入力される第1PMOSトランジスタ対PM6、PM7を有する第1差動増幅器PAと、各ゲートに差動入力信号が入力される第1NMOSトランジスタ対NM13、NM14を有する第2差動増幅器NAと、差動入力信号の同相成分を検出する同相成分検出部1と、同相成分から高周波成分を除去する高周波成分除去部2と、高周波成分が除去された同相成分に基づいて、差動入力信号のコモンモード電圧が第1基準電圧より高い場合、第1差動増幅器PAの動作を停止し、コモンモード電圧が第2基準電圧より低い場合(ただし、当該第2基準電圧は前記第1基準電圧より低い)、第2差動増幅器NAの動作を停止するための制御信号を発生する制御信号発生部3と、を備えた演算増幅器。

(もっと読む)

誤差増幅器

【課題】誤差増幅器における、受動素子の定数のばらつきに起因する帰還回路の定数のばらつきを抑制する。

【解決手段】誤差増幅器における帰還回路の定数が、受動素子の定数だけでなく、能動素子の利得にも依存して決定される構成にする。この誤差増幅器は、能動素子である電圧電流変換器20を含む構成である。また、第1の端子11、第2の端子13、オペアンプ16、第1の抵抗R1、第2の抵抗R2、第1乃至第5のトランジスタ、第1の電流源14および第2の電流源15を一体の集積回路とし、コンデンサC1を外付けしてもよい。

(もっと読む)

差動増幅回路および無線受信機

【課題】消費電流の増大を抑制しつつ、差動増幅回路の線形性と利得の両立を図る。

【解決手段】差動信号Vin、Vinbの一方が入力されるソースフォロア回路を構成する電界効果トランジスタM11と、ソースフォロア回路に直列接続され、差動信号Vin、Vinbの他方が入力されるソース接地回路を構成する電界効果トランジスタM12とを備える。

(もっと読む)

バッファ回路

【課題】 消費電力を抑制することができるバッファ回路を提供すること。

【解決手段】 検波回路11が、入力信号IDのレベルに応じた入力レベル判定信号SWを制御回路9へ供給し、入力信号IDの振幅が比較的小さい場合には、制御回路9が、低レベル入力用回路6を選択して、トータルゲインを十分に上げ、入力信号IDの振幅が比較的大きい場合には、制御回路9が、高レベル入力用回路5を選択して、無用な消費電流の増大を抑制する。

(もっと読む)

補正ユニットを有するシステム及びその補正方法

【課題】

バイナリ探索で探索される補正値が最適値になる補正ユニットを有するシステム及びその補正方法を提供する

【解決手段】

システムは,被補正ユニットと,その出力が基準値により近づくような補正値をバイナリ探索し,補正値を被補正ユニットにフィードバックする補正ユニットを有し,補正ユニットは,バイナリ探索により探索された第1の補正値に対応する被補正ユニットの第1の出力と,第1の補正値に隣接する第2の補正値に対応する補正ユニットの出力であり且つ第1の出力とは基準値との大小関係が逆になる第2の出力とを比較し,基準値により近い第1または第2の出力に対応する第1または第2の補正値を選択する追加判定を行い,当該選択した補正値を被補正ユニットにフィードバックする。

(もっと読む)

プラグの種別を判定する方法及びプラグ判定回路

【課題】ヘッドフォンプラグ又はライン出力プラグの接続時において、ポップノイズの低減及び除去を図りつついずれかのプラグが接続されているかを判別することができる方法及びプラグ判定回路を提供する。

【解決手段】ジャック端子に接続されたプラグの負荷抵抗の大きさに応じてプラグの種別を判定する方法であって、負荷抵抗に第1方向の電流を供給する第1方向電流供給ステップと、負荷抵抗に生じた電圧を所定の参照電圧と比較して、プラグの種別を判定するステップと、負荷抵抗に第1方向とは異なる第2方向の電流を供給する第2方向電流供給ステップと、を有すること。

(もっと読む)

121 - 140 / 652

[ Back to top ]