Fターム[5J500AK35]の内容

増幅器一般 (93,357) | 回路要素 (18,409) | デジタル回路(パルス回路) (1,577) | カウンタ (85)

Fターム[5J500AK35]に分類される特許

1 - 20 / 85

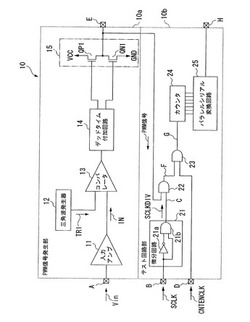

デジタルアンプ及びデジタルアンプのテスト方法

【課題】安価な試験装置を用いても、PWM信号のパルス幅を測定可能にするデジタルアンプを提供する。

【解決手段】PWM信号のキャリア周期とPWM信号のパルス幅を測定する際の目標分解能との和に基づく周期であるサンプリングクロックSCLKの第1の論理から第2の論理への遷移に応じて発生させたサンプリング信号SCLKDIV(微分回路21の出力)と、PWM信号との論理積の結果(アンド回路22の出力)をカウントし、カウント結果に基づいてPWM信号のパルス幅を示すカウント値を出力するテスト回路部10bを設けたことを特徴とする。

(もっと読む)

歪補償装置

【課題】 FDD方式及びTDD方式のいずれの通信方式にも適用することができ、有効データ区間を精度良く反映した遅延調整を実現する歪補償装置を提供する。

【解決手段】 歪補償装置は、歪補償部1が送信信号に歪補償テーブルを用いて歪補償を行い、遅延調整部2が歪補償前の送信信号と歪補償後の送信信号の帰還信号との遅延を調整し、誤差演算部3が遅延調整された送信信号と帰還信号との遅延誤差が小さくなるように歪補償テーブルを更新する。そして、有効データ区間イネーブル生成部5が送信信号に含まれる制御信号を用いて送信信号中に送信データが存在する区間(有効データ区間)を示す信号を生成し、遅延調整部2が上記の遅延調整を有効データ区間で行なう。

(もっと読む)

制御整合ステージを備える装置

【課題】比較的簡単な、制御整合ステージ、方法、およびプロセッサ・プログラム製品を提供する。

【解決手段】第1のステージに第2のステージを整合させるための制御整合ステージ10を備え、制御整合ステージは、第1のステージの出力信号から第1の信号と第2の信号とを導出するための導出手段11と、第1の信号と第2の信号の間の位相を検出するための検出手段12と、前記整合のために前記検出に応じて調整可能インピーダンス・ネットワーク14を制御するための制御手段13とを備える。

(もっと読む)

パルス幅変調器および音声信号出力装置

【課題】分解能を向上させることができ、ダイナミックレンジを向上させるパルス幅変調器を提供する。

【解決手段】クロックに同期しながらカウント値をカウントするシーケンスカウンタ24と、入力信号が前記第1の入力信号パターン種である場合はシーケンスカウンタからのカウンタ値を基準に当該入力信号のスイッチング周期の切り換え時間点を中心としてその前後が対称となるようにパルス幅を変化させ、入力信号が第2の入力信号パターン種である場合はシーケンスカウンタからのカウンタ値を基準に当該入力信号のスイッチング周期の切り換え時間点を中心としてその前または後を1クロック分多くパルス幅を変化させて中間レジスタ値として出力する中間レジスタ処理部20と、シーケンスカウンタからのカウンタ値を基準にして中間レジスタ処理部からの中間レジスタ値にしたがって出力信号を生成するデコーダ22とを備える。

(もっと読む)

半導体集積回路およびその試験方法

【課題】 半導体試験装置を利用して、短い所要時間でD級増幅器の出力パルスの周波数に関する判定を行うことが可能な半導体集積回路を提供する。

【解決手段】 半導体集積回路1は、D級増幅器100と、セレクタ140と、カウンタ150とを有する。カウンタ150は、セレクタ140によって選択された出力信号OUTPまたはOUTMをモニタ対象パルスとし、リセット信号RSTの解除後、所定個数のモニタ対象パルスをカウントしたときに出力端子からカウント終了信号COを出力する。従って、リセット信号RSTの解除から所定時間経過した後の所定期間内にカウント終了信号COが出力されるか否かを判定することにより、D級増幅器100の出力信号の周波数が適正範囲内にあるか否かを判定することができる。

(もっと読む)

スルーレート制御回路、制御方法及び半導体集積回路

【課題】出力アンプのスルーレートを、出力負荷変動があっても高精度に調整可能なスルーレート制御回路を提供すること。

【解決手段】制御時間設定回路がスルーレートを検出するタイミング信号を発生し、電圧比較回路が、出力アンプの出力信号と、上記のタイミング信号によるタイミングに応じた制御電圧との比較を行う。比較結果に応じて、出力アンプ制御回路が、出力アンプのバイアス電流を制御する。上記した処理を、スルーレート制御期間において複数回繰り返す。

(もっと読む)

差動増幅装置

【課題】 差動増幅装置が出力するオフセット電圧を充分に抑制する。

【解決手段】 差動増幅器10は、キャパシタCを介して+IN端子に入力される信号と、−IN端子に入力される信号の差分を増幅する。スイッチS1は、+IN端子が、キャパシタCを介した信号を入力するか否かを切り替える。抵抗RINは、+IN端子と−IN端子の間に接続される。オフセット電圧補正回路20は、+IN端子がキャパシタCを介した信号を入力しないようにスイッチS1が制御された補正期間において、差動増幅器10の出力信号に基づき差動増幅器10のオフセット電圧を補正する。

(もっと読む)

半導体装置

【課題】入力信号のタイプを自動的に判別し、そのタイプに最適な特性の出力信号を共通の出力端子から出力することのできる半導体装置を提供する。

【解決手段】実施形態の半導体装置は、利得を変化させることのできる可変利得増幅器1と、入力信号SIGの周波数を計測するカウンタ2と、を備え、切り替え部3が、入力信号SIGの周波数に応じて、入力信号SIGを、可変利得増幅器1を介して出力端子OUTへ出力するか、そのまま出力端子OUTへ出力するか、を切り替える。また、この半導体装置では、入力信号SIGを可変利得増幅器1を介して出力端子OUTへ出力する場合には、出力先インピーダンス判定部4が、出力端子OUTに接続される機器の入力インピーダンスの高低を判定し、利得調整部5が、出力端子OUTに接続される機器の入力インピーダンスの高低に応じて可変利得増幅器1の利得を調整する。

(もっと読む)

駆動回路

【課題】負荷に流れる電流の異常を検出する。

【解決手段】負荷30の両端に互いに逆相または同相である一対のPWM信号を印加して負荷を駆動する。異常検出回路40は、一対のPWM信号(PWM+,PWM−)の変化状態を検出し、少なくとも一方のPWM信号の変化がなくなった場合にカウントを行い、カウント値が所定値となった場合に、異常検出信号を出力する。

(もっと読む)

チョッパ増幅とデジタル変換の複合回路

【課題】チョッパアンプの出力電圧には所定時間毎に反転する増幅後電圧(Vs)または所定時間毎に反転するオフセット電圧が含まれており、出力電圧から増幅後電圧(Vs)のみを取出してデジタル変換する必要があり、回路が大規模化する。

【解決手段】チョッパアンプとデジタル変換回路を構成する比較回路の間に伝達回路を設ける。伝達回路は、重畳電圧(V1)とデジタル値から変換したアナログ電圧(Vd)を入力し、2種類の電圧(第1出力電圧(VI),第2出力電圧(VII))を出力する。第1出力電圧(VI)と第2出力電圧(VII)の差は、増幅後電圧(Vs)とアナログ電圧(Vd)の差に比例している。この結果、比較回路で増幅後電圧(Vs)とアナログ電圧(Vd)の大小関係を判別することができ、カウンタ回路のカウント値をアップまたはダウンさせ、カウント値を増幅後電圧(Vs)に追従させることができる。

(もっと読む)

プリディストータ

【課題】経年劣化につれて適切でなくなった予備ルックアップテーブルを破棄しメモリ量を減少させるプリディストータを提供することを目的とする。

【解決手段】2個の保存部は、それぞれの保存ルックアップテーブル及び更新ルックアップテーブルのうち特性の高いルックアップテーブルを格納するが、一定期間毎にかつ異なる更新タイミングで、ルックアップテーブルの特性の比較によらず、それぞれの保存ルックアップテーブルを破棄し更新ルックアップテーブルを格納する。歪補償回路11は、通常では更新ルックアップテーブルをロードされるが、更新ルックアップテーブルの破綻時又は保存ルックアップテーブルのロード要求時などには、保存ルックアップテーブルをロードされる。このとき、破棄タイミングからロードタイミングまでの時間がより長い保存部から、歪補償回路11は保存ルックアップテーブルをロードされる。

(もっと読む)

音声出力装置

【課題】スピーカ等に対する音声の無入力検出を柔軟に行い、専用の検出回路を抹消することによるコストダウンと汎用性の向上を実現する。

【解決手段】デジタル音声に基づいてアナログ音声をスピーカ200に出力するデジタルアンプ100において、デジタル音声のデジタル値を周期的に取得し、当該デジタル値をアナログ音声としてスピーカ200に出力した場合に無入力とならない数を比較器31で検出してカウンター32でカウントし、ポーリング期間tあたりのカウンター32のカウント値が所定数未満の場合にデジタルアンプ100のオートパワーダウン処理を制御部40が実行するようになっている。

(もっと読む)

遅延回路及びその制御方法

【課題】入力信号に精度の高い遅延を付加することが可能な遅延回路及びその制御方法を提供する。

【解決手段】遅延回路は、入力信号1001の立ち上がり又は立ち下がりの遷移時刻を、位相の異なる複数のクロック信号に基づいて検出するエッジ検出回路1004と、入力信号の遷移時刻に対応するクロック信号に基づいて、検出された入力信号の遷移時刻から所定の遅延時間経過後に、入力信号の信号波形を再現して出力する出力信号生成部1015と、を備える。

(もっと読む)

増幅回路及びその増幅回路を含むアナログデジタル変換回路

【課題】オフセットキャンセル動作において発生する消費電力を低減可能なコンパレータを提供する。

【解決手段】差動入力信号を受ける一対のMOSトランジスタのドレインと高電位電源線に接続し、一対のMOSトランジスタのドレインに接続する差動出力ノード間の電位差を増幅し、増幅後の電位を差動出力ノードに保持する増幅部と、差動出力ノード間の電圧増幅時に、差動出力ノードにキャンセル電流を流し、増幅部による増幅動作後に、一対のMOSトランジスタのドレイン電圧に応じて差動出力ノードへのキャンセル電流の流入を遮断するキャンセル回路と、差動入力信号の一方の信号の電位を他方の信号の電位と等しく設定し、差動出力ノード間の電位差を増幅したときに、差動出力ノード間の電位が、キャンセル電流を注入する前に比較し、キャンセル電流の注入後に逆転するように、キャンセル電流を設定するコントローラと、を備える増幅回路。

(もっと読む)

周波数特性補償装置

【課題】簡易な手法により前置増幅器を制御する方法とそれを具現化してなる装置とを提供すること。

【解決手段】周波数特性補償装置の備える統計情報計算回路50は、A/D変換器20から適応ディジタルフィルタ30に入力されるディジタル入力信号をモニタして、その信号レベル等に関する統計をとり、統計情報を生成する。制御回路60は、統計情報計算回路50から受けた統計情報に基づいて前置増幅器10の入力オフセット調整及び利得調整を行う。

(もっと読む)

電圧出力装置

【課題】回路規模の増大を抑制することができ、特に液晶表示パネル等の表示装置の駆動回路への適用に適したオフセット補償機能を備えた電圧出力装置を提供する。

【解決手段】電圧出力装置は、反転入力端子および非反転入力端子を有するオペアンプと、反転入力端子の非反転入力端子への接続、非接続を切替える接続切換手段と、反転入力端子と非反転入力端子の接続時において、オペアンプの反転入力側の負荷抵抗と非反転入力側の負荷抵抗の一方または双方の抵抗値を変化させる負荷抵抗変更手段と、反転入力端子と非反転入力端子を接続した状態において反転入力側の負荷抵抗と非反転入力側の負荷抵抗の一方または双方の抵抗値を順次変化させたときに、オペアンプの出力電圧が変化したときの反転入力側の負荷抵抗と非反転入力側の負荷抵抗の抵抗値を維持させる負荷抵抗設定手段と、を含む。電圧出力装置は、反転入力端子と非反転入力端子の非接続時におけるオペアンプの出力電圧を出力する。

(もっと読む)

デジタルプレディストーション処理装置及び方法

【課題】プレディストーションを行うデジタルプレディストーション処理装置、及びプレディストータのパラメータの最適化方法を提供する。

【解決手段】非線形装置へ提供するデータソース信号に対してプレディストーションを行い且つプレディストーションされた信号を出力するプレディストータと、前記非線形装置からの出力信号を前記データソース信号と同じフォーマットに変換された出力信号に変換する信号変換装置と、前記データソース信号を、前記データソース信号が生成されてから前記変換された出力信号が出力されるまでの所要時間と近似的に等しい一定の時間遅延させ、遅延されたデータソース信号を出力する遅延装置と、前記変換された出力信号の統計的特性と前記データソース信号の統計的特性との差を反映する第1のコスト関数を算出し、且つ前記第1のコスト関数により前記プレディストータのパラメータを最適化するパラメータ最適化装置とを備える。

(もっと読む)

時定数調整回路

【課題】参照用の時定数発生回路を集積回路の外部に用意すると、集積回路の端子数の増加および半導体チップ面積の増大を招き、その結果、製造コストが増大してしまう。また、集積回路単体では時定数の調整を行えない。

【解決手段】スイッチトキャパシタを用いることで、時定数発生回路を集積回路に内蔵しても十分な精度が保たれる。さらに、時定数の補正結果を記憶する記憶部を設けることで、時定数調整用回路と、時定数調整後の通常動作用回路を、一部兼用することが可能となる。集積回路の端子数と、半導体チップ面積を節約でき、その結果、製造コストを抑えられる。さらに、外部から電源さえ供給されれば、自動的かつ自律的に時定数の調整を行える。

(もっと読む)

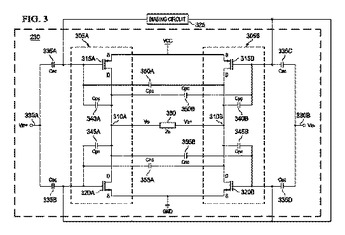

入力抵抗が改善され、コモンモード制御された増幅器

第1出力(Vo−)を規定し、第1入力端子(330A)に結合されるゲートを各トランジスタ(315A、320A)が有する第1対のトランジスタ(305A)、第2出力(Vo+)を規定し、第2入力端子(330B)に結合されるゲートを各トランジスタ(315B、320B)が有する第2対のトランジスタ(305B)、第2出力端子(310B)に及び第1対のトランジスタの第1トランジスタ(315A)のゲートに結合される第1キャパシタ(350A)、第2出力端子(310B)に及び第1対の第2トランジスタ(320A)のゲートに結合される第2キャパシタ(355A)、第1出力端子(310A)に及び第2対の第3トランジスタ(315B)のゲートに結合される第3キャパシタ(350B)、及び第1出力端子(310A)に及び第2対の第4トランジスタ(320B)のゲートに結合される第4キャパシタ(355B)を含む増幅器(230)。

(もっと読む)

(もっと読む)

充電回路、増幅回路

【課題】消費電力及びノイズを抑制しつつ、昇圧電圧でコンデンサを早く充電可能な充電回路を提供する。

【解決手段】充電回路は、入力されるクロック信号の周波数の上昇に応じて短くなる時間間隔ごとに入力電圧を昇圧した昇圧電圧を生成するチャージポンプ回路と、昇圧電圧を積分してコンデンサに印加する積分回路と、第1クロック信号がクロック信号としてチャージポンプ回路に入力される際にコンデンサの充電電圧が所定レベルとなるまでの時間よりも短い時間で充電電圧が所定レベルとなるよう、第1クロック信号より高い周波数の第2クロック信号をクロック信号としてチャージポンプ回路に出力した後に、第1クロック信号をクロック信号としてチャージポンプ回路に出力するクロック信号出力回路と、を備える。

(もっと読む)

1 - 20 / 85

[ Back to top ]