Fターム[5J500AM17]の内容

Fターム[5J500AM17]に分類される特許

301 - 313 / 313

バッファ回路

【課題】消費電力の増加を抑制しつつ高速に負荷を駆動することができるバッファ回路を提供する。

【解決手段】ノードN1を介してnpnトランジスタQ1に入力される電流が電流検出回路1において検出される。バイアス制御回路2では、この検出電流の増加に応じてnpnトランジスタQ2の電流が減少し、検出電流の減少に応じてnpnトランジスタQ2の電流が増加するように、npnトランジスタQ2のベース電圧が制御される。これにより、負荷に過渡的に流すことが可能な電流を大きくすることができるため、負荷キャパシタCLの容量が大きい場合や、周波数が高い場合でも、入力電圧の変化に出力電圧を高速に追従させることが可能になり、出力電圧波形の歪みを抑えることができる。

(もっと読む)

電流源回路及び差動増幅器

【課題】ショートチャネル効果により、MOSトランジスタの出力抵抗(=rds)が小さくなっても、出力抵抗の大きな電流源回路を提供する。

【解決手段】電流源ブロック11に負性抵抗発生ブロック12を並列に接続する。負性抵抗発生ブロック12は、出力電圧Vout1の微小変化に対して負性抵抗−Rneを発生するように動作する。そのため電流源回路14の出力抵抗は、並列接続された負性抵抗−Rneと電流源ブロック11の抵抗Rcuとの合成抵抗(Rcu//−Rne)で与えられる。抵抗Rcuと負性抵抗−Rneの大きさを略等しくすることにより、電流源回路14の出力抵抗を大きくすることができる。また、電流源回路14を用いると、差動出力端子から見た出力抵抗を大きくできるので、利得の大きな差動増幅器を構成することができる。

(もっと読む)

演算増幅回路及びヘッドホンアンプ

【課題】 音割れや音の消失が生ずるのをより小さくすることを目的とする。

【解決手段】 フォールデッドカスコード型の差動増幅段を有する演算増幅回路において、N形MOSトランジスタ31N,32Nの差動入力トランジスタのドレインと電源ライン34との間に設けられた第1のP形MOSトランジスタ35P,36Pの負荷回路に並列に第2のP形MOSトランジスタ51P,52Pの負荷回路を設けると共にP形MOSトランジスタ31P,32Pの差動入力トランジスタのドレインと接地ラインとの間に設けられた第1のN形MOSトランジスタ35N,36Nの負荷回路に並列に第2のN形MOSトランジスタ51N,52Nの負荷回路を設けたものである。

(もっと読む)

多段増幅装置、並びにそれを用いた受信回路及び送信回路

【課題】 白色雑音を発生させることなく、3次相互変調歪みを抑圧し、かつ低消費電力の増幅回路を提供する。

【解決手段】 第1の並列帰還増幅器及び第2の並列帰還増幅器を縦列に接続し、多段増幅装置を構成する。第1の帰還部及び第2の帰還部は、異なるサセプタンス成分を持つ。第1の並列帰還部は、サセプタンス成分によって、第1の増幅部で増幅された所望信号成分の位相と第1の増幅部で発生した第1のIM3成分の位相とを変化させる。第2の並列帰還部は、サセプタンス成分によって、第2の増幅部で増幅された所望信号成分の位相と、第1のIM3成分の位相と、第2の増幅部で発生した第2のIM3成分の位相を変化させる。第2の並列帰還増幅器から出力される第1のIM3成分の位相と第2のIM3成分の位相との差は、120°以上180°以下であり、第1のIM3成分と第2のIM3成分とは、合成されて抑圧される。

(もっと読む)

増幅装置

【課題】 高周波増幅器または受信機が歪みによる干渉波の影響を受けた時、受信品質劣化や受信できない状態を回避できる増幅装置を得ることを目的とする。

【解決手段】 交流信号を伝送する交流信号伝送路が分岐した第1分岐伝送路が接続され、この第1分岐伝送路から入力される上記交流信号を、第1制御信号に応じた増幅値で出力する第1増幅器39aと、上記交流信号伝送路が分岐した第2分岐伝送路が接続され、この第2分岐伝送路から入力された上記交流信号を、第2制御信号に応じた増幅値で出力する第2増幅器39bと、上記第1増幅器の増幅値と上記第2増幅器の増幅値との和を出力する出力合成部310と、を備え、

上記第1制御信号及び上記第2制御信号は、上記第1増幅器または上記第2増幅器のいずれか一方の増幅値を、いずれか他方の増幅値に影響が無い程度に小さくするよう制御する信号とした。

(もっと読む)

可変利得増幅回路

【課題】 利得を可変にしつつ、信号源とのインピーダンスマッチングを実現する。

【解決手段】 可変利得増幅回路1は、所定の利得を有し、一端が回路出力部に接続される増幅器A1と、上記増幅器A1とは異なる利得を有し、一端が上記回路出力部に接続される増幅器A2と、一端が回路入力部に接続され、他端が上記増幅器A1の他端に接続されるインダクタL1と、上記インダクタL1と共に変圧器Tを構成し、一端が接地され、他端が上記増幅器A2の他端に接続されるインダクタL2と、を備えた構成である。これにより、入力信号Vinが入力される信号経路に応じた入力インピーダンスの変動を抑えることができ、信号源とのインピーダンスマッチングを担保できる。

(もっと読む)

トランスコンダクタンスアンプおよびGm−C型積分器

【課題】 直流レベルで60dB程度の積分器ゲインを確保できる集積回路化されたトランスコンダクタンスアンプを提供する。

【解決手段】 Pチャネル型のMOSFETM7,M8のドレインにはそれぞれ同じPチャネル型のMOSFETM7A,M8Aが接続され、これらのMOSFETM7A,M8Aのゲートが共通に接続されるとともに、このMOSFETM7AのドレインがNチャネル型のMOSFETM5Aを介してMOSFETM5のドレインと接続されている。MOSFETM8Aのドレインは、出力端子12に接続されるとともに、Nチャネル型のMOSFETM6Aを介してMOSFETM6のドレインと接続されている。また、キャパシタC2,C3はMOSFETM3,M4のゲート−ソース間容量を増加させ、発振を防止するために接続されている。

(もっと読む)

RFフロントエンド集積回路

携帯型通信装置用の全てのRFフロントエンド又は送受信機素子を有するモノリシック集積回路(IC)及びその製造方法に関する。RFフロントエンドは、電力増幅器(PA)と、マッチング、カップリング及びフィルタリング回路と、調整されたPA出力信号をアンテナ結合するアンテナスイッチとを有する。出力信号センサは、アンテナスイッチにより切り替えられた信号の少なくとも電圧振幅を検知して、検知された出力の過度な値に応答してPA出力電力を制限するようPA制御回路に指示する。好ましい製造技術は、スイッチングデバイスを形成するよう複数のFETをスタックする。PA出力信号の不要な高調波を散逸的に終端するi級PAアーキテクチャについて記載される。RF送受信機ICの好ましい実施例は、2つの区別可能なPA回路と、2つの区別可能な受信信号増幅器回路と、4つの回路のうちの何れか1つへ単一のアンテナ接続を選択的に結合する4方向アンテナスイッチとを有する。  (もっと読む)

(もっと読む)

入力バイアス電流の相殺回路を有したバイポーラ差動入力段

入力バイアス電流相殺回路を有したバイポーラ差動入力段は、入力ペア(Q1、Q2)およびバイポーラのトラッキングトランジスタ(Q3)を含む。入力段は、入力ペア(Q1、Q2)およびトラッキングトランジスタ(Q3)中のコレクタ電流、ならびに入力ペア(Q1、Q2)およびトラッキングトランジスタ(Q3)のコレクタ・エミッタ電圧が、実質的に互いに等しい。ラテラルPNPトランジスタ(Q7)の第1のコレクタが、実質的に等しいコレクタ電流を得るために必要な、トラッキングトランジスタ(Q3)のベース電流を供給し、第2および第3のコレクタ(Q7)が、バイアス電流の相殺電流として、トラッキングトランジスタ(Q3)のベース電流のコピーを入力ペア(Q1、Q2)のベースに供給し、それによって、入力段の入力バイアス電流が減少される。  (もっと読む)

(もっと読む)

増幅器用の適応型バイアス電流回路及び方法

増幅回路の検出された入力電力に少なくとも部分的に基づいて、大きな電流ブーストをもたらす、増幅器用の適応型バイアス方法及び回路。本発明の方法及び回路は、検出された入力電力に基づく更なるバイアス電流を提供する。本発明の回路は、単純で、面積効率がよく、低電力で、安定且つデジタルプログラミングが可能であろう。加えて、本発明の方法及び回路は、インダクタ及び/又は抵抗縮退を有する増幅器を含む、多くの増幅回路構成とともに用いることができる。 (もっと読む)

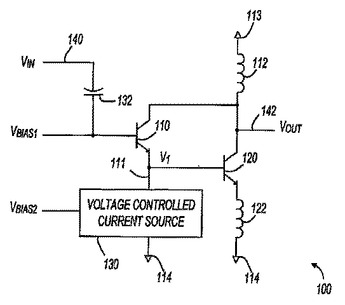

バイアスされたダーリントン・トランジスタ対、方法およびシステム

増幅器は、ダーリントン・トランジスタ対(110,120)および入力トランジスタ(110)中のバイアス電流を増加させるためのバイアスを与えるネットワークを含む。回路(100)は、入力トランジスタ(110)、第2トランジスタ(120)、無線周波数(RF)チョーク(112)、縮退インダクタ(122)、キャパシタ(132)および電圧制御電流源(130)を含む。入力トランジスタ(110)および第2トランジスタ(120)は、コレクタがノード(142)でともに結合され、入力トランジスタ(120)のエミッタがノード(111)に結合されて、ダーリントン・トランジスタ対を形成するために結合される。  (もっと読む)

(もっと読む)

光受信用前置増幅器

光受信用前置増幅器は、反転増幅器1と、反転増幅器1の入出力端子間に接続された電流電圧変換素子2とを備えている。反転増幅器1は、反転増幅器1の入力端子Inにゲートが接続された第1のトランジスタ3と、第1のトランジスタ3のドレインにソースが接続され且つゲートに所定の電圧Vbが与えられた第2のトランジスタ4と、第2のトランジスタ4のドレインに接続された負荷5とを有する。反転増幅器1の入力端子Inと第2のトランジスタ4のソースとの間に第3のトランジスタ6が接続されている。 (もっと読む)

高性能低雑音増幅器

二つの入力端子上において逆位相で一対の入力信号Sp及びSnを受信し、四つの出力端子上において逆位相で二対の出力電流SIp及びSInをもたらすための信号処理回路が提供されている。各々の入力信号Sp及びSnは増幅ユニットLNAUp及びLNAUnで増幅され、その後、分割ユニットSPLUp及びSPLUnで分割される。本発明は、二つの分割ユニットSPLUp及びSPLUnの各々が、前記増幅ユニット、すなわちそれぞれLNAUp及びLNAUnと前記出力端子の一つとの間に接続される少なくとも二つの分岐部、すなわちそれぞれBIp及びBQp並びにBIn及びBQnを含むように構成され、四つの分岐部BIp及びBQp並びにBIn及びBQnは各々、少なくとも一つのインピダンス部、すなわちそれぞれ同じ特性を有するRIp、RQp、RIn、及びRQnを含む。ミキサ回路は当該信号処理回路で容易にスタックされ得る。  (もっと読む)

(もっと読む)

301 - 313 / 313

[ Back to top ]