Fターム[5K029AA20]の内容

直流方式デジタル伝送 (8,390) | 目的、効果 (1,587) | ICへの適合化 (16)

Fターム[5K029AA20]に分類される特許

1 - 16 / 16

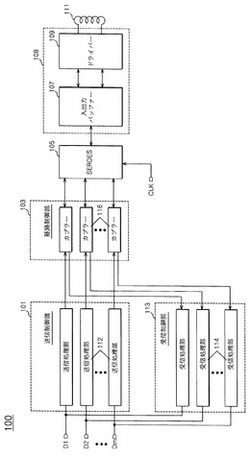

半導体システムのための無線信号送受信装置、無線信号送信方法、及び無線信号受信方法

【課題】本発明は、制限された面積から充分なインダクタンスを確保して安定的に送受信できる半導体システムのための無線信号送受信装置を提供することを目的とする。

【解決手段】無線信号送受信装置100は、並列入力信号を直列信号に変換して出力し、直列入力信号を並列信号に変換して出力するサーデス信号およびサーデス回路105から出力される直列信号によりインダクタンスを発生し、外部装置と誘導結合現象によって発生した信号をサーデス回路105の直列信号に提供するカップリングパッド111を備える。

(もっと読む)

非同期データ転送装置

【課題】電流量の監視による遅延仮定なしで配線故障検出ができ、遅延故障耐性と配線故障耐性を同時に有した非同期データ転送装置を提供する。

【解決手段】IPコア間に配設するLSIの非同期データ転送装置1において、第1のIPコアに接続する第1の配線3aと、第2のIPコアに接続する第2の配線3bと、第1の配線3aに接続する送信器2と、第2の配線3bに接続する受信器4と、送信器2と受信器4とを接続する第3の配線3cと、を含み、送信器2は、符号器5と入力制御部6とを有する入力部2Aと、出力部2Bと、を含み、受信器4は、入力部4Bと、復号器7と出力制御部8とを有する出力部4Aと、を含み、送信器2の符号器5は、第3の配線3cのオープン故障を検出する電流ドライバ回路11a,11b,11c,11dを備える。

(もっと読む)

送信回路、受信回路、送信方法、受信方法及び信号伝達システム

【課題】従来の信号伝達システムは、動作環境により論理判定に誤りが生じる問題があった。

【解決手段】本発明にかかる信号伝達システム1は、一次側コイル11、二次側コイル12、送信回路2、受信回路3を備える。一次側コイル11と二次側コイル12とは磁気的に結合される。送信回路2は、送信データに基づいて生成される送信信号の立ち上がりエッジ又は立ち下がりエッジに応じてドライブ回路21に駆動制御信号を出力するプリドライバ回路22と、駆動制御信号に応じて一次側コイル11に増加率と減少率とが非対称になる正の駆動電流又は負の駆動電流を供給するドライブ回路21とを有する。受信回路3は、送信信号により二次側コイル12に生じる受信信号の正の振幅と負の振幅との絶対値の差に応じた検出電圧を出力する受信信号検出回路31と、検出電圧と基準電圧との電圧差に基づいて送信データを再生するヒステリシスコンパレータ32とを有する。

(もっと読む)

高分解能出力ドライバ

それぞれ、量子化ステップより実質的に大きい、公称インピーダンスを有し、量子化ステップより実質的に小さい、インピーダンスステップだけ、相互にインクリメント的に異なる、比較的に少数のサブドライバブランチまたはスライスを有する、高分解能出力ドライバ。一実装では、かかる「差動」または「非一様」サブドライバスライスは、n choose k等化器の個別の要素を実装し、各かかる差動サブドライバスライスは、一様要素インピーダンス較正DACによって実装される。別の実装では、一様スライス等化器の各構成要素は、差動スライスインピーダンス較正DACによって実装され、さらに別の実装では、差動スライス等化器の各構成要素は、差動スライスインピーダンス較正DACによって実装される。付加的セットの実装の実装では、等化およびインピーダンス較正機能は、階層的実装のネスト化された「DAC内のDAC」配設においてではなく、個別の並列セットのドライバブランチにおいて、双方向に実装される。かかる双方向配設を通して、等化器および較正器量子化の倍増が回避され、それによって、規定の範囲および分解能を満たすために要求されるサブドライバスライスの総数を減少させる。 (もっと読む)

伝達特性測定装置、伝達特性測定方法、および、電子デバイス

【課題】被試験回路の伝達特性を測定する。

【解決手段】被試験回路の入出力間の伝達特性を測定する伝達特性測定装置であって、予め定められた周波数のキャリア信号に予め定められた周波数とは異なる周波数の加算信号を加算した試験信号を生成して、被試験回路に入力する試験信号入力部と、被試験回路が出力する出力信号を測定した結果に基づいて、加算信号の周波数における被試験回路の伝達特性を測定する伝達特性測定部とを備える伝達特性測定装置を提供する。被試験回路は、半導体チップに形成されてもよい。被試験回路は、半導体チップに入力される信号を補正して出力し、半導体チップには、被試験回路の出力信号を、キャリア信号の周波数でサンプリングするサンプリング回路が更に形成されてもよい。

(もっと読む)

デジタルデータ伝送装置

【課題】電源電圧や接地レベルの変動に伴う信号の振幅変動やジッター等の非対称歪の発生が抑えられるようにしたデジタルデータ伝送装置を提供すること。

【解決手段】システムLSIから出力されるデジタルデータを、バッファ回路3(1)を介して波形整形回路4に供給し、ここで立上り部と立下り部にオーバーシュートがかけられたデジタルデータが、駆動電源ライン25から伝送路に供給されるようにし、このとき、調整電圧発生回路31により駆動電源ライン25の電圧を調整し、伝送系の波形歪みによる影響の除去に適したオーバーシュートがえられるようにしたもの。

(もっと読む)

データ伝送装置

【課題】システムLSI1から外部メモリ2へのデータ伝送時に、システムLSI1に設けた波形整形回路4により伝送データや制御信号の変化部の波形を急峻に整形し、制御信号の振幅変動やジッター等の非対称歪の発生を抑えたデータ伝送装置を提供する。

【解決手段】システムLSI1と、伝送路6を通してLSI1に接続された外部メモリ2を備え、LSI1のデータ処理時に外部メモリ2との間でデータ伝送を行なうデータ伝送装置であって、LSI1に配置した波形整形回路4により、LSI1からデジタル信号が出力される際に信号波形の歪を監視し、信号波形に歪が発生する可能性があれば、伝送路6に供給される信号電流値を調整することによりその信号波形に発生する歪を除去する。

(もっと読む)

LVDS受信方法および受信装置

【課題】電源投入時や信号切り換え時に、LVDSデータ信号がS/P変換でラッチミスした映像信号が後段回路に出力することを遮断し、内部で作成した同期信号と映像信号を出力することで、異常画面表示を防止することができる。

【解決手段】LVDSクロック信号を逓倍し、前記逓倍したLVDSクロック信号によって、LVDSデータ信号をシリアル・パラレル変換するステップを有し、かつ、前記シリアル・パラレル変換されたLVDSデータ信号に含まれる同期信号によって前記シリアル・パラレル変換のラッチミス発生有無を検出するステップと、前記検出の結果をもとに、前記逓倍したLVDSクロック信号と他のクロック信号との切り換え、及び前記LVDSデータ信号に含まれる同期信号と他の同期信号との切り換え、及び前記シリアル・パラレル変換したLVDSデータ信号と他の映像信号との切り換えをするステップを有することを特徴とする。

(もっと読む)

半導体送受信装置システム、メモリカードおよびメモリカードホスト機器

【課題】インピーダンス調整、ドライブ能力調整の柔軟性があり、かつ高速な信号伝送が可能な半導体送受信装置システムを小面積にて得ること。

【解決手段】双方向に信号の送受信を行なう半導体送受信装置システムであって、1つのマスター半導体送受信装置と少なくとも1つのスレーブ半導体送受信装置で構成され、前記マスター半導体送受信装置、前記スレーブ半導体送受信装置ともに信号の送受信を行なうための送信回路と受信回路と、伝送線路とのインピーダンスの整合を図る終端回路を具備し、前記マスター半導体送受信装置のみに信号駆動用の電流源を持たせる構成とした。

(もっと読む)

ビット長のカウンタを備えた非同期式シリアルデータ伝送用の集積回路

【課題】ビット長のカウンタを備えた非同期式シリアルデータ伝送用の集積回路を提供する。

【解決手段】本発明は、非同期式シリアルデータ伝送用の集積回路(7)であって、

非同期式シリアルデータ(d)を与える入力端子(30)と、

該入力端子に与える走査クロック(aclk)によって非同期式シリアルデータ(d)を走査する走査器(5)と、

走査クロック(aclk)のクロック数(m)またはビット長のカウンタクロック(xclk)の計数によってビット時間を決定するビット長のカウンタ(4)と、を構成するための構造を有する集積回路において、

ビット長のカウンタ(4)のクロック数(m)の可変設定用のビット長端子(32)が集積回路(7)及び/またはビット長のカウンタ(4)に構成されている集積回路に関する。

(もっと読む)

バス回路及び半導体回路

【課題】波形品質の劣化、電源バウンス、及び電磁波放射を抑制して、高速動作を実現すると共に、使用ピンの数の増大及び回路規模の拡大を抑制することができるようにする。

【解決手段】バス回路10は、伝送線路12と、伝送線路12の送信端に接続されたオープンドレインのPMOS素子からなる駆動スイッチング回路14と、一端が伝送線路12の受信端に接続された終端抵抗16と、インダクタンス成分を有する接続回路20を介して、終端抵抗16の他端に接続され、終端電位となっている電源22と、終端抵抗16の一端に接続され、かつ、信号を受信するためのレシーバ素子18とを備える。バス回路10は、ドレインが、終端抵抗16を迂回するように接続回路20を介して電源22に接続され、ソースが接地されているNMOS素子からなる迂回スイッチング回路24を備え、迂回スイッチング回路24のゲートは伝送線路12の受信端に接続されている。

(もっと読む)

送受信システムの試験方法及び装置

データ送受信システムを試験する方法は、試験信号をシステムの送信機(14)からシステムの受信機(12)に送信し、受信した信号を分析する。デューティ比の関係は、試験信号とシステムの受信機によって用いられるタイミング信号との間で変更され、デューティ比の変動の変更が分析される。デューティ比の関係を変更することによって、ディーティ比歪み(DCD)をもたらし、これを、組み込まれたジッタ挿入の形態と考えることができる。このタイプのジッタを、比較的簡単に測定することができる。  (もっと読む)

(もっと読む)

伝送装置

【課題】 異なる電源系を有する回路ブロック相互間で伝送線を通して信号を正常に伝送する。

【解決手段】 トレンチ絶縁分離構造を備えたIC1は、互いに絶縁されたプロトコル変換部3とトランシーバ4を備えている。出力回路15、16とコンパレータ34との間の伝送線20、21にはコンデンサ22、23が介挿されており、コンパレータ34の入力端子間にはコンデンサ35が接続されている。出力回路15、16が互いに反転した電圧を出力すると、コンデンサ22、35、23の直列回路において分圧作用が生じ、コンデンサ35の端子間に分圧電圧が生じる。この分圧電圧の向きは、出力回路15、16に入力される伝送信号の論理(H/L)に応じて一意に定まる。

(もっと読む)

差動シリアル・ディジタル出力A/D変換手段および撮像装置

【課題】多線読出しセンサを用いた撮像装置において、AD変換後にディジタル信号処理プロセッサまでの基板内配線数を減らすことによって、装置内部でのノイズ発生量を抑圧し、センサからADまでのアナログ信号系にフィードバックするキックバックノイズを減少させる。

【解決手段】結果的にディジタル信号の配線数を減らすことによって、アナログ・フロント・エンドLSIや基板の面積を小さくする。

(もっと読む)

終端回路、半導体装置、及び電子機器

【課題】 終端抵抗としてトランジスタを使用する終端回路の整合特性を向上させる。

【解決手段】 Pチャネル型MOSトランジスタ11aとNチャネル型MOSトランジスタ11bとの並列接続を伝送線路102と電源線103との間に備え、Pチャネル型MOSトランジスタ11cとNチャネル型MOSトランジスタ11dとの並列接続を伝送線路102とグランド線104との間に備える。そして、これら全てをオンとしたときのオン抵抗によってテブナン終端を形成する。

(もっと読む)

共通モードアイドル状態および選択可能なスルーレートを有するTxラインドライバ

選択可能なスルーレートおよび共通モードアイドル状態を有する送信ラインドライバは、ラインドライバ(184)およびプリドライバ(182)の間に結合される選択可能なキャパシタのキャパシタアレイ(186)を含み、選択可能なキャパシタによってスルーレートが選択されてもよい。共通モードアイドル状態は、選択可能なスイッチ(214、215)(記載される実施例におけるMOSFET)を、プリドライバにバイアス電流を与えるミラーデバイス(198)に結合することによって与えられ、スイッチによってバイアス電流が除去されるときに、プリドライバは回路に対する電源電圧に等しい出力信号を生成する。したがって、ラインドライバの差動対(202、204)はともにバイアスをかけられてオンにされ、共通モードアイドル状態を与える。共通モードアイドル状態は論理1に対する出力信号の大きさの半分に等しい。  (もっと読む)

(もっと読む)

1 - 16 / 16

[ Back to top ]