Fターム[5K029HH13]の内容

直流方式デジタル伝送 (8,390) | 受信部 (1,135) | サンプリングをするもの (131)

Fターム[5K029HH13]の下位に属するFターム

1ビット内のサンプリング点が多数あるもの (30)

Fターム[5K029HH13]に分類される特許

1 - 20 / 101

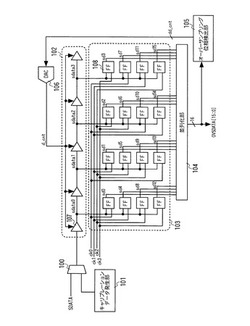

オーバーサンプリング回路及びそれを備えた通信装置

【課題】多相シリアルデータを多相クロックでサンプリングするオーバーサンプリング回路において、遅延量制御動作に伴う消費電流を低減する。

【解決手段】シリアルデータSDATAは、データ遅延部102により多相シリアルデータsdata0〜sdata3とされ、オーバーサンプリング部103において、多相クロックck0〜ck3により、オーバーサンプリングされる。データ遅延部102のデータ遅延素子107の遅延時間は、キャリブレーションデータ発生部101で生成されたデータのオーバーサンプリング出力の位相差をオーバーサンプリング位相検出部105により検出し、その位相差が所望の値となるように、遅延量制御デジタル信号dd_cntを調整する。遅延量制御デジタル信号dd_cntをデジタルアナログ変換部106によりアナログの遅延量発生信号d_cntに変換し、データ遅延素子107に供給する。

(もっと読む)

CDR回路及びCDR方法

【課題】ロック状態であるか否かを検出し、その検出結果を出力するCDR回路及びCDR方法を提供する。

【解決手段】受信データ信号をサンプリングするデータサンプリングクロック信号に同期して、受信データ信号をサンプリングしてサンプルドデータ信号を生成するデータサンプリング回路、データサンプリングクロック信号に対して位相がずれたエッジサンプリングクロック信号に同期して、受信データ信号をサンプリングしてサンプルドエッジ信号を生成するエッジサンプリング回路、データサンプリングクロック信号に同期して、受信データ信号の振幅と基準電圧との比較結果信号を出力する振幅比較回路を備え、比較結果信号、サンプルドデータ信号およびサンプルドエッジ信号に基づいて、データサンプリングクロック信号の位相を調整する位相シフタ回路、及び受信データ信号とデータサンプリングクロック信号との位相関係を検出するロック検出回路を備える。

(もっと読む)

送信装置、受信装置、シリアル通信装置、及び、その装置を備えた記録装置

【課題】受信側の1ビット分のサンプリングクロックの周期に対して送信クロックの周期が変動すると受信エラーが発生する。

【解決手段】受信データ列の中で、サンプリングデータが反転する毎にサンプリングクロックを再同期をとる。更に、同じデータが所定数連続する場合は、反転するダミービットを挿入して再同期をとれるように構成する。

(もっと読む)

データリカバリ方法およびデータリカバリ装置

【課題】入力されたシリアル信号のジッタが大きい場合であっても、復調エラーの発生を抑制することができるデータリカバリ方法およびデータリカバリ装置を提供すること。

【解決手段】入力されたシリアル信号が表すデータを復元するデータリカバリ装置を用いたデータリカバリ方法において、シリアル信号をイコライズするイコライジング工程(S1)と、イコライジング工程でイコライズされたシリアル信号をオーバーサンプルするオーバーサンプリング工程(S2)と、オーバーサンプリング工程で得られたオーバーサンプルデータに基づいてイコライジング工程でイコライズされたシリアル信号のパターン長を演算し、演算したパターン長によってイコライズ工程の処理結果を評価する評価工程(S3)と、評価工程における評価結果に基づいてイコライズ工程のイコライズ量を調整するイコライズ量調整工程(S4)とを有する。

(もっと読む)

データ復元回路及びデータ復元方法

【課題】孤立パルスを確実に検出してデータ判定を実行できるデータ復元回路を提供する。

【解決手段】データ復元回路は、デジタルデータの列のうち2つの連続するデジタルデータを用いて、内挿により第1のデータ切り替わり点の位置を算出すると共に、外挿により第2のデータ切り替わり点の位置を算出する位相検出器と、第1のデータ切り替わり点の平均位置と瞬時位置とに基づいてデジタルデータの列からデータ判定値の列を抽出するデータ判定部と、2つの連続するデジタルデータに挟まれた時間軸上の区間の内に、直前の2つの連続するデジタルデータの外挿直線及び直後の2つの連続するデジタルデータの外挿直線からそれぞれ求めた2つの第2のデータ切り替わり点が位置し且つ2つの外挿直線の傾きの符号が互いに異なる場合、データ判定値の列の当該区間に対応するデータ判定値を、外挿により推定されるデータ値で置き換えるデータ選択部を含むことを特徴とする。

(もっと読む)

適応型受信システム、適応型送受信システム及び複数チャネル送受信システム

【課題】ロックポイント付近におけるサンプリングクロックの位相の調整と、イコライザ部の制御とを安定させ、ジッタトレランスを高める。

【解決手段】位相比較部は、サンプリングタイミングとサンプリングタイミングよりも第一の所定位相分前のタイミングとの間の第一区間に、等化信号EQDATAのエッジが存在するか否かを示す位相比較信号LAG(n)を出力するとともに、サンプリングタイミングとサンプリングタイミングよりも第二の所定位相分後のタイミングとの間の第二区間に、等化信号EQDATAのエッジが存在するか否かを示す位相比較信号LEAD(n)を出力する。判定部は、検出データパターンの各ビットに対応する位相比較信号LAG(n),LEAD(n)の出力パターンを所定の比較対象パターンと比較し、合致するか否かに基づいて、等化信号EQDATAの1ビットがサンプリングクロックCKの1周期よりも長いか短いかを判定する。

(もっと読む)

情報受信制御装置、情報受信制御方法、情報受信制御プログラムおよび記録媒体

【課題】調歩同期式のシリアル通信における通信データのサンプリングタイミングを簡単な回路構成によって制御することで通信データ単位でのサンプリング誤差の累積を防止し、通信データの受信エラーの発生を抑止することができるようにした情報受信制御装置、情報受信制御方法、情報受信制御プログラムおよび記録媒体を提供する。

【解決手段】調歩同期式のシリアル通信に用いられるビット単位の通信データの受信の際に、「基準クロックを分周したカウンタークロック」のカウンタークロック数に対する、「基準クロックから算出される分周値をもとにハード特性を考慮した特性分周値」を計算する。分周値と特性分周値を用いて算出されるそれぞれのカウンタークロックに基づく誤差からビット単位での誤差量を算出し、その誤差量をもとにカウンタークロック数の計数を行う際の初期値を決定する。

(もっと読む)

受信回路

【課題】補間誤差を低減することができる受信回路を提供することを課題とする。

【解決手段】受信回路は、入力データ信号をクロック信号に基づいてサンプリングしてサンプリング信号を出力するサンプリング回路(201)と、前記入力データ信号に対する前記サンプリング信号の位相情報に基づいて前記サンプリング信号を補間して補間データ信号を出力するデータ補間回路(202)と、前記サンプリング信号と前記位相情報とに基づいて補間誤差を出力する補間誤差判定回路(203)と、前記補間誤差に基づいて設定される等化係数によって前記補間データ信号を等化し、前記等化された補間データ信号を判定して判定信号を出力する判定等化回路(204)と、前記判定信号又は前記等化された補間データ信号に基づいて前記位相情報を生成し、前記データ補間回路及び前記補間誤差判定回路に前記位相情報を出力する位相検出回路(205)とを有する。

(もっと読む)

エレベータの信号伝送装置

【課題】直列伝送信号が時間軸に対して歪んだとしても、正しくデータを受信することができるレベータの信号伝送装置を提供する。

【解決手段】直列伝送信号の最初のビット以外の特定のビットが直前のビットと異なるレベルに緩やかに移行する場合に、親局によるサンプリング位置での特定のビットの値が異なるレベルと認識される値となるように、残りのビットの時間幅を維持しつつ、最初のビットの時間幅を狭くして、複数のビットを連続的に並べて親局へ送信するようにした。

(もっと読む)

受信回路

【課題】消費電力及びノイズを低減することができる受信回路を提供することを課題とする。

【解決手段】入力データをサンプリングすることによりデジタルデータを出力するサンプリング回路(401)と、前記サンプリング回路により出力されたデジタルデータに対して無限インパルス応答フィルタを用いて等化処理を行う等化回路(402)と、前記等化回路により等化処理されたデータの位相を検出する位相検出回路(404)と、前記位相検出回路の出力信号に対してフィルタリングを行う第1のフィルタ(405)と、前記第1のフィルタの出力信号を基に前記無限インパルス応答フィルタのフィードバックするデータのビット数を調整する制御回路(403)とを有する受信回路が提供される。

(もっと読む)

受信装置

【課題】少ないビット数のADCを用いながら、信号受信精度を維持することが可能な受信装置を提供する。

【解決手段】第1クロック信号に同期して、NRZ方式の受信信号をサンプリングして得られるサンプル値と当該サンプル値の直前のサンプル値との差分を量子化する第1アナログ/デジタル変換器と、第1クロック信号とは位相が異なる第2クロック信号に同期して、受信信号をサンプリングして得られるサンプル値を量子化する第2アナログ/デジタル変換器と、第1アナログ/デジタル変換器の出力の変化に基づいて、受信信号で表される受信データを復元するデータ判定部と、第2アナログ・デジタル変換器の出力とデータ判定部で復元された受信データとに基づいて、受信信号の同期信号と第1クロック信号および第2クロック信号との位相ズレを抽出する位相検出部と、位相ズレに基づいて、第1クロックおよび第2クロックの位相を調整する位相調整部とを備える。

(もっと読む)

受信機、通信システム及び受信方法

【課題】CPUの負担を軽減し、情報を正確に受信する。

【解決手段】第1のレートで変調されたデジタル信号S0が出力されると、このデジタル信号S0と等価なデジタル信号S3について、第1のレートよりも高い第2のレートでのサンプリングを実行する。そして、サンプリングした結果に基づいて、デジタル信号S0に含まれていたデジタル情報を抽出する。これにより、デジタル信号を受信する受信レジスタ22のサンプリングレートを設定した後は、例えばCPU等によるデジタル信号S0のビット数の変換処理等が不要になる。このため、受信されたデジタルデータを取り扱うCPUや制御機器の負担が軽減され、情報の受信を効率よく行うことが可能となる。

(もっと読む)

ビット変換回路、転送ユニット、通信システム、ビット変換方法及びプログラム

【課題】ビット変換の変換テーブルを小さいゲート規模で実装したビット変換回路、転送ユニット、通信システム、ビット変換方法及びプログラムを提供する。

【解決手段】例えば、8b/10bエンコーダ11によれば、変換後のデータが有する‘0’と‘1’の数が一致するか否かに応じて、8b/10b変換の際に利用するエンコードテーブルのパターン分けを行う。そして、入力データがデータを示すDコードであるとき、‘0’と‘1’の数が同じである場合には、入力データの数が同じであることを利用して算出し、そうでない場合には、エンコードテーブルに従って片方の極性の変換を行った後、インバータにより他方の極性の変換を行う。

(もっと読む)

データ信号品質評価装置

【課題】データ信号のアイパターンに関する品質評価をより効率的に行う。

【解決手段】品質評価手段34は、基準マスク設定手段32で設定された基準マスクの大きさを拡大させつつ、アイパターンを形成する波形データの表示ポイントのうち基準マスクの領域内に入る数を計数し、その計数値と基準マスクの拡大率とに基づいてデータ信号の基準マスクに対するマージンに関する品質評価を行い、その評価結果を表示器40に表示させる。この品質評価手段34は、波形データ取得部21で所定時間幅のアイパターンの表示に最低限必要な数のデータが取得される毎に、その取得したデータに対するマージン測定を行うリアルタイム測定モード34bを有している。

(もっと読む)

データ信号品質評価装置

【課題】データ信号のアイパターンに関する品質評価をより効率的に行う。

【解決手段】マスク領域制限手段35は、操作部50の操作により任意の幅と角度を指定させ、基準マスク設定手段32により評価対象のデータ信号に対するコンプライアンス測定のために設定された基準マスクMrの有効範囲を、指定された幅と角度で決まる範囲に制限するとともに、制限された有効範囲Esを表示器40に示す。品質評価手段34は、マスク領域制限手段35によって基準マスクの有効範囲が制限されたときに、それと連動してその制限された有効範囲に対するコンプライアンス測定を行い、品質評価する。

(もっと読む)

データ信号品質評価装置

【課題】データ信号のアイパターンに関する品質評価をより効率的に行う。

【解決手段】マスク領域制限手段35は、操作部50の操作により任意の幅と角度を指定させ、基準マスク設定手段32により評価対象のデータ信号に対するマージン測定のために設定された基準マスクおよびそれを拡大したマスクの有効範囲を、指定された幅と角度で決まる範囲に制限するとともに、制限された有効範囲Esを表示器40に示す。品質評価手段34は、マスク領域制限手段35によってマスクの有効範囲が制限されたときに、それと連動してその制限された有効範囲におけるマージン測定を行い、品質評価する。

(もっと読む)

受信回路

【課題】エラーの発生率を改善し目標とする発生率にする際の遅延量を低減した受信装置を提供する。

【解決手段】発生確率が時間に応じて正規分布するランダムジッタを含む信号を入力し、この入力信号をデジタルデータに変換して出力する受信装置において、位相を設定可能なクロック信号を生成するクロック回路と、前記入力信号を前記クロック信号に基づくタイミングでデジタルデータに変換して出力するとともに、前記変換の際にエラーが生じた場合にはエラー信号を出力する第1受信回路と、前記入力信号を遅延させた信号を、前記クロック信号に基づくタイミングでデジタルデータに変換して出力するとともに、前記変換の際にエラーが生じた場合エラー信号を出力する第2受信回路と、第1、第2受信回路のエラー信号に基づいて、第1受信回路または第2の受信回路のいずれか一方からのデジタルデータを選択して出力するデータ出力制御部を備えた。

(もっと読む)

半導体集積回路装置、インタフェース回路

【課題】EMIを低減する半導体集積回路、インタフェース回路を提供する。

【解決手段】半導体集積回路装置(100)は、抵抗値を切り替え可能な可変抵抗部(10)と、可変遅延部(20)と、データ取り込み部(26)とを具備する。抵抗値を切り替え可能な可変抵抗部(10)は、入力されるデータ信号(DT)をダンピングする。可変遅延部(20)は、データ信号(DT)の入力タイミングを示すクロック信号(CLK)に変更可能な遅延を与える。データ取り込み部(26)は、可変抵抗部(10)によってダンピングされた信号から可変遅延部(20)によって遅延された遅延クロック信号によって示されるタイミングでデータを取り込む。

(もっと読む)

信号伝送装置、信号伝送方法およびそのためのプログラム

【課題】信号線の数を増やさなくとも、複数の種類の信号を伝送できるようにする。

【解決手段】コマンドサンプリングユニット131は、ASICからの多重信号とクロック信号をそれぞれ入力し、クロック信号の立ち上がり時に、多重信号のレベルが“1”であった場合には、コマンド開始ビット信号が入力されたとみなし、以後に送信された4ビット分の信号をコマンドビット信号として認識する。そして、コマンドサンプリングユニット131は、入力したコマンドビット信号の4ビット分の内容に応じて、メイン制御部158に出力する信号を可変する。

(もっと読む)

受信装置及び通信システム

【課題】伝送路上のノイズによるメイン処理の実行効率低下が発生することなく、且つ、CPUなどに通信処理のための外部割込ポートを必要としない受信装置及び通信システムを提供する。

【解決手段】CPU11が第1サンプリング部21及び第2サンプリング部22を備え、第1サンプリング部21及び第2サンプリング部22が、プリアンブルの各ビットのビット幅と同じサンプリング周期で、且つ、ビット幅の1/2の時間ずらしたタイミングで、入力ポート11aに入力される2値信号のサンプリングを行う。第1サンプリング部21又は第2サンプリング部22の少なくとも一方でプリアンブルを検出した場合に、CPU11がデータの受信を開始することができる。リモコン3及びUHF受信IC12等は、プリアンブルに係る誤差が許容範囲内となるようにCPU11へ信号を送信する。

(もっと読む)

1 - 20 / 101

[ Back to top ]