Fターム[5K047GG24]の内容

デジタル伝送方式における同期 (12,489) | 網同期;クロック、ビット同期 (2,470) | クロックの伝送 (1,938) | クロックの受信 (1,715) | 受信信号よりタイミングの抽出 (1,089) | 抽出手段、原理 (419) | 受信信号特異点を利用 (164) | 立上り、立下り点 (109)

Fターム[5K047GG24]に分類される特許

1 - 20 / 109

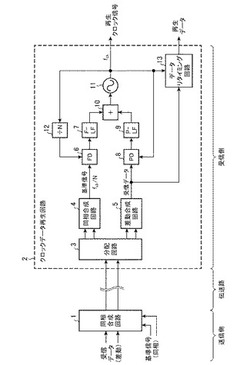

クロックデータ再生回路

信号伝送システム、信号送信装置およびクロックデータ再生回路

【課題】良好な通信品質で、高速な位相同期ループを得る。

【解決手段】送信側は、一方が差動信号であり他方が同相信号であるデータ信号および基準信号を同相合成し、一対の伝送路を通じて伝送する同相合成回路1を備え、クロックデータ再生回路2は、同相合成回路1からの信号からデータ信号および基準信号を分離する信号分離手段(分配回路3、同相合成回路4および差動合成回路5)と、データ信号と位相が同期した再生クロック信号を生成する再生クロック信号生成手段(位相比較回路8、位相同期ループ用ループフィルタ9および電圧制御発振器11)と、再生クロック信号を分周し、当該分周した信号の周波数を基準信号の周波数に同期させる制御信号を生成し、当該制御信号により再生クロック信号の周波数を制御する再生クロック信号収束手段(周波数比較回路6、周波数同期ループ用ループフィルタ7、電圧制御発振器11およびN分周回路12)とを備えた。

(もっと読む)

ゲーティッドVCO回路

【課題】ジッタやクロックデューティ比のずれが抑えられた良好なクロック成分を抽出する。

【解決手段】リング発振器20の位相調整回路21において、ゲート回路群22から出力された自走クロック信号CLKINNを入力とするMOSトランジスタQ1、およびゲーティング回路10からのゲーティング信号GOUTNを入力とするMOSトランジスタQ2の並列接続回路と、基準となるレファレンス電圧VREFを入力とするMOSトランジスタQ3とが差動対をなすCML回路を構成し、当該CML回路で得られた自走クロック信号CLKINNとゲーティング信号GOUTNとの論理和またはその反転論理をクロック出力信号CLKOUTとして出力する。

(もっと読む)

クロックデータリカバリ回路およびそれを内蔵する送受信半導体集積回路

【課題】高いジッタ耐性を有して多相クロックの位相数と消費電力と半導体チップ面積との増大を軽減する。

【解決手段】クロックデータリカバリ回路1のエッジ検出器105の複数のエッジ検出回路105Mの各回路は、第1と第2のエッジ検出回路105M1、2を含む。第1の検出回路105M1は受信データ信号のデータエッジがエッジ検出位相から−1位相よりも進相なことを検出して第1出力信号を生成して、第2の検出回路105M2は受信データ信号のデータエッジがエッジ検出位相から+1位相よりも遅相なことを検出して第2出力信号を生成する。第1または第2の出力信号に応答して、エッジ検出位相が−1位相分または+1位相分変更される。受信データ信号のデータエッジの±1位相の範囲内の存在が検出された場合には、次回のエッジ検出位相は現在の状態に維持される。

(もっと読む)

CDR回路

【課題】誤ロック状態を検出し、この誤ロック状態から復帰することが可能なCDR回路を提供する。

【解決手段】CDR回路は、受信データ信号のデータをサンプルすべきデータサンプリングクロックとして第1のクロックと、受信データ信号のエッジをサンプルすべきエッジサンプリングクロックとして第2のクロックと、を生成し、且つ第1のクロックおよび第2のクロックの位相を調整するクロックリカバリ回路を備える。CDR回路は、第1のクロックで受信データ信号をサンプルした結果をデータサンプリング結果として出力し、第2のクロックで受信データ信号をサンプルした結果をエッジサンプリング結果として出力する位相検出回路を備える。CDR回路は、エッジサンプリング結果と、予め設定されたデータパターンとを比較し、エッジサンプリング結果とデータパターンとが一致した場合、誤ロック状態であると判断し、誤ロック状態検出信号を出力する結果比較回路と、を備える。

(もっと読む)

トランシーバ

【課題】バス通信路にクロック成分とデータとを重畳して送信する通信システムにおいて、クロック成分を受信する側のノードからのデータ送信を可能とするためのトランシーバを提供する。

【解決手段】マスタからクロック成分を受信するスレーブのトランシーバでは、バス通信路を介したデータの送信が許可されている状態において(S101:YES)、スレーブの信号処理部からロウレベルの送信データが入力されると(S102:YES)、重畳用のロウレベルの信号をバス通信路5へ出力するための処理が行われる(S103〜S105)。具体的には、バス通信路上の信号の立ち下がりエッジが検出されると(S103:YES)、重畳用のロウレベルの信号を出力する期間が算出され(S104)、算出された期間継続してロウレベルの信号が出力される(S105)。

(もっと読む)

クロックデータ再生回路

【課題】VCOの発振周波数のばらつきを補償し、低ジッタで電源電圧・温度変動耐性が大きいクロックデータ再生回路を提供する。

【解決手段】ゲーティング回路と、再生クロックを出力する第1の発振回路と、第2の発振回路と、第2の発振回路が出力するクロックと参照クロックを周波数比較し、その周波数誤差に応じた周波数制御信号Aで第1〜第2の発振回路の発振周波数を制御するPLL手段とを備えたクロックデータ再生回路において、第2の発振回路の制御端子に周波数制御信号Aを入力し、第1の発振回路の制御端子に周波数制御信号Aと回路間ばらつき調整信号C1の加算信号を入力し、ゲーティング回路の制御端子に周波数制御信号Aと回路間ばらつき調整信号C2の加算信号を入力する構成である。

(もっと読む)

クロック再生回路

【課題】ジッタが小さく、面積が小さなクロック再生回路を提供する。

【解決手段】このクロック再生回路は、各UGにおける外部データ信号列Dinの最初の立ち上がりエッジに応答して論理レベルが反転される信号PD_Dinと、内部クロック信号VCOCLKに同期したクロック信号PD_Cinとを生成するエッジ抽出回路1と、信号PD_Dinとクロック信号PD_Cinの位相を比較し、比較結果を示す信号UP,DNを出力する位相比較器6とを備える。したがって、各UGで1回だけ位相比較を行なうので、データパターンに依存するジッタを抑制できる。

(もっと読む)

半導体集積回路装置、及び、クロックデータ復元方法

【課題】インターポレータ方式のクロックデータ復元回路において、インターポレータ回路の広帯域化を行わず、マルチレートに対応したクロックデータ復元回路を実現する。

【解決の手段】インターポレータ回路の生成クロックを分周し、リカバリクロックを生成する。また、インターポレータ回路が生成するクロックの位相を制御するポインタは分周前のクロックを使い、その他の回路は分周後のリカバリクロックを使い動作する。

(もっと読む)

トランシーバ

【課題】サンプリングに使用するクロックとは非同期に送信データが供給されるトランシーバにおいて、送信データの信号レベルを正しくサンプリングできるようにする。

【解決手段】送信データTXDのスタートビットの開始エッジのタイミング(開始タイミング)が検出されると、バスクロックBCKに同期し、そのバスクロックBCKの1周期当たり4個のサンプリング用エッジを有するサンプリングSCKを用い、開始タイミングを起点として2個目のサンプリング用エッジのタイミングで送信データTXDをサンプリングし、以後、4個目のサンプリング用エッジのタイミング毎に、送信データTXDをサンプリング(ラッチ)する。そのサンプリングしたデータを、更に、バスクロックBCKの立ち下がりエッジでサンプリングすることによって、バスクロックBCKに同期した同期送信データdTXDを生成する。

(もっと読む)

クロック発生回路、表示装置用駆動回路及びクロック発生回路の制御方法

【課題】電源投入時や通常動作時でも、より確実にクロックの生成が停止した状態から回復することが可能となるクロック発生回路を提供する。

【解決手段】クロック発生回路1は、クロックとデータとが重畳されたエンベデッド信号から抽出クロックを抽出するクロック抽出回路10と、前記エンベデッド信号と前記抽出クロックとに基づき前記抽出クロックの停止を検出し、前記クロック抽出回路を初期状態にリセットするリセット信号を出力する停止検出回路30と、を備えるものである。

(もっと読む)

バイフェーズ符号化データの復号化方法

【課題】バイフェーズ符号化データの復号化方法を提供する。

【解決手段】本発明のバイフェーズ符号化データの復号化方法は、バイフェーズ符号化データ中の立下りエッジ変換を検出することによって、隣り合う2つの立下りエッジ変換の間の時間差値及び前1ビットの論理値に基づき、相応する復号化を行い、時間差値が1個ビット周期であり且つ前1ビットが論理1である時、現在のビットが論理1であると判定し、時間差値が1個のビット周期であり且つ前1ビットが論理0である時、現在のビットが論理0であると判定し、時間差値が1.5個のビット周期であり且つ前1ビットが論理1である時、現在及び後1ビットが何れも論理0であり、時間差値が1.5個のビット周期であり且つ前1ビットが論理0である時、現在のビットが論理1であると判定し、時間差値が2個のビット周期であり且つ前1ビットが論理1である時、現在及び後1ビットがそれぞれ論理0及び1であると判定する。

(もっと読む)

同期化回路及び同期化方法

【課題】短時間に受信側クロックで位相を同期化すること。

【解決手段】受信したデータを同期化する同期化回路10は、位相差判定回路15と第1のFF11と第2のFF12とを有する。位相差判定回路15は、同期化回路10と接続された他装置から受信したデータを同期化回路の内部クロックの位相で受付けた場合、データを安定に捉えられるか否かを判定する。第1のFF11は、位相差判定回路15によってデータを内部クロックの位相で安定に捉えられると判定された場合、データと内部クロックとを受付け、データを内部クロックの位相で捉えて同期化する。第2のFF12は、位相差判定回路15によってデータを内部クロックの位相で安定に捉えられないと判定された場合、データと位相が反転された内部クロックとを受付け、データを位相が反転された内部クロックの位相で捉えて同期化する。

(もっと読む)

シリアル・データ通信装置のDPLL回路

【課題】PLCで設計・構成するシリアル・データ通信の高速化を図ることができ、しかも受信データのジッタ許容範囲を明確にできる。

【解決手段】DPLL回路10のうち、データシフト回路DS1〜DS3は受信データからソースクロックCLKで同期を取った複数のシリアル・データを生成する。排他的論理和回路EX_ORは一対のシリアル・データから受信データの変化点を検出する。カウンタDPLCNTは、最大カウント値nが設定され、変化点から次の変化点までをソースクロックをカウントする。一致判定回路ANDはカウンタのカウント値が予め設定したカウント値n/2に一致したときに受信クロックとして出力する。ハイレベル・データ・リンク・コントローラ・モジュール(HDLC−IP)20は、受信クロックを使って受信データ(シリアル・データ)の転送制御を行う。

(もっと読む)

適応型受信システム、適応型送受信システム及び複数チャネル送受信システム

【課題】ロックポイント付近におけるサンプリングクロックの位相の調整と、イコライザ部の制御とを安定させ、ジッタトレランスを高める。

【解決手段】位相比較部は、サンプリングタイミングとサンプリングタイミングよりも第一の所定位相分前のタイミングとの間の第一区間に、等化信号EQDATAのエッジが存在するか否かを示す位相比較信号LAG(n)を出力するとともに、サンプリングタイミングとサンプリングタイミングよりも第二の所定位相分後のタイミングとの間の第二区間に、等化信号EQDATAのエッジが存在するか否かを示す位相比較信号LEAD(n)を出力する。判定部は、検出データパターンの各ビットに対応する位相比較信号LAG(n),LEAD(n)の出力パターンを所定の比較対象パターンと比較し、合致するか否かに基づいて、等化信号EQDATAの1ビットがサンプリングクロックCKの1周期よりも長いか短いかを判定する。

(もっと読む)

データ復元回路及びデータ復元方法

【課題】孤立パルスを確実に検出してデータ判定を実行できるデータ復元回路を提供する。

【解決手段】データ復元回路は、デジタルデータの列のうち2つの連続するデジタルデータを用いて、内挿により第1のデータ切り替わり点の位置を算出すると共に、外挿により第2のデータ切り替わり点の位置を算出する位相検出器と、第1のデータ切り替わり点の平均位置と瞬時位置とに基づいてデジタルデータの列からデータ判定値の列を抽出するデータ判定部と、2つの連続するデジタルデータに挟まれた時間軸上の区間の内に、直前の2つの連続するデジタルデータの外挿直線及び直後の2つの連続するデジタルデータの外挿直線からそれぞれ求めた2つの第2のデータ切り替わり点が位置し且つ2つの外挿直線の傾きの符号が互いに異なる場合、データ判定値の列の当該区間に対応するデータ判定値を、外挿により推定されるデータ値で置き換えるデータ選択部を含むことを特徴とする。

(もっと読む)

CDR回路

【課題】前段の光受信装置のスケルチ機能の有無に関係なく汎用的に使用可能なCDR回路を提供する。

【解決手段】CDR回路は、入力データ1に同期した再生クロック2を出力するG−VCO14と、入力データ1の識別再生を再生クロック2に基づいて行うフリップフロップ回路12と、G−VCO14と同一周波数のクロックを出力するサブVCO15と、再生クロック2とサブVCO15の出力クロック4のいずれかを選択する選択回路17と、選択回路17の出力クロック8と参照クロック6とを周波数比較しその周波数差に応じた周波数制御信号5を出力する周波数比較器16とを備える。選択回路17は、少なくとも入力データ1が無信号である期間においてサブVCO15の出力クロック4を選択し、残りの期間において再生クロック2を選択する。

(もっと読む)

光受信装置

【課題】連続信号対応の汎用的なCDR回路を備えた制御LSIに、応答特性を損なうことなくシリアルデータ信号を入力する。

【解決手段】光受信装置は、データ信号期間/無信号期間を問わず信号を出力し続けるLA回路6と、LA回路6の出力信号からクロックを抽出しデータを再生するバーストCDR回路2とを備える。バーストCDR回路2は、LA回路6の出力信号とタイミングの合った再生クロックを出力する第1の電圧制御発振器と、第1の電圧制御発振器と同一の周波数で発振する第2の電圧制御発振器と、第2の電圧制御発振器の出力と参照クロックとを周波数比較して、第1、第2の電圧制御発振器を所望のデータレート周波数で発振させる周波数制御信号を出力する周波数比較器と、LA回路6の出力信号の識別再生を再生クロックに基づいて行う識別回路とを有する。

(もっと読む)

CDR回路

【課題】ジッタの抑圧と応答時間の短縮とを両立させる。

【解決手段】CDR回路は、入力データ4が遷移したときにパルスを出力するゲーティング回路10と、ゲーティング回路10の出力パルスのタイミングに合うように出力クロックの位相を調整するG−VCO11と、G−VCO11の出力クロックのタイミングに合うように再生クロック7の位相を調整するVCO12と、入力データ4のデータ識別を再生クロック7に基づいて行うフリップフロップ回路3と、入力データ4のデータ信号期間の少なくとも一部において、ゲーティング回路10の出力パルスが再生クロック7に与える影響を、入力データ4の同期信号期間と比較して小さくするよう制御する可変減衰器16とを備える。

(もっと読む)

CDR回路および受信回路

【課題】参照クロックが不要なインタポレータ方式のCDR回路を小面積で実現することができる技術を提供する。

【解決手段】CDR回路101において、再生クロックのエッジの近傍と遠方にある伝送データのエッジの個数を計測するデータエッジ位置計測回路117と、伝送データのエッジの近傍と遠方にある再生クロックのエッジの個数を計測するクロックエッジ位置計測回路118とを含み、データエッジ位置計測回路117の計測結果とクロックエッジ位置計測回路118の計測結果に応じて、再生クロックの周波数を調整する周波数調整回路116を有する。エッジの近傍と遠方の判定には、CCL回路の最小入力振幅を制御することで実現している。

(もっと読む)

1 - 20 / 109

[ Back to top ]