Fターム[5K047GG25]の内容

デジタル伝送方式における同期 (12,489) | 網同期;クロック、ビット同期 (2,470) | クロックの伝送 (1,938) | クロックの受信 (1,715) | 受信信号よりタイミングの抽出 (1,089) | 抽出手段、原理 (419) | 受信信号特異点を利用 (164) | ゼロクロス点 (17)

Fターム[5K047GG25]に分類される特許

1 - 17 / 17

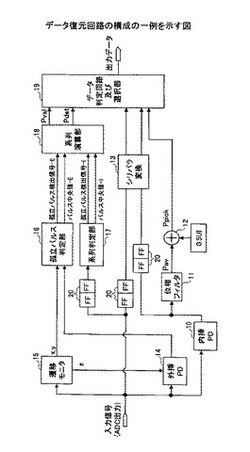

データ復元回路及びデータ復元方法

【課題】孤立パルスを確実に検出してデータ判定を実行できるデータ復元回路を提供する。

【解決手段】データ復元回路は、デジタルデータの列のうち2つの連続するデジタルデータを用いて、内挿により第1のデータ切り替わり点の位置を算出すると共に、外挿により第2のデータ切り替わり点の位置を算出する位相検出器と、第1のデータ切り替わり点の平均位置と瞬時位置とに基づいてデジタルデータの列からデータ判定値の列を抽出するデータ判定部と、2つの連続するデジタルデータに挟まれた時間軸上の区間の内に、直前の2つの連続するデジタルデータの外挿直線及び直後の2つの連続するデジタルデータの外挿直線からそれぞれ求めた2つの第2のデータ切り替わり点が位置し且つ2つの外挿直線の傾きの符号が互いに異なる場合、データ判定値の列の当該区間に対応するデータ判定値を、外挿により推定されるデータ値で置き換えるデータ選択部を含むことを特徴とする。

(もっと読む)

信号配線システム及びジッタ抑制回路

【課題】従来は、信号配線のジッタ量を削減しつつ、回路規模の増大化を抑制することが難しかった。

【解決手段】差動信号を出力する出力部と、前記出力部からの前記差動信号を受信する受信部と、前記受信部が受信する前記差動信号のジッタ量を、抑制係数に応じて抑制するジッタ抑制回路と、前記出力部からの前記差動信号を伝達し、前記ジッタ抑制回路の前記抑制係数に応じた配線長を有する信号配線部と、を有する信号配線システム。

(もっと読む)

受信回路、送信回路、通信システム、及び通信システムの送信設定方法

【課題】信号遷移発生用の符号化を用いることなくデータとクロックとを1つの信号に纏めて送受信可能な送信回路及び受信回路を提供する。

【解決手段】送信回路は、データ信号とクロック信号とを重み付け加算することにより生成した信号を送信する。また受信回路は、受信した第1の信号の信号遷移からクロック信号を抽出するクロック抽出回路と、抽出されたクロック信号を第1の信号から減算することにより第2の信号を生成する減算回路と、抽出されたクロック信号に応じたタイミングにおいて第2の信号をデータ判定するデータ判定回路とを含む。

(もっと読む)

交流信号のゼロクロス点検出装置及びこれを用いた信号伝送システム

【課題】ゼロクロス点を高精度に検出することが可能な交流信号のゼロクロス点検出装置及びこれを用いた信号伝送システムを提供する。

【解決手段】交流電圧E1を分圧し、且つ平滑化した電圧を基準電圧V1として設定する。また、交流電圧E1を分圧した電圧を参照電圧Vrefとする。そして、基準電圧V1と参照電圧Vrefを比較し、VrefがV1を上回る地点をゼロクロス点として設定する。このような構成によれば、交流電圧E1の振幅が変動した場合であっても、この変動に伴って基準電圧V1が変動するので、高精度にゼロクロス点を検出することができる。このため、例えば、PLC通信等で交流電圧に送信信号を重畳する場合には、高精度な信号伝送が可能となる。

(もっと読む)

PCM信号復調回路、該復調回路に用いられるPCM信号復調方法及びPCM信号復調プログラム

【課題】入力PCM信号にノイズが含まれている場合でも、高精度で復調するPCM信号復調回路を提供する。

【解決手段】復調タイミング判定手段(タイミング制御部24、ローカルクロック25、PLL26、エンベロープ予測部27)は、ゼロクロス検出信号zbを入力すると共にピーク検出信号pbを入力して入力PCM信号ibの1周期分の位相及び振幅を含むデータptを生成し、エンベロープデータとして蓄積して基準位相標本情報及び基準周期情報を作成すると共に、基準位相標本情報及び基準周期情報に基づいて、入力PCM信号ibの後続の周期の位相及び振幅の予測情報efを作成し、予測情報efと後続の周期の位相及び振幅とを比較して誤差が所定の範囲内にあるとき、復調タイミング信号tcを出力する。復調部28により、復調タイミング信号tcに同期して復調データmdが出力される。

(もっと読む)

瞬時に同期を確立しかつ保持できる同期発振器

【課題】瞬時に同期を確立し、比較的に長時間、同期状態を高精度で保持することができる同期発振器を安価に実現する。

【解決手段】少なくとも、セットもしくはリセット付きカウンタ22と同期検出手段24とから構成され、前記同期検出手段24において、同期入力信号の立上り点、立下り点、もしくはゼロ交差点のタイミングを検出し、前記タイミングにおいて、前記カウンタ22をセットしあるいはリセットすることで、同期入力信号と瞬時に同期を確立し、前記同期入力信号が休止しあるいは停止した場合、あるいは取去られた後にも、比較的に長時間、同期状態を高精度で保持することができる。

(もっと読む)

信号処理装置、タイミング同期回路、信号処理方法、及びタイミング同期方法

【課題】遅延を用いずにデータ信号とクロックとを同期させるタイミング同期回路を提供すること。

【解決手段】入力信号を立ち上がり又は立ち下がりタイミングでトグルするトグル回路と、クロックと前記トグル回路の出力信号とが入力され、当該トグル回路の出力信号を前記クロックの立ち上がり又は立ち下がりタイミングに同期させる第1同期回路と、前記トグル回路の出力信号と前記第1同期回路の出力信号とが入力され、入力された両出力信号の排他的論理和を出力する排他的論理和回路と、前記クロックと前記排他的論理和回路の出力信号とが入力され、当該出力信号を前記クロックの立ち下がり又は立ち上がりタイミングに同期させる第2同期回路と、を備える、タイミング同期回路が提供される。

(もっと読む)

クロック生成回路

【課題】高速動作するクロック・データリカバリのための正確なクロック信号を生成するクロック生成回路を提供する。

【解決手段】クロック生成回路は、第1入力電圧に応じて第1周波数信号を出力する第1電圧制御発振回路と、第2入力電圧に応じて第2周波数信号を出力する第2電圧制御発振回路と、制御信号を受け取り、第1周波数信号と第2周波数信号との位相差が制御信号に応じた値になるように第1入力電圧と第2入力電圧とを制御する位相調整回路と、第1周波数信号に同期して受信信号を検出して出力する第1判定回路と、第2周波数信号に同期して受信信号を検出して出力する第2判定回路と、第1判定回路の出力と第2判定回路の出力とに基づいて受信信号の位相を検出し、その位相検出の結果に応じて第1入力電圧と第2入力電圧とを制御する位相検出器とを含む。

(もっと読む)

高速シグナリングシステムにおける過渡事象時の位相誤差を補正する方法および装置

送信器と受信器との間でのデータ通信中に過渡事象によって引き起こされる、データとタイミング基準信号との間の位相誤差を動的に補正するシステムについて記載されている。本システムは、動作中に、過渡事象に対する1つ以上の位相オフセット値をオフセットテーブルに格納する。構成要素である位相オフセット値は、過渡事象によって引き起こされる位相誤差に関連付けられている。本システムは、その過渡事象の次の発生を検出すると、1つ以上の位相オフセット値に基づいて、データとタイミング基準信号との間の位相関係を調節する。 (もっと読む)

クロック再生回路

【課題】エッジ検出やクロック成分抽出を差動回路で行うとともに遅延手段を不要にし、チップ面積の縮小化が図れ、ビットレートフリー動作が可能で低消費電力のクロック再生回路を提供すること。

【解決手段】2入力データを増幅し、差動データを出力する少なくとも1つの差動回路と、この差動回路と縦続接続され、基準電圧と差動出力データとの交点電圧の差に基づきクロック信号成分を抽出するクロック成分発生回路、とで構成されたことを特徴とするクロック再生回路。

(もっと読む)

シンボルタイミング検出装置及び無線端末装置

【課題】受信された変調信号のシンボルタイミングを検出して当該変調信号を復調する無線端末装置で、無線通信を行う無線周波数に周波数偏差が生じても、安定してシンボルタイミングを制御する。

【解決手段】サンプリング手段103がシンボル周期より短い周期で変調信号の信号値をサンプリングする。抽出手段117が複数のサンプリング点における信号値の中からシンボルタイミングの位置にあるとみなされる信号値を抽出し、復調手段107が抽出された信号値について復調を行う。サンプリング点復調手段110が各サンプリング点における信号値について復調を行い、値検出手段201が各サンプリング点における復調結果の電力値を検出し、シンボルタイミング制御手段113〜116が各サンプリング点における電力値に基づいて抽出手段117によりシンボルタイミングであるとみなすタイミングを制御する。

(もっと読む)

復調方法及び復調回路

【課題】パケット無線通信方式等において、同期追従精度を向上させる。

【解決手段】復調回路は、受信信号INを検波する周波数検波部10と、検波結果を復調して復調信号OUTを出力する受信信号判定部11と、復調信号OUTのフレーム長の長短を比較判定するフレーム長比較部16と、検波結果に対して同期を捕捉する同期捕捉部13と、検波結果に対して同期を追従させる同期追従部14と、同期捕捉部13で生成したゼロ交差点のポジション情報P1又は同期追従部14で生成したゼロ交差点のポジション情報P2のいずれか一方を用いて受信信号判定部11で使用するポジション情報P3を生成する再生搬送波発生部15とを有している。そして、受信信号INのデータフォーマットに含まれるフレーム長情報を使用し、フレーム長比較部16の出力により、同期追従動作を動作/停止させるようにしている。

(もっと読む)

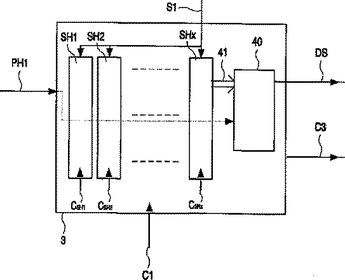

ビット検出装置及び情報再生装置

振幅を有するアナログ信号(AS)を、当該アナログ信号(AS)が導出されるビット列を表すデジタル信号(DS)に変換することができるビット検出装置が開示される。ビット検出装置は、量子化されたアナログ信号とクロック信号C2との間の位相差を検出する位相検出器を有する。位相差は、AD変換器によってサンプリングされる。前記位相差が低周波信号であるので、AD変換器は、比較的遅いレートでサンプリングすることができる。サンプリングされた位相差は、位相信号PH1を出力するデジタルPLLに供給される。位相信号及び量子化されたアナログ信号は、前記デジタル信号(DS)を再現するために用いられる。本発明は、前記ビット判断ユニットが更に、−クロック信号CSH2を用いて前記出力信号S1をサンプリングすることができる少なくとも1つの追加のサンプル及び保持ユニットSH2であって、前記クロック信号CSH2の周波数はクロック信号CSH1の周波数に等しく、前記クロック信号CSH2の位相は、前記クロック信号CSH1の位相とは大幅に異なる、サンプル及び保持ユニットSH2と、−前記のサンプル及び保持ユニットSH1又はSH2のサンプルを出力するための出力ユニットであって、前記位相信号PH1が前記位相差ΔP1は第1の領域にあることを示すときには前記サンプル及び保持ユニットSH1のサンプルが出力され、前記位相信号PH1が前記位相差ΔP1は第2の領域にあることを示すときには前記追加のサンプリング及び保持ユニットSH2のサンプルが出力される、出力ユニットとを有することにより特徴付けられる。これは、位相ジッタがある場合に発生するビットエラーの変更が低減されるという利点を有する。  (もっと読む)

(もっと読む)

クロック再生回路

【課題】 多値データを受信する受信回路のクロック再生回路のジッタを抑える。

【解決手段】 各コンパレータS1、S2、S3は、対応する基準電圧と入力信号とを比較し、フリップフロップ回路FF1a〜FF3a、FF1b〜FF3bは、その比較結果を記憶する。位相調整回路T1は、フリップフロップ回路FF1a〜FF3a、FF1b〜FF3bで記憶されたデータから連続する3つのデータを再生する。PLL回路P1は、転属する3つのデータの信号波形が対称形に変化した場合には、3つのデータの内の中央のデータの変化タイミングで再生クロックの位相を制御し、信号波形が対称形でなければ、中央のデータの変化タイミングでは再生クロックの位相を制御しないで次のタイミングを待つ。

(もっと読む)

デジタル光伝送システムにおけるクロック信号の回復のための光電的位相調整回路

例えば光受信器、アド・ドロップ機能を有するマルチプレクサまたは3R再生器におけるクロック信号の簡単な回復のための公知の位相調整回路は、データ信号および帰還されたクロック信号から位相コンパレータにおいて重畳される比較信号および変化されないデータ信号を別の比較信号として差動増幅器に供給し、差動増幅器の調整信号が発振器に印加されてクロック信号が調整設定される。しかしクロック回復の安定性は非常に高いデータレート、例えば160Gbit/sにおいて殊に不満足である。それ故に、クロック信号(TS)の微分的な回復が行われる本発明の位相調整回路(PLL)では、出力結合されたデータ信号(DS)は位相遅延エレメント(DELAY)を介して同様に位相コンパレータ(PC)に導かれる。位相シフトが相互に調整設定可能である比較信号(DCS,CCS)を用いた位相コンパレータ(PC)の作動により、微分位相評価が可能にある。これにより動作点が送信チャネルの出力に無関係に常に調整領域の真ん中にある調整信号(RS)が生じる。従って本発明の微分式クロック回復において出力変動、SN比、パルス形態および伝送されるビットパターンの依存性は大幅に低減される。クロック回復の長時間安定性は著しく改善される。  (もっと読む)

(もっと読む)

タイミング復元方法及びタイミング復元装置

【課題】タイミング復元方法及びタイミング復元装置が開示される。

【解決手段】サンプリングクロックによって一定の位相間隔で入力信号をサンプリングして、2つの連続したサンプリング値を生成する段階、2つの連続したサンプリング値に基づいてサンプリング傾斜を算出する段階、及び算出されたサンプリング傾斜とターゲット傾斜との差異を利用してサンプリングクロックの位相を補正する段階を含んでタイミング復元方法を構成する。又、2つの連続したサンプリング値を合算して入力信号ゲインを算出する段階、及び算出された入力信号ゲインとターゲットゲインの比率を前記ターゲット傾斜にかけて前記ターゲット傾斜を補正する段階を更に含んでタイミング復元方法を構成することによって、サンプリングクロックの位相は算出されたサンプリング傾斜と補正されたターゲット傾斜との差異に基づいて補正されることができる。

(もっと読む)

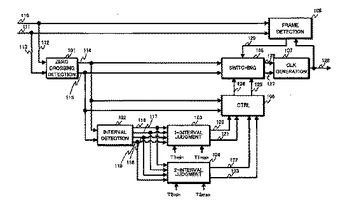

クロック再生回路およびこれを用いた受信装置

信号からシンボルの識別点判定のためのクロック再生回路において、信号に周波数ずれや雑音を含むと、クロック再生の位相引き込みが困難になる。

検波信号には、シンボル交番するプリアンブル部を先頭として、ユニークワード部とデータ部とが含まれている。ゼロクロス検出部は、検波信号の符号変化であるゼロクロスを検出し、ゼロクロス間隔検出部はゼロクロスが発生した時間間隔をカウントする。ゼロクロス1間隔判定部は、ゼロクロス間隔信号が所定範囲内であるかを判定し、ゼロクロス2間隔判定部は、隣接する2つのゼロクロス間隔信号を加算し、ゼロクロス2間隔信号が所定範囲内であるかを判定する。ゼロクロス制御部は、判定結果をもとにゼロクロス信号を制御して、有効ゼロクロス信号を出力する。ゼロクロス切替部はフレーム受信検出部が出力するフレーム受信信号をもとにゼロクロス信号と有効ゼロクロス信号とを切り替え、有効位相誤差情報を出力する。クロック生成部は有効位相誤差情報を入力として、シンボルクロックを生成する。  (もっと読む)

(もっと読む)

1 - 17 / 17

[ Back to top ]