Fターム[5K047KK04]の内容

デジタル伝送方式における同期 (12,489) | 監視;試験 (340) | 監視、試験項目 (214) | 異常状態検出 (142) | 同期はずれ(同期状態)検出 (77)

Fターム[5K047KK04]に分類される特許

1 - 20 / 77

クロック供給方法およびクロック供給装置

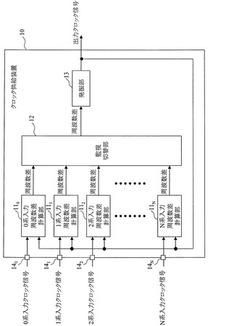

【課題】本発明は、クロック基準信号が異常な場合においてもクロックパスの監視が可能であり、かつ、正常系のクロックパスへの切替を可能とすることを目的とする。

【解決手段】本願発明のクロック供給装置10は、3つ以上のクロック入力部140〜14Nと、クロック入力部140〜14Nから入力されたいずれかのクロック周波数で発振する発振部13と、クロック入力部140〜14Nからの各入力クロック信号の周波数と発振部13の発振周波数との各周波数差を計算する周波数差計算部110〜11Nと、周波数差計算部110〜11Nからの各周波数差が予め定められた閾値を超えたか否かを判定し、閾値を超えたクロックパスの個数と閾値を超えていないクロックパスの個数に関して多数決を用いて比べることにより各クロックパスが正常であるか、異常であるかを判定する監視切替部12と、を備える。

(もっと読む)

CDR回路及びCDR方法

【課題】ロック状態であるか否かを検出し、その検出結果を出力するCDR回路及びCDR方法を提供する。

【解決手段】受信データ信号をサンプリングするデータサンプリングクロック信号に同期して、受信データ信号をサンプリングしてサンプルドデータ信号を生成するデータサンプリング回路、データサンプリングクロック信号に対して位相がずれたエッジサンプリングクロック信号に同期して、受信データ信号をサンプリングしてサンプルドエッジ信号を生成するエッジサンプリング回路、データサンプリングクロック信号に同期して、受信データ信号の振幅と基準電圧との比較結果信号を出力する振幅比較回路を備え、比較結果信号、サンプルドデータ信号およびサンプルドエッジ信号に基づいて、データサンプリングクロック信号の位相を調整する位相シフタ回路、及び受信データ信号とデータサンプリングクロック信号との位相関係を検出するロック検出回路を備える。

(もっと読む)

CDR回路

【課題】誤ロック状態を検出し、この誤ロック状態から復帰することが可能なCDR回路を提供する。

【解決手段】CDR回路は、受信データ信号のデータをサンプルすべきデータサンプリングクロックとして第1のクロックと、受信データ信号のエッジをサンプルすべきエッジサンプリングクロックとして第2のクロックと、を生成し、且つ第1のクロックおよび第2のクロックの位相を調整するクロックリカバリ回路を備える。CDR回路は、第1のクロックで受信データ信号をサンプルした結果をデータサンプリング結果として出力し、第2のクロックで受信データ信号をサンプルした結果をエッジサンプリング結果として出力する位相検出回路を備える。CDR回路は、エッジサンプリング結果と、予め設定されたデータパターンとを比較し、エッジサンプリング結果とデータパターンとが一致した場合、誤ロック状態であると判断し、誤ロック状態検出信号を出力する結果比較回路と、を備える。

(もっと読む)

時刻制御装置及び時刻制御方法

【課題】複数の子局が有しているRTCの誤差を削減する時刻制御装置及び時刻制御方法を提供することを目的としている。

【解決手段】衛星から情報を受信し、受信した情報に基づき第1クロック信号を生成する第1クロック生成部と、第2クロック信号を生成する第2クロック生成部と、第1クロック信号と第2クロック信号との誤差を検出する誤差検出部と、誤差検出部が検出した誤差が予め定められている値より大きい場合、第2クロック生成部が生成する第2クロック信号を調整する制御部と、を備える。

(もっと読む)

送信装置、受信装置、シリアル通信装置、及び、その装置を備えた記録装置

【課題】受信側の1ビット分のサンプリングクロックの周期に対して送信クロックの周期が変動すると受信エラーが発生する。

【解決手段】受信データ列の中で、サンプリングデータが反転する毎にサンプリングクロックを再同期をとる。更に、同じデータが所定数連続する場合は、反転するダミービットを挿入して再同期をとれるように構成する。

(もっと読む)

通信装置、制御信号生成方法、シャッターメガネ、及び通信システム

【課題】 受信データから得られる基準タイミングに基づいた表示装置等の被制御装置の制御を遅延なくかつ低消費電力で可能にする通信装置、その被制御装置を制御するための制御信号生成方法、受信データから得られる基準タイミングに基づいたシャッターの開閉を遅延なくかつ低消費電力で可能にするシャッターメガネ、及び基準タイミングを表すデータの送受信を遅延なくかつ低消費電力で可能にする通信システムを提供する。

【解決手段】 間欠的に到来するデータ内に所定の基準タイミング信号パターンが存在するか否かを識別するタイミング信号識別手段と、タイミング信号識別手段によって所定の基準タイミング信号パターンの存在が識別された場合に被制御装置に対する制御信号を生成する制御信号生成手段と、通信装置の制御を司る制御手段と、を備える。

(もっと読む)

受信装置、受信方法、およびプログラム

【課題】データの欠損によるタイミングの変化に迅速に対応することができるようにする。

【解決手段】受信装置は、同期回路14と等化回路15を備える。同期回路14の検出器33は、受信信号のデータの欠損を検出し、検出結果を等化回路15の等化器42に供給する。等化器42は、データの欠損の検出結果に基づいて、データの欠損量だけ処理タイミングを調整する。この開示の技術は、例えば、データの欠損が生じ得る受信信号を受信する受信装置に適用できる。

(もっと読む)

通信装置及び通信方法

【課題】PLL回路をベースとしたCDR回路を使用したトランシーバ間において、再同期を高速に行うことを目的とする。

【解決手段】PLL回路により構成されるクロック抽出部16に、受信信号を受信していない非受信状態の場合には、受信信号を受信している受信状態から非受信状態へ移行する時点におけるクロック信号の位相を示す位相情報を保持しておく受信側位相保持部22を追加する。データ送信時には、受信側位相保持部22が保持した位相情報を用いて生成されたクロック信号を用いて送信データを送信する。

(もっと読む)

無線通信装置

【課題】対象装置からの信号に基づいて当該対象装置と同期をとる構成において、非同期状態から同期状態へ早期に復帰することが可能な無線通信装置を提供する。

【解決手段】無線通信装置201は、対象装置から受信した受信データに基づいて生成された再生タイミング信号に基づいて第1の制御電圧を生成し、電圧制御発振器25に第1の制御電圧を供給することにより、再生タイミング信号の周波数成分のうち、所定の周波数以上の成分が減衰された周波数成分を有し、かつ再生タイミング信号に同期する基準タイミング信号を生成するためのジッタ抑圧部12と、タイミング信号生成部22によって生成される再生タイミング信号の異常を検知し、異常を検知した場合には、第1の制御電圧の代わりに、第1の所定範囲内の電圧である第2の制御電圧を電圧制御発振器25に供給するための発振器制御部13とを備える。

(もっと読む)

情報受信制御装置、情報受信制御方法、情報受信制御プログラムおよび記録媒体

【課題】調歩同期式のシリアル通信における通信データのサンプリングタイミングを簡単な回路構成によって制御することで通信データ単位でのサンプリング誤差の累積を防止し、通信データの受信エラーの発生を抑止することができるようにした情報受信制御装置、情報受信制御方法、情報受信制御プログラムおよび記録媒体を提供する。

【解決手段】調歩同期式のシリアル通信に用いられるビット単位の通信データの受信の際に、「基準クロックを分周したカウンタークロック」のカウンタークロック数に対する、「基準クロックから算出される分周値をもとにハード特性を考慮した特性分周値」を計算する。分周値と特性分周値を用いて算出されるそれぞれのカウンタークロックに基づく誤差からビット単位での誤差量を算出し、その誤差量をもとにカウンタークロック数の計数を行う際の初期値を決定する。

(もっと読む)

伝送装置および伝送方法

【課題】 伝送装置全体の構成を変えることなく、新たに外部から網同期用のクロック信号を容易に取得することができる技術を提供することを目的とする。

【解決手段】 収容する通信端末を増設する拡張部と、拡張部に収容された通信端末とネットワーク網との間でデータ伝送する伝送部と、拡張部と伝送部とを通信可能に接続する接続部とを有する伝送装置であって、伝送部は、通信端末を制御監視しデータ伝送を制御する制御部を備え、拡張部は、通信端末をネットワーク網と同期させるためのクロック信号を外部から受信する外部クロック受信部を備え、接続部は、外部クロック受信部によって受信されたクロック信号を制御部へ転送し、制御部は、転送されたクロック信号に基づいて、通信端末をネットワーク網と同期させてデータ伝送させる。

(もっと読む)

中継装置及び同期維持方法

【課題】移動通信装置と基地局との間にRNが配置され、CRSを受信することができない場合においても、RNと基地局装置との間の同期が維持することができる中継装置及び同期維持方法を提供すること

【解決手段】本発明にかかる中継装置30は、移動通信装置10と基地局装置20との間に配置される。中継装置30は、基地局装置20からユーザデータを送信するデータ領域に設定された参照信号を用いて基地局装置20との同期を維持する基地局同期確立部31を備える。基地局同期確立部31は、基地局装置20から参照信号が送信されないことにより、基地局装置20との同期が解除された場合に、中継装置30から周辺基地局装置に対する初期アクセス時に用いられる同期確立手順を用いて、基地局装置20との同期を確立するものである。

(もっと読む)

無線通信装置

【課題】誤同期の直後であっても正規の無線信号を正しく受信することができる無線通信装置を提供する。

【解決手段】演算処理ブロック1の命令デコード部29が、同期検出部27がフレーム同期検出信号の出力を開始してから当該フレーム同期検出信号の出力を停止するまでの間に受信データ出力命令を受け取らなかった場合、同期検出部27が次回のフレーム同期検出信号の出力を開始するまでの間に演算処理ブロック1の中央演算処理部10から受信データ出力命令が出力されても、受信データバッファ25に蓄積されている受信データを出力させないようにしている。その結果、誤同期の直後であっても正規の無線信号を正しく受信することができる。

(もっと読む)

アライメントマーカ重複判定回路、アライメントマーカ重複判定方法およびプログラム

【課題】データを複数のレーンに振り分け、レーン毎にアライメントマーカを挿入して行われるデータ通信における、アライメントマーカの誤設定を検出する。

【解決手段】受信装置に含まれる整列同期回路において、アライメントマーカ検出回路110−0〜110−(n−1)がライン0〜ライン(n−1)に含まれるアライメントマーカを検出する。そして、検出されたアライメントマーカの示すレーン番号が複数のラインについて同一であると判定した場合に、レーン番号重複判定回路130がアライメントマーカ重複を示す信号を出力する。

(もっと読む)

デスキュー装置およびデスキュー処理方法

【課題】全レーンにおける全スキューパターンを補正する従来技術と比較して、より短時間でデスキューを完了することのできるデスキュー装置を得る。

【解決手段】DQPSK変調方式を適用し、送信機(10)のプリコーダの内側にプリスキュー回路(13)が設けられており、Iチャネル、Qチャネルそれぞれ3レーン以上の複数レーンで構成され、干渉するレーンがIチャネル、Qチャネルそれぞれ2レーンであり、複数レーンの信号をパラレル伝送した際に発生するレーン間のスキューを除去するデスキュー処理を行うデスキュー装置であって、オフラインでトレーニングを送信することによりデスキュー処理を行う際に、1レーンずつトレーニングを送信することで、Iチャネルの複数レーンと、Qチャネルの複数レーンのタイミングが一致するレーンの組み合わせを順次特定していく。

(もっと読む)

無線基地局装置

【課題】信頼性の高い無線基地局装置を提供する。

【解決手段】

無線基地局装置として、サーデスインターフェイスを持つ大電力増幅器を備えた無線部(RE)と、当該無線部を制御する上位装置である無線制御部(REC)とを用いて構成する。この無線部は、サーデスから再生クロックを抽出するデータ/クロック再生回路部を備える。抽出された再生クロックは、多出力位相同期回路部を用いて、各部と同期させられる。また、サーデスの異常を検知して、このクロックの同期状態を監視する監視回路部を備える。

(もっと読む)

デジタル信号処理回路、デジタル信号処理方法、及び、プログラム

【課題】セットアップタイム及びホールドタイムのマージンを十分に確保することが可能なデジタル信号処理回路を提供すること。

【解決手段】回路は第1の遅延量を複数の判定用遅延量のそれぞれに設定する。回路は入力データ信号を、第1の遅延量だけ遅延させた第1の遅延データ信号と第2の遅延量だけ遅延させた第2の遅延データ信号とを出力する。回路は、第1の遅延データ信号をラッチすることにより第1のラッチデータを取得し、第2の遅延データ信号をラッチすることにより第2のラッチデータを取得する。回路は、複数の判定用遅延量のそれぞれに対して、第1のラッチデータと第2のラッチデータとが一致しているか否かを判定し、当該判定結果に基づいて第1のラッチデータと第2のラッチデータとを一致させるように、第1の遅延量を第1の制御遅延量に設定し且つ上記第2の遅延量を第2の制御遅延量に設定する。

(もっと読む)

同期データ検出装置、同期データ検出方法及びプログラム

【課題】パケット抜けなく同期データの有無の検出を行うことができる同期データ検出装置を提供する。

【解決手段】同期バイト検出部5は、所定の同期データを含むTSデータを記憶するメモリからTSデータを所定の単位で順次読み込み、所定の同期バイトを検出する0x47検出器22と、0x47検出器22において所定の同期バイトを検出した回数をカウントするカウンタ25と、0x47検出器22が、最初の所定の同期バイトを検出した後、所定の周期でTSデータを読み込ませ、0x47検出器22が所定の周期で所定の同期バイトを連続して所定の回数検出しない場合は、0x47検出器22に対して、最初の所定の同期バイトの次のTSデータから順番に読み込ませる判定指示部24とを有する。

(もっと読む)

データ転送装置及びデータ転送システム

【課題】前後のデータの関係から同期ヘッダを正しい値に訂正する。

【解決手段】フレームが分割されたデータに第2の所定ビットの同期ヘッダを付加することによって生成されるブロックを転送するデータ転送装置であって、前記ブロックは、連続して順に転送される第1のブロック、第2のブロック及び第3のブロックを含み、前記データ転送装置は、前記第1のブロックに含まれる第1の同期ヘッダ、前記第2のブロックに含まれる第2の同期ヘッダ及び前記第3のブロックに含まれる第3の同期ヘッダを取得し、前記第2の同期ヘッダが正しい値でない場合、前記第2のブロックが前記第1のブロック及び前記第3のブロックと整合するように、前記第2の同期ヘッダを、前記第1の同期ヘッダと前記第3の同期ヘッダとに基づいて推測できるか否かの第1の判定をし、前記推測された値に前記第2の同期ヘッダを訂正する。

(もっと読む)

高速シリアル転送デバイス試験方法、プログラム及び装置

【課題】高速シリアル転送デバイスでの同期外れ等障害の検証に特化した試験パターンを作成して対象装置内で連続的に転送することで、同期外れ等を短時間に検証可能とする。

【解決手段】試験パターン作成部10は、高速シリアル転送デバイスが有する複数のシリアル転送チャネルの各々に、符号変換テーブルによる変換後データでビット0又は1の同値が連続転送されるように変換前データを並べた試験パターンを作成する。基本パターン設定部22は、高速シリアル転送デバイスにおけるバイト順序方式と符号変換のRD値を考慮したうえで基本パターンを設定する。基本パターン再設定部24は高速シリアル転送デバイスにおけるビット転送順序のチャネル使用方法に合わせて基本パターンを再設定する。基本パターン並替え部26は使用チャネル数やビット転送順序等のチャネル使用方法に合わせて各チャネルに基本パターンが転送されるように並び替える。

(もっと読む)

1 - 20 / 77

[ Back to top ]