Fターム[5K047MM35]の内容

デジタル伝送方式における同期 (12,489) | 装置、回路、機能 (2,875) | 基本回路、機能 (1,980) | 積分回路 (28)

Fターム[5K047MM35]に分類される特許

1 - 20 / 28

クロック再生回路及びクロックデータ再生回路

【課題】安定した再生クロック信号を高速に生成することができるクロック再生回路を提供することを課題とする。

【解決手段】クロック再生回路は、入力データに同期して第1のクロック信号をサンプリング及びホールドする第1のサンプルホールド回路(312)と、第1のクロック信号に対して周波数が同じで位相が90度異なる第2のクロック信号を入力し、入力データに同期して第2のクロック信号をサンプリング及びホールドする第2のサンプルホールド回路(313)と、第1のクロック信号及び第2のサンプルホールド回路の出力信号をミキシングする第1のミキサ回路(314)と、第2のクロック信号及び第1のサンプルホールド回路の出力信号をミキシングする第2のミキサ回路(315)と、第2のミキサ回路の出力信号から第1のミキサ回路の出力信号を減算することにより再生クロック信号を出力する減算器(316)とを有する。

(もっと読む)

同期回路、同期方法、および受信システム

【課題】受信機の個体差や伝送チャネルの時間変動に応じて最適なループゲインを探索できるようにするとともに、伝送フレーム内で複数の変調方式が用いられる場合でも最適なループゲインを探索することができるようにする。

【解決手段】ループゲイン制御部34から初期化フラグを受け取ったPLL制御誤差比較部33は、制御誤差値を算出し、比較器63において、この制御誤差値の大小比較を開始する。制御誤差比較結果に基づいてループフィルタ43−1およびループフィルタ43−2に供給するループゲインを制御する。伝送モード別ゲイン選択部71は、複数の内部のレジスタのうち、伝送モード番号TMに対応するループゲインレジスタG1main[TM]に保持させる値をゲイン制御シーケンサ72から入力される値によって更新する。

(もっと読む)

半導体装置

【課題】従来の半導体装置は、送信クロックの周波数が安定するまでに多くの時間を要する問題があった。

【解決手段】本発明の半導体装置は、送信クロックCLKから生成される受信クロックRCLKと入力信号RDと間の位相の進み又は遅れを示す位相差信号を生成し、受信クロックRCLKの位相を入力信号RDの位相に追従させる制御を行う位相追従ループと、受信クロックRCLKの周波数を入力信号RDの周波数に追従させる制御を行う周波数追従ループと、を有し、入力信号RDからデータ信号Sout及びデータ信号に対応する同期クロックSCLKの抽出を行うクロックアンドデータリカバリ回路13と、位相差信号に基づき生成される周波数差信号FPに応じて周波数調整信号Fadjにより示される値を増減させる周波数誤差調整器14と、周波数調整信号Fadjに基づき送信クロックCLKの周波数を増減させる発振器12と、を有する。

(もっと読む)

差動4位相偏移変調の位相補間ベースのクロック及びデータの回復

【課題】方法は、N個の入力ストリームを受け取る工程を含む。

【解決手段】N個の入力ストリームおける入力データ・ビットに基づいて、回復されたクロック信号を生成する工程であって、回復されたクロック信号はクロック周波数及び回復されたクロック位相を有する工程と、回復されたクロック位相に対する個別の位相オフセットにおける個別の位相及びクロック周波数を有する回復されたクロック信号に基づいてN個の入力ストリームのうちの一入力データ・ビットストリームに対するクロック信号を生成する工程と、N個のそれぞれのクロック信号と、N個の入力ビットストリームそれぞれとの間の位相差を検出する工程と、それぞれの位相差をなくすようN個のクロック信号の位相を調節する工程である。

(もっと読む)

クロックアンドデータリカバリ回路

【課題】ジッタトレランスの低下、引き込み時間の増大、引き込みが不能等の問題を解消するクロックアンドデータリカバリ回路を提供する。

【解決手段】多相の抽出クロック信号で入力データをサンプリングするデータサンプリング回路11からのサンプリングデータ信号群の比較結果に基づきクロック信号の位相を進める信号(UP1)又は位相を遅らせる信号(DOWN1)、エラー検出時エラー信号(ERR)を出力する位相検出器12と、UP1/DOWN1信号を積分する第1の積分器13と、第2の積分器14と、第1の積分器の出力値(PPM)に基づき所定のパターンを生成するパターン発生器15と、第2の積分器の出力とパターン発生器の出力を合成する混合器16と、入力クロックを入力し前記混合器の出力信号に基づき位相を可変させた前記多相の抽出クロックを生成する位相補間器17から構成される。

(もっと読む)

受信回路、受信方法、および、光受信器

【課題】送信されるデータ信号に外乱ノイズが混入しやすい環境にあっても、非同期方式により正しくデータを受信することができる受信回路を実現する。

【解決手段】非同期データ受信回路100は、受信信号をサンプリングして得られた信号値の和から受信信号の値を推定する積分量算出・傾き検出部10を備えている。そして、推定された受信信号の値が変化するデータ変化点を参照して、再生クロック生成部50にて再生クロックの立ち上がりタイミングを設定し、推定された受信信号の値を参照して、同期確認・データ再生部60にて再生データの値を設定する。

(もっと読む)

マルチレート用バーストモード受信機

【課題】 異なる送信ビットレートのONUが混在するPONシステムにおいて,OLTが,ONUに特別な機能を必要とせずに高速なバースト信号を受信するための,マルチレート用バーストモード受信機を実現することが課題である。

【解決手段】 本発明のマルチレート用バーストモード受信機では,平均振幅を検出することにより信号の入力を判定する信号入力判定部と,高周波成分の包絡線検波を行い信号のビットレートを判定するビットレート判定部の判定結果により,受信ビットレートに対応した光信号受信部及びシリアル/パラレル変換部の設定切替を行う。

(もっと読む)

無線受信装置

【課題】初期同期を精度よく取る。

【解決手段】検波ブロック2は、アンテナ1による受信信号の包絡線検波を行う。各積分ブロック31,32は、積分回路301,302によって検波信号を積分期間において積分する。信号処理部5では、2つのデジタル信号(積分値)の少なくとも一方が閾値以上となる範囲において、第1の積分ブロック31のデジタル信号が第2の積分ブロック32のデジタル信号より大きい場合、2つの積分期間のタイミングを検波信号のパルスのタイミングに対して進み方向に変化させ、第2の積分ブロック32のデジタル信号が第1の積分ブロック31のデジタル信号より大きい場合、2つの積分期間のタイミングを遅れ方向に変化させるように位相制御部7を制御する。閾値レベルは、2つのデジタル信号の少なくとも一方が閾値以上となる範囲で、第1,2の積分ブロック31,32の積分値の大小反転が1回となるように設定される。

(もっと読む)

無線受信装置

【課題】初期同期を取った後、同期を外すことなく安定にパルスを追尾する。

【解決手段】検波ブロック2は、アンテナ1による受信信号の包絡線検波を行う。各積分ブロック31,32は、積分回路301,302によって検波信号を積分期間において積分する。信号処理部5では、初期同期を取った後、通常状態では第1,2の積分ブロック31,32の2つの積分期間のタイミングを検波信号のパルスのタイミングに対して進む方向又は遅れる方向の何れかの方向に一定シフト量ずつシフトさせるように、位相制御部7を制御するとともに、2つのデジタル信号(積分値)の差分の極性が反転したか否かを判定する。2つのデジタル信号の差分の極性が反転したと判定した場合、2つの積分期間のタイミングを検波信号のパルスのタイミングに対して逆方向に一定シフト量より大きいシフト量だけシフトさせるように、位相制御部7を制御する。

(もっと読む)

BPSK復調回路、BPSK復調方法、非接触ICカードリーダライタ、非接触ICカードおよび通信システム

【課題】簡易な回路構成で、小型化、経済化および低消費電力化が可能なBPSK復調回路を提供する。

【解決手段】BPSK受信信号の先頭に挿入されたプリアンブル信号を整流してキャパシタCに順次充電した充電電位が、所定の閾値を超えたか否かの判定結果を同期状態信号としてシュミットトリガインバータSより出力し、該同期状態信号がロジック“1”の間は、AND1回路からプリアンブル信号をカウンタクリア信号として出力して、BPSK受信信号の16倍の周波数のクロックCLを分周する4ビットカウンタCNをクリアする動作を繰り返して、4ビットカウンタCNの16分周出力の反転出力の位相をプリアンブル信号に一致させる。充電電位が前記閾値を超えた時点以降BPSK受信信号がなくなるまで、該16分周出力の反転出力¬QDと8分周出力QCとの論理積をBPSK受信信号のデータをサンプリングするサンプリングタイミング信号として出力する。

(もっと読む)

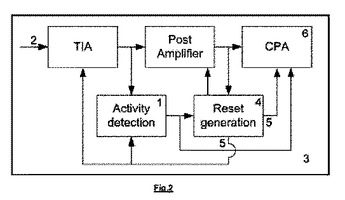

TDMAネットワークにおける信号検出のための装置及び方法

本発明は、バーストモード受信機における動作状態を検出するための回路(1)に関する。本回路は、プリアンブルを含む入力信号(2)を受けるように構成される。本回路は、入力信号(2)における信号遷移を検出する微分器(11)を備え、微分器(11)を動作させる情報をそのプリアンブルが含む。好ましい実施形態において、上記情報は時定数である。本回路は、微分器の出力が供給されるように構成された積分器(12)をさらに備える。結果として得られる信号は基準(16)に対して比較される。この基準と交差するとき、動作状態が検出される。ある実施形態ではフロントエンド回路が提供され、フロントエンド回路は、動作状態を検出する回路の後段に、フロントエンド回路をリセットするように構成されたリセット回路と、位相を復元するように構成されたクロック位相アラインメント回路を備える。  (もっと読む)

(もっと読む)

クロックアンドデータリカバリ回路

【課題】クロックアンドデータリカバリ回路において、周波数追従ループのジッタ耐性を安定させる。

【解決手段】位相検出器210は、位相補間器270からの同期クロックとシリアルデータの位相を比較して比較結果に応じた位相誤差信号を出力する。第1の積分器230は、位相誤差信号を積分してシリアルデータの位相変動に追従するための位相補正制御信号を得る。第2の積分器240は、位相補正制御信号をさらに積分してアップ/ダウン信号を得る。パターン発生器250は、アップ/ダウン信号からシリアルデータの周波数変動に追従するための周波数補正制御信号を生成する。パターン発生器250のパターン長と第2の積分器240のカウント幅の積は、第1の積分器230のカウント幅が大きいほど大きくなる大きさの閾値以上である。

(もっと読む)

CDR回路

【課題】再生データに含まれるジッタを簡易且つ正確にモニタ可能にする。

【解決手段】入力データDinを入力して第1再生クロックCLK1を出力する第1クロック再生部10と、前記入力データDinと前記第1再生クロックCLK1を入力して再生データDoutを出力するデータ再生部20と、前記再生データDoutを入力して第2再生クロックCLK2を出力する第2クロック再生部30と、前記第2再生クロックCLK2を入力してジッタ量を検出するジッタ検出部とを備える。ジッタ検出部は、ゲーティング回路40、積分回路50およびジッタ算出回路60からなる。

(もっと読む)

ビット同期回路

【課題】受信機と送信側の間にタイミング誤差が残るような状況で長いデータを受信する場合でも、正しいビット同期点を表す信号を発生し続けることができるビット同期回路を提供する。

【解決手段】FSK復調回路に用いるビット同期回路において、サンプリング・極性判定回路の出力とデータの変化点付近の信号との相関を計算する相関回路12と、該相関回路12の出力の絶対値を出力する絶対値回路13と、該絶対値回路13の出力を予め決められた数のデータ周期分だけデータ周期内の時間位置を合わせて積分する積分回路14と、該積分回路14の出力のピーク位置からビット同期点を求めるピーク判定回路15と、リセット時にビット同期信号を出力するビット同期カウンタ16とを有し、該ビット同期カウンタ16はサンプリングクロックをカウントし、ピーク判定回路15から出力するピーク判定信号によりリセットされる。

(もっと読む)

無線フレームの先頭位置検出方法及び装置

【課題】本発明は複数のシンボルで構成され各シンボル内の先頭に自シンボル内の終端の所定のサンプル数のデータを複写したガードインターバル(GI)を備え,先頭のシンボルの第1のGIが他のシンボルの第2のGIより長いOFDMの無線フレームの先頭位置を簡易な構成で短時間に検出することを目的とする。

【解決手段】入力フレームと入力フレームを所定長遅延させた信号を各位相毎に自己相関の演算をし,その出力を第1と第2のGIの各時間で積分をし,フレームの任意位置において,第1のGIを持つシンボルと第2のGIを持つシンボルの配置位置の1フレーム内に発生可能な配列の組合せに対応した個数の相関結果の加算を各積分値の出力に対して行って結果を記憶し,記憶した各相関結果からピーク値の位相とGI長を検出して,フレームの先頭位置を求めるよう構成する。

(もっと読む)

デジタル位相推定器、デジタル位相ロックループ及び光コヒーレント受信器

【課題】デジタル位相推定器、デジタル位相ロックループ、及び光コヒーレント受信器を提供する。

【解決手段】光コヒーレント受信器は、ローカル発信器光信号を供給するローカル発信器レーザと、受信光信号を前記ローカル発信器光信号とミックスする光90°周波数ミキサと、前記光90°周波数ミキサから出力された光信号をベースバンド電気信号に変換する第1と第2のバランス光電子検出器と、前記第1と第2のバランス光電子検出器からの出力信号をデジタル信号にそれぞれ変換する第1と第2のアナログ・デジタル変換器と、受信光信号のキャリア信号とローカル発信器光信号の間の位相差を補償して補償信号を出力するデジタル位相ロックループと、前記補償信号からデータを回復するデータ回復部とを有する。

(もっと読む)

シンボルタイミング検出装置及び無線端末装置

【課題】受信された変調信号のシンボルタイミングを検出して当該変調信号を復調する無線端末装置で、無線通信を行う無線周波数に周波数偏差が生じても、安定してシンボルタイミングを制御する。

【解決手段】サンプリング手段103がシンボル周期より短い周期で変調信号の信号値をサンプリングする。抽出手段117が複数のサンプリング点における信号値の中からシンボルタイミングの位置にあるとみなされる信号値を抽出し、復調手段107が抽出された信号値について復調を行う。サンプリング点復調手段110が各サンプリング点における信号値について復調を行い、値検出手段201が各サンプリング点における復調結果の電力値を検出し、シンボルタイミング制御手段113〜116が各サンプリング点における電力値に基づいて抽出手段117によりシンボルタイミングであるとみなすタイミングを制御する。

(もっと読む)

受信装置及び受信方法

【課題】 正信号と負信号との間の位相差を低減できるようにすると共に、位相差を自動かつ最適に調整できるようにする。

【解決手段】 差動信号の正信号と負信号との間に発生する差動ペア内スキューのDC電圧レベルSa3−2と当該DC電圧レベルSa3−2を判別するための閾値Sa3−3とを比較し、比較後、位相を遅延させる制御信号Sa4、及び遅延状態を表す制御信号Sp1に基づいて、正信号または負信号に対して所定の遅延量を設定する差動ペア内スキュー調整部8を備えるものである。

(もっと読む)

クロック同期方法およびクロック同期回路

【課題】 互いに非同期である送信側装置と受信側装置とのクロック同期をとるために、入力データ速度に対して数倍程度のクロック周波数があれば同期可能なクロック同期方法およびクロック同期回路を提供する。

【解決手段】 受信フレームが、クロックの同期のために利用される予め定められた信号を有する任意のビット数のクロック同期情報を備え、受信装置が、入力信号識別手段と、積分手段と、最適位相判定手段とを備え、受信装置が、受信フレームを受信したときに、入力信号識別手段が、前記受信フレームのクロック同期情報を識別し、積分手段が、前記入力信号識別手段の識別結果を位相毎に累積加算し、最適位相判定手段が、前記積分手段の累積加算結果を位相毎に比較することにより、クロック同期を得るために最適な位相を判定する。

(もっと読む)

無線受信装置及び無線受信方法

【課題】パルス同期が取れた後、パルス同期の維持の確実性を向上することができる無線受信装置、及び無線受信方法を提供する。

【解決手段】異なる積分期間について通信フレームの積分値AD1〜ADnを出力する複数の積分回路と、積分値AD1〜ADnを加算する加算器7と、加算値AD0を単位期間毎に積算した積算値がパルス消失検出用閾値に満たない場合パルスが消失したことを検出するパルス消失検出部82と、消失が検出されたタイミングから単位期間毎に加算値AD0を積算するパルス検出用積算部83と、当該積算値がパルス有無判定用閾値を超えるとパルス有区間であると判定し、当該パルス有無判定用閾値に満たないとパルス無区間であると判定するパルス有無判定部84と、パルス有区間であればパルスタイミングと積分期間とを同期させる同期部81とを備えた。

(もっと読む)

1 - 20 / 28

[ Back to top ]