Fターム[5K047MM36]の内容

デジタル伝送方式における同期 (12,489) | 装置、回路、機能 (2,875) | 基本回路、機能 (1,980) | 遅延回路、素子 (191)

Fターム[5K047MM36]に分類される特許

1 - 20 / 191

クロックデータ再生回路

クロックデータリカバリ回路およびそれを内蔵する送受信半導体集積回路

【課題】高いジッタ耐性を有して多相クロックの位相数と消費電力と半導体チップ面積との増大を軽減する。

【解決手段】クロックデータリカバリ回路1のエッジ検出器105の複数のエッジ検出回路105Mの各回路は、第1と第2のエッジ検出回路105M1、2を含む。第1の検出回路105M1は受信データ信号のデータエッジがエッジ検出位相から−1位相よりも進相なことを検出して第1出力信号を生成して、第2の検出回路105M2は受信データ信号のデータエッジがエッジ検出位相から+1位相よりも遅相なことを検出して第2出力信号を生成する。第1または第2の出力信号に応答して、エッジ検出位相が−1位相分または+1位相分変更される。受信データ信号のデータエッジの±1位相の範囲内の存在が検出された場合には、次回のエッジ検出位相は現在の状態に維持される。

(もっと読む)

時刻同期システムおよび時刻同期方法

【課題】時刻同期ネットワーク上でクライアント装置が独立した時刻同期ネットワークを構築する際に、クライアント装置間で高精度な時刻同期を確立する。

【解決手段】時刻同期が確立した時刻同期ネットワークの転送装置に接続された2つのクライアント装置間で、当該時刻同期ネットワークを介してPTPの時刻同期パケットを用いた時刻同期確立シーケンスに基づいて時刻同期をとる時刻同期システムにおいて、2つのクライアント装置にそれぞれ接続される転送装置のうち、クライアント装置に時刻同期パケットを出力する側の転送装置で、時刻同期ネットワークを介して転送される時刻同期パケットの双方向の遅延時間Δtを調整して等しくし、PTPの時刻同期確立シーケンスに基づく時刻同期処理を行う構成である。

(もっと読む)

シリアル通信回路

【課題】低消費電力モードから復帰時にその受信シンボルでスキュー調整を実施することができ、通常通信状態への迅速な復帰を行う。

【解決手段】符号化された複数のレーンのシリアル受信信号からクロックの再生を行い、受信シンボルを各レーン毎に再生し、バイトアライン及びSP変換後、復号化して複数のレーンの受信シンボルを同一のクロックに同期した受信シンボルに変換して出力する物理層受信回路と、複数のレーンの受信シンボルに対してレーン間のシンボルスキューを調整するレーン間スキュー調整回路とを備えたシリアル通信回路において、所定の検出基準シンボルを受信シンボルからレーン毎に検出し、カウンタ回路により検出信号に応答して検出信号の計数を開始し、カウンタ値の選択信号に対応する遅延量だけ、物理層受信回路から出力される複数のレーンの受信シンボルに対して遅延させてレーン間のシンボルスキューを調整する。

(もっと読む)

周波数・時刻同期方法および周波数・時刻同期装置

【課題】

従来、周波数同期と時刻同期とを実現する場合、装置のオーバヘッドが多くなるという課題があった。

【解決手段】

本発明では、パケットネットワークを介して接続される装置間で周波数同期と時刻同期とを行う周波数・時刻同期方法において、上位側の装置は、標準周波数に同期する周波数情報を含む信号上に標準時刻に同期する時刻情報を含む時刻同期パケットを重畳して伝送し、前記信号を受信する下位側の装置は、前記信号に含まれる前記周波数情報を抽出して自装置内の時刻のカウントアップに使用し、前記時刻同期パケットの前記時刻情報を用いて自装置の時刻を設定することを特徴とする。

(もっと読む)

通信システムおよび方法

【課題】通信マスタ装置と複数のノードとの間をライントポロジーで接続する通信システムにおいて、各ノードにおける同期信号の生成タイミングのずれを補正する。

【解決手段】通信システムは、通信マスタ装置と、通信マスタ装置から送出される通信フレームを受信する複数のノードとがライントポロジーで接続されている。通信マスタ装置は、ライントポロジー上で通信マスタ装置から遠方に位置する順に、各ノードに与えるべきデータが格納されるフィールドが配置された通信フレームを送出する。各ノードの信号処理LSIは、通信フレーム内で各ノードに割り当てられたフィールドのデータ到着時に同期信号を生成する同期信号生成回路12と、ライントポロジー上で下流側に隣接するノードとの間に生じる伝播遅延時間を計算する演算回路18と、伝播遅延時間に基づき、下流側に隣接するノードに送信する通信フレームを遅延させる遅延回路24と、を備える。

(もっと読む)

半導体装置、及び情報処理装置

【課題】

安定的な動作を確保できる半導体回路装置、及び情報処理装置を提供することを課題とする。

【解決手段】

半導体装置は、入力信号に遅延を与える遅延部と、前記遅延部から出力される出力信号の位相を検出する位相検出部と、前記位相検出部から出力される位相情報に基づき、前記出力信号の位相の安定動作範囲を設定する設定部と、前記安定動作範囲から位相が外れた前記出力信号の検出回数をカウントするカウンタと、前記遅延部の動作条件又は外的要因に応じて、前記カウンタのカウント数のディスカウント数を表すディスカウント信号を生成するディスカウント制御部と、前記カウンタのカウント数と前記ディスカウント信号が表すディスカウント数とに基づき、前記出力信号の位相のエラーの有無を判定するエラー判定部とを含む。

(もっと読む)

タイミング検出回路および通信機

【課題】フレームタイミングを精度良く合わせることにより安定的な通信を実現することができるタイミング検出回路22を提供する。

【解決手段】本発明のタイミング検出回路22は、異なる複数の遅延タイミングでプリアンブルの相関値を算出する相関器220と、OFDMシンボル毎の相関値の平均に基づいて閾値SigBを算出する第2の閾値算出部222と、同一の遅延タイミング毎に相関値を複数のOFDMシンボルに渡って平均してSigCを算出する相関平均算出部223と、SigBを超えるSigCの中で最大のSigCを特定し、その所定割合を閾値SigDとして算出する第1の閾値算出部224と、閾値SigDを超えるSigCの中で、最前のSigCのタイミングをOFDMシンボルタイミングとして特定するフレームタイミング出力部225とを備える。

(もっと読む)

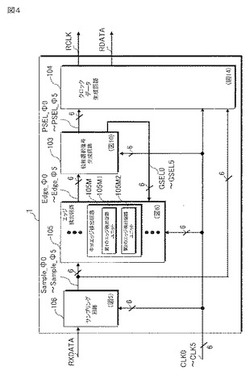

位相調整装置

【課題】デジタル画像データとクロックとの位相を調整する場合に、投影画像による目視判断などを行わないで自動的に調整する。

【解決手段】データセレクタ104は、遅延回路101から並列に供給される互いに所定時間遅延時間の異なる複数の遅延クロックのうち、セレクト端子に供給されるnビットカウンタ値に応じた1種類の遅延時間の遅延クロックを選択する。ラッチ回路105は、デジタルデータをデータセレクタ104から出力された遅延クロックの立ち上がり及び立ち下りでラッチする。4段シフトレジスタ106は、ラッチ回路105からのデジタルデータを、データセレクタ104から出力された遅延クロックをシフトクロックとして4段シフトする。コンパレータ107は、4段シフトレジスタ106の入力デジタルデータと出力デジタルデータとを比較し、比較結果が一致する場合は、ラッチが正しくできていると判断する。

(もっと読む)

光パケットスイッチ装置

【課題】伝送路の帯域利用効率を向上できる光パケットスイッチ装置を提供する。

【解決手段】光パケットスイッチ装置10は、光スイッチ制御部13と、光スイッチ部16とを備える。光スイッチ制御部13は、光電変換部と、CDR部と、シリアル/パラレル変換部と、分周部と、パラレルデータ信号の中からフレーム同期パターンを検出すると共に、パラレルデータ信号の先頭ビットに対して何ビットずれた位置にフレーム同期パターンが格納されているかを示す遅延ビット数を検出する同期パターン検出部と、ヘッダを解析して、光パケット信号の光パケット長および方路情報を検出するヘッダ解析部と、ヘッダ解析部で検出された光パケット長および方路情報と、同期パターン検出部で検出された遅延ビット数情報とに基づいて、競合する光パケット信号の通過/破棄を判定する出力競合判定部34とを備える。

(もっと読む)

デジタルクロックリカバリ回路及び半導体チップ

【課題】小型で、省電力で、かつパルスベースの超高速シリアル転送にも用いることのできるデジタルクロックリカバリ回路(CDR)を実現することを目的とする。

【解決手段】デジタルロックループ(DLL)、エッジ検出器、デジタルコンパレータ等を用いて、データ信号にDLLクロック信号をロックさせ、全ての回路要素をデジタル回路で構成し、クロックデータリカバリ(CDR)を実現する。

(もっと読む)

通信装置及びデータ処理方法及びプログラム

【課題】時刻同期目的の通信が行われている最中に時刻同期目的以外の通信が行われる場合でも正確に通信遅延時間を算出し、高精度の時刻同期を実現する。

【解決手段】同期スレーブ300が計測フレームの受信を完了してから計測応答フレームの送信を開始するまでの時間を同期スレーブ300において送信待ち時間として計測する。時刻同期と無関係の汎用フレームの送信により計測フレームの受信完了から計測応答フレームの送信までに時間がかかっても、同期マスタ200が計測フレームを送信してから計測応答フレームを受信するまでの往復時間から送信待ち時間を差し引くことにより正確な通信遅延時間を導出することができ、高精度の時刻同期を実現できる。

(もっと読む)

データ受信装置、データ送信装置、制御方法

【課題】 データ受信装置がデータ送信装置から受信するデータと、データ受信装置がデータ送信装置へ出力するクロックとの間で1サイクル以上の遅延がある場合、データ受信装置がデータ送信装置から供給されるデータを取りこぼしてしまう可能性がある。

【解決手段】 データ送信装置へコマンドを送信する際に、コマンドの送信終了タイミングと、送信装置からの前記コマンドに対応するデータの受信開始タイミングとの間のサイクル数をカウントする。

(もっと読む)

受信回路

【課題】受信信号にプリアンブルまたはユニークワードが含まれているかに係らず、かつ受信信号の符号化方式に依存せずに、データの先頭が検出できる受信回路を提供する。

【解決手段】受信回路100は、1シンボルの参照信号を受信信号に対してスライディングさせながら相関演算をすることによって、相関信号を生成する相関演算部11を備える。参照信号は、前半の1/2シンボル期間がハイレベルであり、後半の1/2シンボル期間がロウレベルである。受信回路100は、さらに、受信信号に対して、参照信号の1/2シンボル期間分だけ遅延させて、遅延信号を出力する遅延部17と、相関信号の先頭のピークのタイミングを遅延信号に含まれるデータの先頭のタイミングとして検出するデータ先頭タイミング検出部16とを備える。

(もっと読む)

オーバーサンプリング回路及びそれを用いたシリアル通信装置及びシリアル通信方法

【課題】主な目的は、消費電流を減少させることにあり、副次的な目的は、オーバーサンプリング間隔を切り替えることができるオーバーサンプリング回路及びそれを用いたシリアル通信装置及びシリアル通信方法を提供する。

【解決手段】シリアルデータを所定時間だけ遅延させた多相シリアルデータを生成する生成部と、その多相シリアルデータを多相クロックでオーバーサンプリングするオーバーサンプリング部と、を備えた。

(もっと読む)

シリアル通信装置及びその制御方法

【課題】内部回路との間で所定の同期クロックを用いて通信を行う送受信回路と、入力される基準クロックに基づいて上記同期クロックを発生するPLL回路とを備えたインターフェース回路を備えたシリアル通信装置において、インターフェース回路及び内部回路の誤動作を防止する

【解決手段】遅延回路5は、基準クロックREFCLKの周波数が100MHzで安定した後に発生されるリセット信号PERST#を、所定の遅延時間Δtだけ遅延させて内部リセット信号PERST2を発生し、リンクコントローラ31に出力する。PHY回路2は、リセット信号PERST#に応答してリセットされ、リンクコントローラ31は、内部リセット信号PERST2に応答してリセットされる。また、遅延時間Δtは、PLL回路23の回路仕様に基づいて予め計算されたロックアップ時間より長く設定される。

(もっと読む)

CDR回路、受信装置、および通信システム

【課題】簡易な回路構成で、高速かつジッタ入力に強く、信号エラーの発生を抑止することが可能なCDR回路、受信装置、および通信システムを提供する。

【解決手段】CDR回路310は、遅延素子312−1〜312−4を含み、定期的に信号遷移の挿入されたデータ入力をトリガとしてクロックを抽出する分周器320と、分周器で抽出されたクロックに同期して入力データ信号をラッチするラッチ315−1〜315−8とを有する。

(もっと読む)

光通信システムのためのスキュー検出装置、光通信システム

【課題】短時間でのスキュー量の検出を可能にした光通信システムのためのスキュー検出装置等を提供する。

【解決手段】送信信号を多重化して送信する送信装置において、DQPSK符号化された送信信号の代わりに、1周期パターン中の所定のデータ箇所が変化する周期パターンからなるパターン信号を多重化して送信させるために前記パターン信号を発生するパターン発生手段103と、前記送信装置からの受信信号を受信し逆多重化を行う受信装置において、受信し逆多重化された前記パターン信号の周期パターンにおいて変化が生じている場所を検出して送信装置および受信装置の少なとも一方の内部で発生するスキュー量を検出するスキュー検出手段110と、を備えた。

(もっと読む)

時刻同期システム及び時刻同期方法

【課題】無線基地局間の同期状態を安定に保つこと。

【解決手段】無線基地局間を同期させるための第1同期信号6を供給する制御装置4と、第1チャネル及び第2チャネルを有する伝送路3を介して制御装置4と接続されるGPS受信機1とを備える時刻同期システムにおいて、GPS受信機1は、GPSの基準信号を受信し、制御装置4への上り信号の第1チャネルに基準信号を多重し、上り信号を伝送路3を介して送信する。制御装置4は、GPS受信機1への下り信号の第2チャネルに遅延測定信号を多重し、下り信号を伝送路3を介して送信し、GPS受信機1からの上り信号から第1チャネル及び第2チャネルを分離し、第2チャネルの遅延測定信号に基づいて伝送路3の遅延時間を測定し、遅延時間をもとに第1チャネルの基準信号の位相を補正し、補正された基準信号に基づいて第1同期信号6を出力する。

(もっと読む)

データ受信回路

【課題】高速で高精度のデータ受信を可能にするデータ受信回路の提供を図る。

【解決手段】入力データDataを受け取って遅延した遅延データを出力する可変遅延回路2と、データ取り込みクロックCLK1に従って前記遅延データを取得するデータ取得用フリップフロップ31と、クロック信号CLKを受け取ってフラクショナルクロックを出力するフラクショナルPLL回路1と、前記フラクショナルクロックCLK2に従って前記遅延データの位相検出を行う位相検出用フリップフロップ32と、該位相検出用フリップフロップの出力信号および前記データ取得用フリップフロップの出力信号から前記可変遅延回路における遅延量を制御して位相調整を行う位相調整回路4と、を有する。

(もっと読む)

1 - 20 / 191

[ Back to top ]