Fターム[5K047MM38]の内容

デジタル伝送方式における同期 (12,489) | 装置、回路、機能 (2,875) | 基本回路、機能 (1,980) | サンプリング、サンプルホールド回路 (144)

Fターム[5K047MM38]に分類される特許

1 - 20 / 144

電子装置

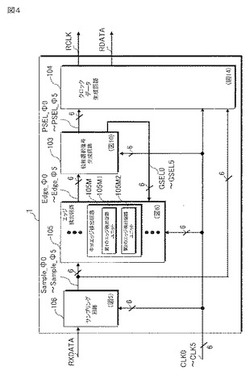

クロックデータリカバリ回路およびそれを内蔵する送受信半導体集積回路

【課題】高いジッタ耐性を有して多相クロックの位相数と消費電力と半導体チップ面積との増大を軽減する。

【解決手段】クロックデータリカバリ回路1のエッジ検出器105の複数のエッジ検出回路105Mの各回路は、第1と第2のエッジ検出回路105M1、2を含む。第1の検出回路105M1は受信データ信号のデータエッジがエッジ検出位相から−1位相よりも進相なことを検出して第1出力信号を生成して、第2の検出回路105M2は受信データ信号のデータエッジがエッジ検出位相から+1位相よりも遅相なことを検出して第2出力信号を生成する。第1または第2の出力信号に応答して、エッジ検出位相が−1位相分または+1位相分変更される。受信データ信号のデータエッジの±1位相の範囲内の存在が検出された場合には、次回のエッジ検出位相は現在の状態に維持される。

(もっと読む)

位相平均化に基づくクロック及びデータ回復の方法、回路及びシステム

【課題】入力データビットストリームとともに伝達される周波数ジッタ及びクロック信号発生器によって生成される周波ジッタを減衰させることができる、位相平均化に基づくクロック及びデータ回復の方法等を提供する。

【解決手段】一実施形態で、方法は、第1のクロック信号の第1の周波数を第1の周波数と基準クロック周波数の基準クロック周波数との間の周波数差に基づき調整するステップ(603)と、第1のクロック信号の第1の周波数及び第1の位相を第1のクロック信号と入力データビットストリームとの間の位相差及び第1の周波数と基準クロック周波数との間の周波数差に基づき更に調整して、第1のクロック信号の第1の周波数及び第1の位相を入力データビットストリームの入力データビット周波数及び入力データビット位相に略固定するステップ(606)とを有する。

(もっと読む)

CDR回路

【課題】誤ロック状態を検出し、この誤ロック状態から復帰することが可能なCDR回路を提供する。

【解決手段】CDR回路は、受信データ信号のデータをサンプルすべきデータサンプリングクロックとして第1のクロックと、受信データ信号のエッジをサンプルすべきエッジサンプリングクロックとして第2のクロックと、を生成し、且つ第1のクロックおよび第2のクロックの位相を調整するクロックリカバリ回路を備える。CDR回路は、第1のクロックで受信データ信号をサンプルした結果をデータサンプリング結果として出力し、第2のクロックで受信データ信号をサンプルした結果をエッジサンプリング結果として出力する位相検出回路を備える。CDR回路は、エッジサンプリング結果と、予め設定されたデータパターンとを比較し、エッジサンプリング結果とデータパターンとが一致した場合、誤ロック状態であると判断し、誤ロック状態検出信号を出力する結果比較回路と、を備える。

(もっと読む)

CDR回路及びCDR方法

【課題】ロック状態であるか否かを検出し、その検出結果を出力するCDR回路及びCDR方法を提供する。

【解決手段】受信データ信号をサンプリングするデータサンプリングクロック信号に同期して、受信データ信号をサンプリングしてサンプルドデータ信号を生成するデータサンプリング回路、データサンプリングクロック信号に対して位相がずれたエッジサンプリングクロック信号に同期して、受信データ信号をサンプリングしてサンプルドエッジ信号を生成するエッジサンプリング回路、データサンプリングクロック信号に同期して、受信データ信号の振幅と基準電圧との比較結果信号を出力する振幅比較回路を備え、比較結果信号、サンプルドデータ信号およびサンプルドエッジ信号に基づいて、データサンプリングクロック信号の位相を調整する位相シフタ回路、及び受信データ信号とデータサンプリングクロック信号との位相関係を検出するロック検出回路を備える。

(もっと読む)

受信回路及びエラー検出方法

【課題】設計時のタイミング調整を容易とする受信回路及びエラー検出方法を提供すること

【解決手段】本発明にかかる受信回路は、位相の異なる複数のクロックを用いて、矩形波としてデータが遷移する受信シリアルデータビット列をサンプリングして、前記サンプリングされた受信シリアルデータビットを用いて受信データビット列を生成するDL回路部1と、前記サンプリングされた前記受信シリアルデータビットのうち、所定期間内に位相の異なるクロックを用いてサンプリングされた前記受信シリアルデータビットの値が一致するか否かを比較した結果に基づいて前記受信データビット列のエラー区間を検出するPD回路部2と、を備えるものである。

(もっと読む)

適応型受信システム、適応型送受信システム及び複数チャネル送受信システム

【課題】ロックポイント付近におけるサンプリングクロックの位相の調整と、イコライザ部の制御とを安定させ、ジッタトレランスを高める。

【解決手段】位相比較部は、サンプリングタイミングとサンプリングタイミングよりも第一の所定位相分前のタイミングとの間の第一区間に、等化信号EQDATAのエッジが存在するか否かを示す位相比較信号LAG(n)を出力するとともに、サンプリングタイミングとサンプリングタイミングよりも第二の所定位相分後のタイミングとの間の第二区間に、等化信号EQDATAのエッジが存在するか否かを示す位相比較信号LEAD(n)を出力する。判定部は、検出データパターンの各ビットに対応する位相比較信号LAG(n),LEAD(n)の出力パターンを所定の比較対象パターンと比較し、合致するか否かに基づいて、等化信号EQDATAの1ビットがサンプリングクロックCKの1周期よりも長いか短いかを判定する。

(もっと読む)

受信装置、送信装置、受信方法、送信方法、通信システム

【課題】送信装置と受信装置が非同期のクロックを用いた音声データの通信において、音声データの内容等に応じて受信装置側で好ましい受信処理を行うことができるようにする。

【解決手段】受信装置では、受信した伝送信号について送信側の第1のクロックと非同期でかつ同一周波数の第2のクロックで音声データの復調を行って出力する非同期モード処理と、受信した伝送信号から得られる音声データについてリサンプリングを行い第2のクロックでサンプリングされた音声データを出力するリサンプリングモード処理とを、選択的に実行する。このモード選択は送信装置からの指示情報に基づいたり、受信した音声データの種別に応じたものとしたり、AGC処理に連動するものとする。

(もっと読む)

オーバーサンプリング回路及びそれを用いたシリアル通信装置及びシリアル通信方法

【課題】主な目的は、消費電流を減少させることにあり、副次的な目的は、オーバーサンプリング間隔を切り替えることができるオーバーサンプリング回路及びそれを用いたシリアル通信装置及びシリアル通信方法を提供する。

【解決手段】シリアルデータを所定時間だけ遅延させた多相シリアルデータを生成する生成部と、その多相シリアルデータを多相クロックでオーバーサンプリングするオーバーサンプリング部と、を備えた。

(もっと読む)

クロック再生回路及びクロックデータ再生回路

【課題】安定した再生クロック信号を高速に生成することができるクロック再生回路を提供することを課題とする。

【解決手段】クロック再生回路は、入力データに同期して第1のクロック信号をサンプリング及びホールドする第1のサンプルホールド回路(312)と、第1のクロック信号に対して周波数が同じで位相が90度異なる第2のクロック信号を入力し、入力データに同期して第2のクロック信号をサンプリング及びホールドする第2のサンプルホールド回路(313)と、第1のクロック信号及び第2のサンプルホールド回路の出力信号をミキシングする第1のミキサ回路(314)と、第2のクロック信号及び第1のサンプルホールド回路の出力信号をミキシングする第2のミキサ回路(315)と、第2のミキサ回路の出力信号から第1のミキサ回路の出力信号を減算することにより再生クロック信号を出力する減算器(316)とを有する。

(もっと読む)

位相同期回路および無線受信装置

【課題】サブサンプリングPLLの利点を保持したまま、フラクショナル分周を実現する。

【解決手段】電圧制御発振器は、制御電圧に応じて周波数が制御される第1信号、および前記第1信号と逆相の第2信号を生成する。サブサンプリング位相比較器は、基準信号の周期毎に、前記第1信号および第2信号の電圧を標本化して、第1標本化電圧および第2標本化電圧を生成する。電流生成回路は、供給電圧に応じて第1電流信号を生成する第1のチャージポンプと、供給電圧に応じて前記第1電流信号と反対符号の第2電流信号を生成する第2のチャージポンプとを有する。セレクト制御手段は、前記第1および第2標本化電圧を前記第2および第1チャージポンプにまたはこれと反対に供給する第1、第2供給モードを選択的に実行する。ループフィルタは、前記第1、第2の電流信号の合成電流信号を平滑化して、前記電圧制御発振器に与える前記制御電圧を生成する。

(もっと読む)

サンプリング位相を補正するホストコントローラ及び方法

【課題】 転送データの信頼性向上ならびにエラー対処性能の向上を実現する。

【解決手段】 一実施形態は、外部機器から受信した信号をサンプリングする際のサンプリングクロックの位相シフト補正を行うホストコントローラ10であって、前記サンプリングクロックの位相シフトが必要か判定し、位相シフトが必要な場合は、シフト方向に応じてカウンタ108をアップ/ダウンカウントする位相シフト判定部107と、前記位相シフトの変動範囲制限値を格納する制限値格納部109と、前記カウンタ値が前記位相シフトの制限値を超えているか判定し、超えている場合にエラーの通知を可能とし、超えていない場合に、前記カウンタ108のカウンタ値に応じて、前記サンプリングクロックの位相をシフトするシフト制限判定部110とを具備する。

(もっと読む)

送信装置、受信装置および送受信システム

【課題】回路規模の増大を抑制しつつEMIノイズの低減を図ることができる送信装置を提供する。

【解決手段】送信装置10Aは、送信データ生成部11および出力バッファ部12Aを備える。送信データ生成部11は、受信装置へ送出すべきデータdata1およびクロックclock1を生成し、これらを出力バッファ部12Aへ出力する。出力バッファ部12Aは、データ送信部13およびクロック送信部14Aを含む。クロック送信部14Aは、間欠的に位相シフトを与えられたクロックを生成して送出する。データ送信部13は、クロック送信部14Aにより送出されるクロックに同期してデータを送出する。

(もっと読む)

データ再生回路、局側光送受信装置及びデータ再生方法

【課題】高速かつ消費電力の低いバーストCDR回路を提供することを目的とする。

【解決手段】複数のクロックを生成する多位相クロック生成手段と、サンプリングデータを出力するサンプリング手段と、データの変化位相を検出する変化位相検出手段と、識別位相を決定する識別位相決定手段と、識別位相のクロックでサンプリングされたデータを選択し再生データを出力するデータ選択手段と、識別位相の変動が収束したかを判定し、収束した場合に収束通知信号を出力する収束判定手段と、その信号に基づいて変化位相検出手段の変化位相検出動作を予め定めた時間の間中止させる検出動作制御手段と、前記時間の間識別位相決定手段に収束位相を保持させる識別位相保持手段とを有し、変化位相検出動作を中止している時間の間は収束位相でサンプリングされたデータを選択して再生データを出力することを特徴とする。

(もっと読む)

ホストコントローラ、情報処理装置、およびサンプリング方法

【課題】 メモリカードからのデータを正しく得ることができ且つデータの転送効率を向上させることができるようにすること。

【解決手段】 実施形態によれば、ライトデータに対して返されるCRCステータスを対象に、位相が異なる複数のクロックに従ってサンプリングを行うことによって複数の値を取得する動作を繰り返す複数のデータ入力手段(25〜27)と、前記複数のデータ入力手段により取得された複数の値の中から、前記CRCステータスの値として正しく取得された値を識別し、データ転送が成功したか否かを示す判定結果を所定のデバイスに通知する制御手段(21)とを具備するホストコントローラが提供される。

(もっと読む)

クロックアンドデータリカバリ回路

【課題】ジッタトレランスの低下、引き込み時間の増大、引き込みが不能等の問題を解消するクロックアンドデータリカバリ回路を提供する。

【解決手段】多相の抽出クロック信号で入力データをサンプリングするデータサンプリング回路11からのサンプリングデータ信号群の比較結果に基づきクロック信号の位相を進める信号(UP1)又は位相を遅らせる信号(DOWN1)、エラー検出時エラー信号(ERR)を出力する位相検出器12と、UP1/DOWN1信号を積分する第1の積分器13と、第2の積分器14と、第1の積分器の出力値(PPM)に基づき所定のパターンを生成するパターン発生器15と、第2の積分器の出力とパターン発生器の出力を合成する混合器16と、入力クロックを入力し前記混合器の出力信号に基づき位相を可変させた前記多相の抽出クロックを生成する位相補間器17から構成される。

(もっと読む)

PCM信号復調回路、該復調回路に用いられるPCM信号復調方法及びPCM信号復調プログラム

【課題】入力PCM信号にノイズが含まれている場合でも、高精度で復調するPCM信号復調回路を提供する。

【解決手段】復調タイミング判定手段(タイミング制御部24、ローカルクロック25、PLL26、エンベロープ予測部27)は、ゼロクロス検出信号zbを入力すると共にピーク検出信号pbを入力して入力PCM信号ibの1周期分の位相及び振幅を含むデータptを生成し、エンベロープデータとして蓄積して基準位相標本情報及び基準周期情報を作成すると共に、基準位相標本情報及び基準周期情報に基づいて、入力PCM信号ibの後続の周期の位相及び振幅の予測情報efを作成し、予測情報efと後続の周期の位相及び振幅とを比較して誤差が所定の範囲内にあるとき、復調タイミング信号tcを出力する。復調部28により、復調タイミング信号tcに同期して復調データmdが出力される。

(もっと読む)

受信回路、受信方法、および、光受信器

【課題】送信されるデータ信号に外乱ノイズが混入しやすい環境にあっても、非同期方式により正しくデータを受信することができる受信回路を実現する。

【解決手段】非同期データ受信回路100は、受信信号をサンプリングして得られた信号値の和から受信信号の値を推定する積分量算出・傾き検出部10を備えている。そして、推定された受信信号の値が変化するデータ変化点を参照して、再生クロック生成部50にて再生クロックの立ち上がりタイミングを設定し、推定された受信信号の値を参照して、同期確認・データ再生部60にて再生データの値を設定する。

(もっと読む)

デジタルクロック再生器

サンプリング装置(110)は、変動する周期時間を有する入力クロック信号(CLKin)を受信し、入力クロック信号(CLKin)の平均周波数より実質的に高い周波数を有するサンプリングクロック信号(CLKsmpl)に基づいて、入力クロック信号(CLKin)をサンプリングする。サンプリング装置(110)は、入力クロック信号(CLKin)の各周期に対して、各周期長値(PL)を生成する。平均化装置(120)は、いくつかの周期長値(PL)をサンプリング装置(110)から受信し、それに基づき、前記数の周期長値(PL)に等しい周期数を含む平均化期間に渡って、入力クロック信号(CLKin)に対して平均周期時間を表す平均周期長値(PLavg)を生成する。出力装置(151)は、平均周期長値(PLavg)およびサンプリングクロック信号(CLKsmpl)に基づいて、安定した出力クロック信号(CLKout)を生成する。 (もっと読む)

受信装置及び通信システム

【課題】伝送路上のノイズによるメイン処理の実行効率低下が発生することなく、且つ、CPUなどに通信処理のための外部割込ポートを必要としない受信装置及び通信システムを提供する。

【解決手段】CPU11が第1サンプリング部21及び第2サンプリング部22を備え、第1サンプリング部21及び第2サンプリング部22が、プリアンブルの各ビットのビット幅と同じサンプリング周期で、且つ、ビット幅の1/2の時間ずらしたタイミングで、入力ポート11aに入力される2値信号のサンプリングを行う。第1サンプリング部21又は第2サンプリング部22の少なくとも一方でプリアンブルを検出した場合に、CPU11がデータの受信を開始することができる。リモコン3及びUHF受信IC12等は、プリアンブルに係る誤差が許容範囲内となるようにCPU11へ信号を送信する。

(もっと読む)

1 - 20 / 144

[ Back to top ]