Fターム[5L106AA01]の内容

半導体メモリの信頼性技術 (9,959) | メモリの種類 (1,971) | DRAM (638)

Fターム[5L106AA01]に分類される特許

1 - 20 / 638

半導体装置

【課題】半導体装置の動作テストのスループットを向上させる。

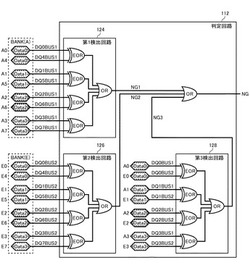

【解決手段】判定回路112は、2つのメモリバンクBANK(A)、BANK(E)から読み出される計16ビットのテストデータを検査する。検査対象となる16ビットのメモリセルMCにはすべて「H」の書き込みが実行されており、いずれのメモリセルMCに異常がなければそのまま「H」が読み出される。判定回路112は、メモリバンクBANK(A)のテストデータ同士を比較する第1検出回路124とメモリバンクBANK(E)のテストデータ同士を比較する第2検出回路126に加えて、更に、メモリバンクBANK(A)のテストデータとメモリバンクBANK(E)のテストデータを比較する第3検出回路128を備える。

(もっと読む)

半導体装置

【課題】複数の貫通電極を選択的に利用可能な積層型の半導体装置において、回路動作を安定させる。

【解決手段】半導体記憶装置10は、インターフェースチップIFと複数のコアチップCCを含む。コアチップCCは、インターフェースチップIFに積層される。インターフェースチップIFとコアチップCCは複数の貫通電極TSVにより接続される。コアチップCCに含まれる入力切り替え回路240、230は、電源投入時における設定処理の前に、コアチップCCに含まれる複数の入力信号線と複数の貫通電極TSVとの接続をいったん遮断し、コアチップCCの設定後に、複数の入力信号線と複数の貫通電極TSVの接続を示す救済情報にしたがって各入力信号線を複数の貫通電極TSVのいずれかと接続する。

(もっと読む)

半導体装置及びトリミング方法

【課題】ヒューズ素子の列数増に伴うトリミング時間の伸長を抑制する。

【解決手段】x方向に延伸する接地配線Gと、接地配線のy方向の一方側に設けられたヒューズ素子領域Aにx方向に沿って3列に並べて配置され、かつそれぞれの一端が接地配線Gに共通に接続される複数のヒューズ素子と、ヒューズ素子領域Aを挟んで接地配線Gの反対側に設けられ、ヒューズ素子領域Aに配置された複数のヒューズ素子それぞれの他端と接続される救済回路とを備え、上記複数のヒューズ素子は、それぞれ1つの欠陥選択線を示すアドレス情報を記憶する複数のヒューズ素子グループに所定個ずつグループ化され、同一のヒューズ素子グループに属する所定個のヒューズ素子は、同一列に配置されることを特徴とする

(もっと読む)

半導体装置及びこれを備える半導体システム並びにその動作方法

【課題】内部でデータ基準電圧を生成する半導体装置を提供すること。

【解決手段】本発明の半導体装置は、設定されたデータパターンを有する比較データを外部から印加されて設定された電圧レベル差を有してスイングさせることによって、その論理レベルを明確に区分して格納するデータ格納部と、テスト進入/脱出コマンドにより定義されるテスト動作区間の間に、外部から印加されるレベルテストコードに応答してその電圧レベルが決定されるデータ基準電圧のレベルに基づいて、設定された時間ごとに前記設定されたデータパターンを有する状態で外部から印加されるテストデータの論理レベルを決定し、論理レベルの決定された前記テストデータと前記比較データの論理レベルを比較してテスト結果信号を生成するテスト動作部と、前記テスト進入コマンドに応答してアクティブになり、前記テスト結果信号に応答して非アクティブになるテスト動作測定信号を生成するテスト動作測定信号生成部と、を備える。

(もっと読む)

半導体メモリ装置および半導体システム

【課題】PVT変動によってスキューが発生しても、不良に関する情報を適切に格納できるようにした半導体メモリ装置を提供する。

【解決手段】書き込み動作のために書き込みコマンドおよびデータを印加し、読み出し動作のために読み出しコマンドを印加し、前記読み出し動作によって出力データが入力されるテスト回路と、前記書き込みコマンドに応答して前記データをメモリセルに格納し、前記読み出しコマンドに応答して不良に関する情報を含む情報データを内部的に格納するが、前記情報データの格納は、前記情報データのレベルが遷移する場合に発生するパルスに同期して行われる。

(もっと読む)

集積回路,試験回路,試験装置,及び試験方法

【課題】記憶部と記憶部の試験を行なう試験部とを備える集積回路の回路規模の増大又は製造コストの増加を低減させる。

【解決手段】記憶部3と、供給される一組のアドレス及びデータを含む試験情報に基づいて前記記憶部3に対する書込及び読出試験を行なう試験部4と、を備え、前記試験部4は、前記試験情報に基づき前記記憶部3への書き込みが行なわれた場合に当該書き込みに用いられた第1書込アドレス及びデータを保持する第1保持部5と、前記試験情報に基づく第2書込アドレス及びデータによる前記記憶部3への書き込みと同時に前記記憶部3の第1読出アドレスから第1読出データを読み出す同時読出に用いる前記第1読出アドレスを、前記第1保持部5に保持された前記第1書込アドレスに基づいて生成する第1生成部6と、前記第1読出データの期待値を、前記第1保持部5に保持された前記第1書込データに基づいて生成する第2生成部7と、を備える。

(もっと読む)

半導体装置およびその制御方法

【課題】テストモード時にテストモードがリセットされるのを防ぐ。

【解決手段】本発明の半導体装置1は、外部から入力されるコマンドに応じて、半導体装置を通常動作モードまたはテストモードで動作させるテスト制御回路220と、通常動作モード時または前記テストモードにおける所定期間外に所定のコマンドが入力されると、テストモードリセット信号TRSTを活性化してテスト制御回路220に入力し、テストモードにおける所定期間内は、所定のコマンドが入力されても、テストモードリセット信号TRSTを活性化しないテストモードリセット制御回路210と、を有する。

(もっと読む)

試験装置および試験方法

【課題】アドレスを反転制御することができる。

【解決手段】被試験メモリのアドレスを発生するアドレス発生部と、アドレス発生部により発生されたアドレスをビット反転して被試験メモリに供給するか否かを選択する選択部と、アドレスをビット反転することを選択部が選択した場合にアドレス発生部により発生されたアドレスをビット反転して出力し、アドレスをビット反転しないことを選択部が選択した場合にアドレス発生部により発生されたアドレスをビット反転せずに出力する反転処理部と、反転処理部が出力した反転制御されたアドレス、および、反転処理部が出力したアドレスがビット反転したアドレスであるか否かを示す反転サイクル信号を、被試験メモリへと供給する供給部と、を備える試験装置を提供する。

(もっと読む)

半導体装置

【課題】CRC機能を有し、ライト動作とリード動作を高速に行うことができる半導体装置を提供する。

【解決手段】メモリセルアレイ(メモリセルアレイ11)と、巡回冗長論理符号を生成する誤り検出符号生成回路(誤り検出符号生成回路20)と、メモリセルアレイから読み出されたデータに巡回冗長論理符号を付加してデータ入出力端子を介して半導体装置の外部へリードデータとして出力し、或いは半導体装置の外部からライトデータが入力されて、前記メモリセルアレイへ書き込むデータを誤り検出符号生成回路に出力するデータ入出力部(データ入出力部19)と、メモリセルアレイとデータ入出力部との間に配置されるバス配線(リードライトバス)と、誤り検出符号生成回路とデータ入出力部との間に配置される巡回冗長論理符号配線(CRC信号線)と、を備える。

(もっと読む)

半導体装置

【課題】パリティエラーが発生した場合に適切な処理を実行する。

【解決手段】例えば、アクセスすべきメモリセルMCのアドレスを示すアドレス信号ADD及びアクセスの種別を示すコマンド信号CMDを外部から受け、これらに基づいてメモリセルアレイ11にアクセスするアクセス制御回路20を備える。アクセス制御回路20は、外部から供給される検証信号PRTYに基づいてアドレス信号ADD及びコマンド信号CMDを検証する検証回路90を含む。検証回路90は、アドレス信号ADD又はコマンド信号CMDがエラーであると判定した場合、メモリセルアレイ11へのアクセスを停止する。これにより、いわゆるパリティエラーなどの不良が検出された場合、誤ったコマンドの実行によってデータが破壊されたり、誤ったアドレスにデータを上書きしたりすることがない。

(もっと読む)

半導体装置

【課題】動作速度と駆動能力とのバランスが調整された多入力論理回路を備えた半導体装置を提供する。

【解決手段】3入力以上の入力端子を含み当該3入力以上の入力端子の論理レベルについて論理演算を行う多入力論理回路(XOR_H)を備え、当該多入力論理回路は、それぞれ2つの入力端子を含み当該2つの入力端子の論理レベルに対して前記論理演算を行う複数の2入力論理回路を含み、当該複数の2入力論理回路は、第1の2入力論理回路(XOR_D61)と当該第1の2入力論理回路よりも占有面積が小さく駆動能力が小さい第2の2入力論理回路(XOR_F61、XOR_F62)とを含み、前記第1の2入力論理回路が前記多入力論理回路の最終段として動作し、前記第2の2入力論理回路が前記第1の2入力論理回路に信号を供給する前段回路の少なくとも一部として動作することを特徴とする。

(もっと読む)

半導体装置及びそのテスト方法

【課題】ディスターブ試験時のノイズを低減しサイクル高速化を実現する技術を提供する。

【解決手段】本発明による半導体装置は、ワード線及びビット線に接続された複数のメモリセルを含み、複数のバンクに分割されたメモリセルアレイと、テスト動作時に、テスト回路用アドレス信号とディスターブ試験用テスト信号を用いて、バンク毎にワード線を内部アドレス信号に応じて別々のタイミングで選択するロウ周辺回路とを備える。

(もっと読む)

半導体装置

【課題】不良チップの救済効率を向上させ歩留まりを向上させる。

【解決手段】第1半導体チップのメモリセルアレイは、ノーマルセルアレイとスペアセルアレイとを備える。第1不良アドレスデータ出力回路は、メモリセルアレイ中の不良メモリセルのアドレスを示す第1不良アドレスデータを出力する。第1比較回路は、アドレスデータと第1不良アドレスデータとを比較して第1の一致信号を出力する。第2不良アドレスデータ出力回路は、メモリセルアレイ中の不良メモリセルのアドレスを示す第2の不良アドレスデータを出力する。第2比較回路は、アドレスデータと第2の不良アドレスとを比較して第2の一致信号を出力する。

(もっと読む)

半導体装置

【課題】チップサイズの増大を抑制でき、評価精度を落とすことなく、パラレルテストの時間の増大を抑制できる半導体装置を提供する。

【解決手段】複数のメモリアレイと、読み出し動作においては、メモリセルからの読み出しデータを増幅して外部へ出力するリードデータを生成し、書き込み動作においては、外部から供給されるライトデータに基づいてメモリセルへの書き込みデータを生成する、複数のメモリアレイに共通に設けられたリードライトアンプ(RWAMP)と、複数のメモリアレイ毎に設けられたスイッチと、複数のメモリアレイのうち活性化するメモリアレイのスイッチを順次導通させる第1の制御信号(LMIOSW)を生成する第1の制御回路(12b)と、リードライトアンプを活性化する第2の制御信号(DAE)を、活性化するメモリアレイの個数に基づいて発生する第2の制御回路(14)と、を備える。

(もっと読む)

半導体記憶装置

【課題】ライトマスクが可能で、CASアクセス時間が短く、かつCASサイクル時間が短縮されることで、データ転送効率を高めることが容易にできるECC機能付メモリを実現する。

【解決手段】センスアンプ20a,20bの後段にセンスアンプのデータと常に同一データとなるように制御されたページ長と同一ビット数の第1データラッチ30a,30bを配置し、CASアクセスの開始により第1データラッチ30a,30bから誤り検出・訂正回路40へのデータ転送をするとともに、誤り訂正とパリティ生成とをパイプライン処理することで、CASアクセス時間とCASサイクル時間とを短縮する。

(もっと読む)

半導体装置

【課題】誤ってテストモードにエントリされたとしても、正常に動作させる。

【解決手段】半導体装置は、内部回路をテストするテスト回路2に対してテストを開始させるテストモードエントリ信号が入力されたことに応じて、内部のラッチ10をセットすることにより、テスト回路2に対し、テスト回路2の駆動を許可するテストイネーブル信号をラッチ10から出力するテスト信号発生回路1を備える。テスト信号発生回路1が、ラッチ10がテストイネーブル信号を出力している場合、テストイネーブル信号を遅延させて、ラッチ10をリセットするリセット信号を生成するリセット信号生成回路30と、ラッチ10がテストイネーブル信号を出力している場合に、外部から供給されるトグル信号に基づいて、リセット信号生成回路30によるリセット信号を生成する動作を初期化する遅延初期化信号を出力する遅延初期化回路40と、を有している。

(もっと読む)

半導体装置、タイミング検出方法及びタイミング調整方法

【課題】半導体装置の設計値に対するタイミング検出、設計値に対するタイミング調整を最適に行う半導体装置、タイミング検出方法及びタイミング調整方法を提供する。

【解決手段】オシレータ回路1−3と、テスト信号の活性化期間内に前記オシレータ回路に対してクロッキング動作を行わせる前記テスト信号を前記オシレータ回路に出力するコマンド回路1−1と、前記オシレータ回路と接続され、前記クロッキング動作によるクロッキング数をカウントするカウンタ回路1−2と、を備える。

(もっと読む)

不揮発性半導体記憶装置

【課題】アクセス性能の向上を図ることが可能な不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置は、データバッファに格納されエラー訂正されたリードデータを第1の入出力ピンから出力するのに同期して、エラー訂正されたリードデータに対応する第1のパリティフラグを第2の入出力ピンから出力する。

(もっと読む)

半導体装置

【課題】テスト時間の短縮化を図ることが可能な半導体装置を提供する。

【解決手段】このチャージポンプ回路12では、通常動作時は、ポンプキャパシタC0,C2の一方電極にポンプクロック信号φPを与えるとともにポンプキャパシタC1,C3の一方電極にポンプクロック信号φPの相補信号を与え、ポンプキャパシタC0〜C3の欠陥を検出するテストモード時は、ポンプキャパシタC0〜C3の各々の電極間に外部電源電圧VCCを静的に印加する。したがって、MOSトランジスタのオン耐圧を超える高電圧をポンプキャパシタC0〜C3に印加できるので、テスト時間を短縮化できる。

(もっと読む)

高エネルギー粒子の衝突の影響を補正するメモリ素子

【課題】 高エネルギー粒子の衝突の影響を補正するメモリ素子を提供する。

【解決手段】 本発明は、少なくとも1個のメモリセル(CM)を含み、高エネルギー粒子の衝突の影響を自動的に補正するメモリ素子において、

−前記メモリセル(CM)に保存された値(Qd)の単一のコピーを一定期間保持する保持手段(MRET)と、

−前記メモリセル(CM)に保存された値(Qd)を前記保持手段(MRET)に保持された値と比較することにより、前記メモリセル(CM)の状態の変化を検知する検知手段(MDET)と、

−前記メモリセル(CM)の検知された状態変化が、高エネルギー粒子に起因するか否かを判定し、起因する場合は、前記保持手段(MRET)に保存された値を前記メモリセル(CM)に再ロードすることを自動的に命令するのに適した管理手段(MG)とを含むことを特徴とするメモリ素子に関する。

(もっと読む)

1 - 20 / 638

[ Back to top ]