Fターム[5M024AA58]の内容

Fターム[5M024AA58]に分類される特許

1 - 20 / 38

半導体メモリ装置およびその駆動方法

【課題】容量素子の容量を低減し、また、集積度の高い半導体メモリ装置を提供する。

【解決手段】1つのビット線BL_mに複数個のメモリブロックを接続させる。メモリブロックMB_n_mはサブビット線SBL_n_mと書き込みスイッチと複数のメモリセルを有する。サブビット線SBL_n_mと隣接するサブビット線SBL_n+1_mは2つのインバータと2つの選択スイッチよりなる増幅回路AMP_n/n+1_mに接続し、増幅回路は選択スイッチによりその回路構成を変更できる。また、増幅回路は読み出しスイッチを介してビット線BL_mに接続する。サブビット線SBL_n_mの容量は十分に小さいため、各メモリセルの容量素子の電荷による電位変動を増幅回路AMP_n/n+1_mでエラーなく増幅でき、ビット線BL_mに出力できる。

(もっと読む)

半導体メモリ装置およびその駆動方法

【課題】容量素子の容量を低減し、また、集積度の高い半導体メモリ装置を提供する。

【解決手段】1つのビット線BL_mに複数個のメモリブロックを接続させる。第n行のメモリブロックはサブビット線SBL_n_mと複数のメモリセルを有する。メモリセルはトランジスタと容量素子を直列に接続し、容量素子の電極の一をサブビット線SBL_n_mに接続する。さらに第n行のメモリブロックは書き込みトランジスタWTr_n_mと読み出しトランジスタRTr_n_mを有し、また、読み出しトランジスタRTr_n_mには相補型インバータ等の増幅回路AMP_n_mを接続する。サブビット線SBL_n_mの電位変動を増幅回路AMP_n_mで増幅する。サブビット線SBL_n_mの容量は十分に小さいため、各メモリセルの容量素子の電荷による電位変動を増幅回路AMP_n_mでエラーなく増幅でき、ビット線BL_mに出力できる。

(もっと読む)

半導体記憶装置

【課題】単位面積あたりのメモリモジュールの記憶容量を増加させる。また、消費電力の小さなメモリモジュールを提供する。

【解決手段】半導体装置は、ビット線と、二以上のワード線と、トランジスタおよびキャパシタからなるサブメモリセルを二以上有するメモリセルと、を有する。トランジスタのソースまたはドレインの一方がビット線と接続し、トランジスタのソースまたはドレインの他方がキャパシタと接続し、トランジスタのゲートがワード線の一と接続し、キャパシタの容量が各サブメモリセルで異なる。

(もっと読む)

記憶装置

【課題】記憶装置において、データの保持期間を確保しつつ、単位面積あたりの記憶容量を高める。

【解決手段】基板に設けられた駆動回路と、駆動回路上に設けられ、駆動回路によって駆動される複数のメモリセルアレイと、を有し、複数のメモリセルアレイはそれぞれ複数のメモリセルを有し、複数のメモリセルはそれぞれ、酸化物半導体層と重畳する第1のゲート電極と、を有する第1のトランジスタと、ソース電極又はドレイン電極と、第1のゲート絶縁層と、導電層と、を有する容量素子と、を有し、複数のメモリセルアレイは重ねて配置される。こうして、記憶装置において、データの保持期間を確保しつつ、単位面積あたりの記憶容量を高める。

(もっと読む)

半導体記憶装置およびその作製方法

【課題】電力の供給がない状況でもデータの保持が可能、かつ書き込み回数にも制限がない、新たな構造の半導体記憶装置を提供する。また、単位面積あたりの記憶容量を増加させる。

【解決手段】一対の電極と、一対の電極の側壁と接して設けられた絶縁膜と、該絶縁膜を介して一対の電極間に設けられ、一対の電極の上面の高さよりも上面の高さの低い第1のゲート電極と、第1のゲート電極上に設けられた第1のゲート絶縁膜と、第1のゲート絶縁膜および一対の電極と接して設けられた酸化物半導体膜と、少なくとも酸化物半導体膜上に設けられた第2のゲート絶縁膜と、第2のゲート絶縁膜を介して酸化物半導体膜上に設けられた第2のゲート電極と、を有する第1のトランジスタと、一対の電極の一方を介して第1のトランジスタと接続されるキャパシタと、を有し、該キャパシタに保持される電位に応じてデータが記憶されるメモリセルからなる半導体記憶装置である。

(もっと読む)

スイッチトランジスタを有しない差動センス増幅器

【課題】回路全体の面積を増やし、製造コストを押し上げるため、センス増幅器に使用される面積を最小限に抑える技術を提供する。

【解決手段】第1のビットライン(BL)に接続された出力と第2のビットライン(/BL)に接続された入力を有する第1のCMOSインバータと、第2のビットライン(/BL)に接続された出力と、第1のビットライン(BL)に接続された入力を有する第2のCMOSインバータと、第1のビットラインおよび第2のビットラインをそれぞれ第1のグローバルビットラインおよび第2のグローバルビットラインに接続するように配列された一対のパスゲートトランジスタを有し、それぞれのCMOSインバータはプルアップトランジスタM21、M22およびプルダウントランジスタM31、M32を備え、パスゲートトランジスタは、プルアップトランジスタ又はプルダウントランジスタによって構成される。

(もっと読む)

半導体メモリ装置

【課題】DRAMに必要なキャパシタの容量を低減し、高度に集積化したDRAMを提供する。

【解決手段】分割ビット線型DRAMにおいて、サブビット線をワード線の下に形成し、ビット線をワード線の上に形成する。分割ビット方式でサブビット線の寄生容量が低減し、かつ、セルトランジスタのオフ抵抗を必要に応じて高いものとすることによって、キャパシタの容量を通常のDRAMの1/10以下とすることができる。このため、スタック型キャパシタであっても、その高さを従来のものの1/10以下とできるので、その上にビット線を設けることも容易となる。また、セルトランジスタの構造を特殊なものとすることでメモリセルあたりの面積を4F2とできる。

(もっと読む)

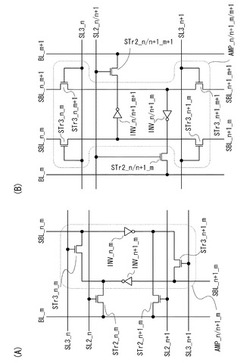

半導体メモリ装置およびその駆動方法

【課題】従来のDRAMでは容量素子の容量を減らすと、データの読み出しエラーが発生しやすくなる。

【解決手段】1つのビット線MBL_mに複数個のセルを接続させる。各セルはサブビット線SBL_n_mと4乃至64個のメモリセル(CL_n_m_1、等)を有する。さらに各セルは選択トランジスタSTr1_n_mとSTr2_n_mを有し、また、選択トランジスタSTr2_n_mには相補型インバータ等の増幅回路AMP_n_mを接続する。サブビット線SBL_n_mの寄生容量は十分に小さいため、各メモリセルの容量素子の電荷による電位変動を増幅回路AMP_n_mでエラーなく増幅でき、ビット線に出力できる。

(もっと読む)

半導体メモリ装置および半導体メモリ装置の駆動方法

【課題】消費電力の少ない新規の半導体メモリ装置を提供する

【解決手段】書き込みトランジスタWTr_n_mのソースと読み出しトランジスタRTr_n_mのゲートとキャパシタCS_n_mの一方の電極を接続し、書き込みトランジスタWTr_n_mのゲートとドレインを、それぞれ書き込みワード線WWL_nと書き込みビット線WBL_mに、キャパシタCS_n_mの他方の電極を読み出しワード線RWL_nに、読み出しトランジスタRTr_n_mのドレインを読み出しビット線RBL_mに接続した構造とする。ここで、読み出しビット線RBL_mの電位はフリップフロップ回路FF_mのような反転増幅回路に入力され、反転増幅回路によって反転された電位が書き込みビット線WBL_mに出力される構造とする。

(もっと読む)

半導体装置及びその内部回路の制御方法

【課題】従来の半導体装置は、チップ面積を抑制しながら内部電源電圧の変動を抑制することができなかった。

【解決手段】本発明の半導体装置は、電源電圧の電圧値を他の電圧値に変換して内部電源電圧を生成する第1の電源回路PWR0、第2の電源回路PWR1と、第1の配線MT02を介して第1の電源回路PWR0から内部電源電圧VDL0の供給を受ける第1の内部回路MA0と、第2の配線MT12を介して第2の電源回路PWR1から内部電源電圧VDL1の供給を受ける第2の内部回路MA1と、第1の配線MT02と第2の配線MT12とを互いに接続するブロック間配線MT3と、第1の内部回路MA0と第2の内部回路MA1が同時に動作する期間の長さを制御する制御回路CNT0、CNT1と、を有する。

(もっと読む)

縦型バイポーラインジェクタを有するDRAMメモリセル

【課題】フローティングボディDRAMセルにおいて表面積が縮小された改良型メモリセルを提供する。

【解決手段】ソースSと、ドレインDと、ソースSとドレインD間のフローティングボディFBとを有するFETトランジスタと、FETトランジスタのフローティングボディへの電荷の注入を制御可能なインジェクタであって、エミッタ15と、ベースと、FETトランジスタのフローティングボディFBによって形成されたコレクタとを有するバイポーラトランジスタからなるインジェクタとを備え、バイポーラトランジスタのエミッタ15が、FETトランジスタのソース22がバイポーラトランジスタのベースとして働くように配置される。複数のメモリセルを備えるメモリアレイ、及びこのようなメモリセルを制御する方法にも適用される。

(もっと読む)

第2のコントロールゲートを絶縁層の下に埋め込んだSeOIDRAMメモリセルをコントロールする方法

【課題】DRAMメモリセルでより小型のトランジスタを使用できる方法を提供する。

【解決手段】ゲート誘電体7によってチャネルから分離されているフロント・コントロール・ゲート8、およびベース基板に配置され、かつ絶縁層(BOX)によってチャネル4から分離されているバック・コントロール・ゲート9と、を有するトランジスタからなるDRAMメモリセルコントロール方法において、セルプログラミング動作において、フロント・コントロール・ゲートおよびバック・コントロール・ゲートが、第1の電圧をフロント・コントロール・ゲートに、第2の電圧をバック・コントロール・ゲートに印加することによって共に使用され、第1の電圧の大きさは、バック・コントロール・ゲートに電圧が印加されない場合にセルをプログラミングするのに必要な電圧の大きさよりも小さい。

(もっと読む)

半導体集積回路装置

【課題】雑音特性が優れ、かつサイズが小さいメモリアレイ及びそのメモリアレイを備えた半導体集積回路装置を提供する。

【解決手段】ビット線と定電圧との間に、順番に直列に接続された2つのトランジスタと1つの記憶蓄積素子とを備えたメモリセルは、2つのトランジスタのゲート電極に第1のワード線、第2のワード線がそれぞれ接続され、メモリアレイは、メモリセルがビット線と第1のワード線が交差する全ての交点に配置されたマットと、同一マット内のビット線対を入力とするセンスアンプと、第1及び第2のワード線を出力する第1及び第2のワードドライバと、を備える。

(もっと読む)

集積回路のためのオンチップ電圧変換装置およびシステム

【課題】 多数の電圧ドメインを有する集積回路デバイスおよびシステムのための改良された電圧変換システムを提供する。

【解決手段】 集積回路のためのオンチップ電圧変換装置は、第1のキャパシタと、この第1のキャパシタの第1の電極を第1の電圧ドメインの低側電圧レールに選択的に結合するように構成された第1のNFETデバイスと、第1のキャパシタの第1の電極を第1の電圧ドメインの高側電圧レールに選択的に結合するように構成された第1のPFETデバイスと、第1のキャパシタの第2の電極を第2の電圧ドメインの低側電圧レールに選択的に結合するように構成された第2のNFETデバイスであって、第2の電圧ドメインの低側電圧レールが第1の電圧ドメインの高側電圧レールに対応する、第2のNFETデバイスと、第1のキャパシタの第2の電極を第2の電圧ドメインの高側電圧レールに選択的に結合するように構成された第2のPFETデバイスと、を含む。

(もっと読む)

半導体メモリ

【課題】 無駄なデータ出力バッファが配置されることを防止し、半導体メモリのチップサイズを削減する。

【解決手段】 半導体メモリは、第1パッドと、第1パッドに隣接して配置される第2パッドと、第1パッドに接続される第1出力バッファと、第2パッドに接続される第2出力バッファとを有している。第1パッドと第2パッドとはメタルで接続される。これにより、読み出しデータを第1および第2出力バッファを用いて第1パッドに出力できる。したがって、読み出しデータを1つの出力バッファを用いて第1パッドに出力するときに比べて、第1および第2出力バッファの駆動能力を小さくできる。この結果、第1および第2出力バッファのサイズを従来に比べて小さくでき、半導体メモリのチップサイズを削減できる。

(もっと読む)

半導体記憶装置

【課題】メモリセルの情報を読み出すときのセンス動作マージンを向上させる。

【解決手段】半導体記憶装置50には、PMOSセンス回路1、NMOSセンス回路2、プリチャージ回路3、ダミーセル回路4、カラム選択回路5、切り離し回路6、メモリセルアレイMCA1、メモリセルアレイMCA2、及びNch MOSトランジスタNT1乃至6が設けられる。ビット線BL及び/BLにPMOSセンス回路1が接続され、ローカルビット線LBL及び/LBLにNMOSセンス回路2、プリチャージ回路3、ダミーセル回路4、及びカラム選択回路5が接続される。切り離し回路6は、PMOSセンス回路1とNMOSセンス回路2の間に設けられ、Nch MOSトランジスタNT1及びNT2を有し、制御信号Φtに基づいて、ビット線BLとローカルビット線LBLの間、及びビット線/BLとローカルビット線/LBLの間の接続或いは分離を行う。

(もっと読む)

半導体記憶装置及び半導体記憶装置の動作方法

【課題】本発明は、半導体記憶装置内の単位セルがキャパシタとフローティングボディーの全てにデータに対応する電荷とホールを格納することができるようにすることにより、リフレッシュ性能を向上させることができる半導体記憶装置及びその動作方法を提供する。

【解決方法】本発明の一実施形態に係る半導体記憶装置は、ボディーがフローティングされたトランジスタと電荷を格納するためのキャパシタで構成された単位セル、単位セルを活性化するためのワードライン、及び単位セルにデータを伝達するビットラインを含む。

(もっと読む)

半導体記憶装置

【課題】オーバードライブ方式を低電圧且つ小面積で成立させることが可能となる半導体記憶装置を提供する。

【解決手段】複数のメモリセルMCと、PMOS及びNMOSトランジスタからなり、メモリセルMCから読み出された情報を増幅するための複数のセンスアンプ121と、センスアンプ121のPMOSトランジスタのソース端子に接続されたPCS電源線とオーバードライブ電圧を供給するためのVOD電源線との間に設けられたトランジスタ17と、VOD電源線に接続されたVOD電源容量22と、VOD電源線と外部電源であるVDDSA電源線との間に接続された抵抗21とを備えている。

(もっと読む)

電源電圧発生回路

【課題】チップ面積をより小さくする。

【解決手段】容量素子のチャージポンピングによって昇圧電圧を発生して出力する昇圧部20と、外部電源の電圧が容量素子の耐圧を超える場合に、容量素子の耐圧範囲内の電圧に外部電源の電圧を降圧して昇圧部20の電源に与える電源降圧部10と、昇圧部20の電源に外部電源を直接与えるか電源降圧部10を介して与えるかを切り替えるスイッチ素子SW1と、を備える。昇圧部20は、多段の昇圧回路から構成され、多段の昇圧回路のそれぞれに含まれるMOSトランジスタで構成される容量素子のゲート酸化膜の厚さが同一であり、昇圧部20の出力を電源とする回路に含まれるMOSトランジスタのゲート酸化膜より薄い。

(もっと読む)

半導体記憶装置

【課題】メモリセルとしてFin型FETを採用し、かつ、メモリセルアレイのサイズが小さい半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、第1の方向に延在する複数のFin型半導体と、Fin型半導体内に設けられたソース層Sおよびドレイン層Dと、ソース層とドレイン層との間のFin型半導体内に設けられ、電気的に浮遊状態であり、データを格納するために多数キャリアを蓄積あるいは放出するボディBと、隣接する2つのFin型半導体の間にある第1の溝内に設けられた第1のゲート電極G1と、第1の溝に隣接し、隣接するFin型半導体の間にある第2の溝に設けられた第2のゲート電極G2と、ドレイン層に接続され、第1の方向に延在するビット線BLと、第1のゲート電極に接続され、第1の方向に対して直交する第2の方向に延在するワード線WLと、ソース層に接続され、第2の方向に延在するソース線SLとを備えている。

(もっと読む)

1 - 20 / 38

[ Back to top ]