Fターム[5M024AA91]の内容

Fターム[5M024AA91]の下位に属するFターム

Fターム[5M024AA91]に分類される特許

1 - 20 / 38

記憶装置

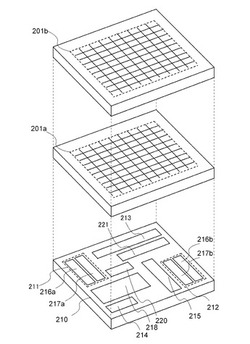

【課題】記憶装置において、データの保持期間を確保しつつ、単位面積あたりの記憶容量を高める。

【解決手段】基板に設けられた駆動回路と、駆動回路上に設けられ、駆動回路によって駆動される複数のメモリセルアレイと、を有し、複数のメモリセルアレイはそれぞれ複数のメモリセルを有し、複数のメモリセルはそれぞれ、酸化物半導体層と重畳する第1のゲート電極と、を有する第1のトランジスタと、ソース電極又はドレイン電極と、第1のゲート絶縁層と、導電層と、を有する容量素子と、を有し、複数のメモリセルアレイは重ねて配置される。こうして、記憶装置において、データの保持期間を確保しつつ、単位面積あたりの記憶容量を高める。

(もっと読む)

半導体メモリ装置およびその検査方法

【課題】オフ抵抗が極めて高いトランジスタをスイッチング素子として有するメモリセルを構成するに際し、信頼性を高める検査方法および構成を提供する。

【解決手段】メモリセルのトランジスタのしきい値Vthが許容される範囲内にあるか否かを判定することにより、データ保持特性が十分でないメモリセルを排除する。そのためにトランジスタのゲートの電位を適切な電位VGMに保持し、また、トランジスタのドレインの電位をVGM以上の電位にする。この状態でメモリセルに書き込むことにより、トランジスタのソースの電位はしきい値Vthを含む式、(VGM−Vth)で表現される。この電位と他の参照電位との大小を比較することによりしきい値Vthが許容される範囲内にあるか否かを判定できる。

(もっと読む)

半導体メモリ装置およびその検査方法

【課題】オフ状態での抵抗が極めて高いトランジスタをスイッチング素子としてメモリセルを構成すれば、例えば、10年以上もの長期にわたりデータを保持できる。その一方で、例えば、トランジスタの特性等により1年しかデータを保持できないメモリセルも同時に作製される。そのようなメモリセルは早期に不良メモリセルとして排除する手段が必要とされるが、従来の検査では判別する手段がなかった。

【解決手段】メモリセルのトランジスタのゲートの電位を通常の保持に使用する電位VGLとそのトランジスタのしきい値Vthの間の所定の電位VGMに保持する。この状態で所定の時間保持すれば、電位VGLで10年保持したものと同様の状態となるので、この時点でデータの保持が不十分なメモリセルは、通常の使用でもデータを10年間保持できないと判断できる。

(もっと読む)

半導体装置及び半導体モジュール

【課題】DDP構造の半導体モジュールにおいて、上下のメモリのいずれにおいても、基板との間の信号経路を、DQ信号とDQS信号とで等長にすること。

【解決手段】本発明の半導体装置は、×N動作から×M(M=N/2)動作への切替を指示する信号が入力される入力端子と、偶数番目のDQピンまたは奇数番目のDQピンを指示する切替信号が入力される入力端子と、DQSピンからDQS信号が供給されると、供給されたDQS信号にしたがって、対応するDQピンを介してDQ信号を入出力するN個のDQ制御回路と、×M動作時に、偶数番目のDQピンが指示された場合、偶数番目のDQピンに対応するDQ制御回路にDQS信号を供給する第1のDQS制御回路と、×M動作時に、奇数番目のDQピンが指示された場合、奇数番目のDQピンに対応するDQ制御回路にDQS信号を供給する第2のDQS制御回路と、を有する。

(もっと読む)

半導体記憶装置及びそのテスト方法

【課題】シングルエンド型の複数のセンスアンプ回路を流れる電流を測定し、そのしきい値電圧のばらつきを容易に判別可能な半導体記憶装置とそのテスト方法を提供する。

【解決手段】本発明の半導体記憶装置は、選択されたメモリセルMCから読み出された信号を伝送する第1のビット線LBLと、第1のビット線LBLの信号電圧を増幅して出力電流に変換する増幅素子Q1を含むシングルエンド型の第1のセンスアンプ回路21と、第1のセンスアンプ回路を流れる電流(独立の接地電位VSSLを経由する電流)を、他の回路部分を流れる電流とは独立に測定するテスト動作を制御する制御回路とを備えている。

(もっと読む)

半導体記憶装置及び半導体記憶装置のテスト方法

【課題】複数のデータ入出力端子の内、一部のデータ入出力端子しかメモリテスタと接続しない場合においても十分なテストができるような半導体記憶装置およびそのテスト方法を提供する。

【解決手段】データ入出力端子(DQ0〜DQ31)と、メモリセルアレイ122と、通常の書き込み動作時にデータ入出力端子から取り込んだデータを一時的にラッチし遅れてメモリセルアレイに書き込めるようにしたデータラッチ回路111と、を備え、データラッチ回路が、読み出し動作時にデータ入出力端子へ読み出したデータをラッチし、書き込み動作時にデータ入出力端子のデータを新たにラッチせずにすでにラッチされているデータをメモリセルアレイに書き込むテストモードを備える。

(もっと読む)

半導体記憶装置

【課題】センスアンプ回路のオフ電流により不良を生じさせず、本来検出すべきメモリアレイ内のショート不良を検出することを可能とする。

【解決手段】センスアンプ回路30−1〜30−4は、ワード線131及びビット線132−1〜132−8の駆動により選択されるメモリセル136−1〜136−4の電位に基づいて生じるビット線対間の電位を増幅する。選択トランジスタ13−1〜13−8は、ビット線とセンスアンプ回路30−1〜30−4との間に設けられる。Xタイミング生成回路部に備えられるワード−SE間隔制御回路は、ワード線の駆動からセンスアンプ回路の活性化までの間を拡大してビット線の不良箇所を検出するテストが行われる際、拡大する時間に応じた間、テスト状態であることを示す信号に基づいて選択トランジスタ13−1〜13−8をオフ状態とし、ビット線132−1〜132−8とセンスアンプ回路30−1〜30−4とを切り離す。

(もっと読む)

ワード線不良をテストする方法

【課題】パッケージ段階のBIテストを実施する前に、ウェハー段階においてメモリーデバイスのワード線不良をテストする方法を提供し、不良WL修理を可能にする。

【解決手段】メモリーデバイスのワード線不良をテストする方法を提供するものであって、メモリーデバイスは、メモリーデバイスがワード線およびビット線に接続されるトランジスターを有するメモリーセルを備えるものであり、前記方法が:ワード線ドライバーにより前記ワード線を先決定電圧レベルまで駆動して前記メモリーセルの前記トランジスターをオンまたはオフとすること;および前記ワード線ドライバーの駆動能力を低減することを含むものである。

(もっと読む)

同期型半導体記憶装置およびそのテスト方法

【課題】テスト時に観測ピン数を減らすと共に出力データのデータレートを落として出力することが可能な同期型半導体記憶装置を提供する。

【解決手段】入出力回路部に複数のデータ端子に出力されるデータの一致を検出する一致検出回路250を設ける。テスト時にはラッチ146、148に同じ結果が書込まれ、クロック信号に応じて交互に読み出される。したがって、通常時にダブルデータレートでデータを出力する端子からテスト結果をデータレートを落として出力することができる。性能の低いテスタでも観測が可能であり、テストコストが削減できる。

(もっと読む)

半導体記憶装置

【課題】通常のCMOSプロセスにおいてDRAMを作製でき、低い製造コストで製造可能なDRAMの混載した半導体記憶装置を提供する。

【解決手段】半導体基板上に形成された第1及び第2のトランジスタT1、T2と、セルデータ電荷を保持するための2つのノードSNt、SNcと、周囲に形成されたシールド電極により構成される1ビットのメモリセル11領域であって、各々のノードSNt、SNcは第1、第2のトランジスタT1、T2のドレインに接続されており、第1及び第2のトランジスタT1、T2のゲートはともに同一のワード線WL0に接続されており、第1及び第2のトランジスタT1、T2のソースは第1、第2のビット線BLt0、BLc0に接続され、第1及び第2のビット線BLt0、BLc0は、同一のセンスアンプSA12に接続され、1ビットのメモリセル領域が2次元的にアレイ状に形成される。

(もっと読む)

半導体記憶装置及びそのテスト方法

【課題】 冗長セルに置換後の期待値比較方式のパラレルテストを可能とする半導体記憶装置の提供。

【解決手段】複数の冗長アドレスに対応して配設される冗長回路(BCRED)が、アクセスアドレスが冗長セルに置換されたものであるか判定する判定回路(102、103、105)と、前記領域が冗長セットが使用されていることを示す信号CFENと、該冗長選択信号CTRATYがともに活性化されている場合に、活性化した出力信号を出力する回路(104)を備え、冗長エリアのテストのときは、論理回路(11)の出力を、テスト結果のマスク信号として出力し、ノーマルエリアのテストのときは、論理回路(12)の出力を、テスト結果のマスク信号として出力するセレクタ14を備え、メモリアレイのテスト時、冗長アドレスにアクセス時にはテスト結果を強制的にパスとする。

(もっと読む)

インタフェース回路及びメモリ制御装置

【課題】ループバックテスト時に、実スピード動作における遅延故障検出のテストを実現するメモリ制御装置の提供。

【解決手段】出力側回路に、ノーマルモード位相シフト量制御回路23とテストモード位相シフト量制御回路25と、これら2つの位相シフト量制御回路の出力を選択するセレクタ27と、可変遅延回路6を備え、入力回路側にノーマルモード位相シフト量制御回路24とテストモード位相シフト量制御回路26と、これら2つの位相シフト量制御回路の出力を選択するセレクタ28と、可変遅延回路15を備え、ループバックしてリードデータ取り込み回路19でラッチされたリードデータ21とライトデータ20との期待値照合を行う比較回路22と、入力データのサンプリングタイミングが1エッジ分遅れた場合の期待値照合を行う第2の比較回路100を備えている。

(もっと読む)

オシレータ回路及び半導体記憶装置

【課題】本発明は、閾値電圧Vthのばらつきによる容量特性のばらつきに影響されることなく、所定の周期の発振信号を生成可能なオシレータ回路を提供することを目的とする。

【解決手段】オシレータ回路は、容量と、容量の一端に電気的に結合可能な第1の定電流源と、容量の該一端に電気的に結合可能な第2の定電流源と、容量の該一端と第1及び第2の基準電位とに結合され、容量の該一端の電位と第1及び第2の基準電位との比較結果に応じて、第1の定電流源を容量の該一端に電気的に結合して容量を充電する第1の動作と第2の定電流源を容量の該一端に電気的に結合して容量を放電する第2の動作とを切り換える制御回路と、第1の動作と第2の動作との切り換えタイミングに応じてパルス信号を生成する回路を含む。

(もっと読む)

基準電圧発生回路

【課題】絶対値が小さくても高い温度依存性を有する基準電圧を発生させることができる基準電圧発生回路を提供する。

【解決手段】電流経路P1は、入力端子14A側から見て、ダイオード11、及び抵抗12(抵抗R1)を直列接続して形成され、第2の電流経路P2は、入力端子14A側からダイオード13、抵抗14(抵抗R2)及び抵抗15(抵抗R3)を直列接続して形成される。オペアンプ20の反転入力端子には、ダイオード11のカソードと抵抗12との間の接続点の電圧V1が与えられ、非反転入力端子には、抵抗14と抵抗15との接続点の電圧V2が与えられる。

(もっと読む)

半導体記憶装置

【課題】 半導体記憶装置において、メモリセルのビット線間ショートはその抵抗値が大きいことから検出しにくい、また検出するためのテスト時間が長いという問題がある。

【解決手段】 シェアード型センスアンプを採用した半導体記憶装置において、テストモードにエントリし、シェアード型センスアンプに用いられるトランスファゲート、プリチャージ回路、センスアンプを個別に制御する。注目するビット線をハイインピーダンス状態とする。対向するセンスアンプは活性化のままとすることで隣接するビット線はロウインピーダンスとする。ビット線間ショートがあれば、隣接するロウインピーダンスのビット線からハイインピーダンス状態の注目ビット線のデータを反転させる。この反転データを読み出すことでビット線間ショートが検出できる。

(もっと読む)

半導体装置、半導体記憶装置、制御信号生成方法、及び救済方法

【課題】

ヒューズの切断不良による誤動作を防止するとともに、テストの作業時間を短縮し、チップ面積を削減すること。

【解決手段】

本発明にかかる半導体記憶装置は、複数のメモリセルが配列されたメモリセルアレイ30と、メモリセルアレイ30に生じた不良メモリセルを救済する冗長メモリセルと、冗長メモリセルに対応して設けられた電気ヒューズ10a,10bと、不良メモリセルを示すデータ信号に応じて電気ヒューズ10a,10bを選択するセレクタ11と、選択された電気ヒューズ10a,10bに電流を流して切断する切断回路21と、電気ヒューズ10a,10bの切断状態に基づいて切替信号を生成する切替信号生成回路22と、切替信号に応じて不良メモリセルを冗長メモリセルに切り替える切替回路2と、を有するものである。

(もっと読む)

テスト回路及びテスト方法

【課題】

従来のスキャンパスによるメモリテストでは、書き込み設定から読み出し設定までの時間がDRAMの記録保持時間を越える場合、正確なテストが行えなかった。

【解決手段】

テスト対象メモリに対し値を設定するスキャンフリップフロップに対し、書き込み値を設定し、その後の一連のシフト動作を介して、読み出し値の設定が完了するまでの間の、スキャンパスのシフト動作中に、テスト対象メモリに対し値を設定するフリップフロップを通過してゆく値に対して、リフレッシュ動作を行わせる値を含ませる。

(もっと読む)

半導体メモリ

【課題】 ビット線への電圧印加パターンを最適化し、バーンイン試験時間を短縮する。

【解決手段】 ビット線が互いに交差するツイスト構造を有するビット線対と、ビット線が互いに平行な非ツイスト構造を有するビット線対とを交互に配置して構成された半導体メモリに、電圧印加時間が互いに等しい第1〜第6ステップのバーンイン試験を実施する。全てのビット線間に印加されるストレスの印加時間を全て等しくできるため、ビット線へのストレスの印加時間のばらつきはない。したがって、メモリセルの特性が、バーンイン試験により過度に劣化することを防止できる。また、第1〜第6ステップにおいて、ストレスが印加されないビット線の数を最小限にできる。したがって、ストレスが印加されるビット線の比率を高くでき、バーンイン時間を短縮できる。この結果、試験コストを削減できる。

(もっと読む)

半導体記憶装置のテスト装置およびテスト方法

【課題】 ウェハテストにおけるバーンインを含むテストの時間を短縮する。

【解決手段】 ウェハテスト時において、バーンイン実施前に、テスタ用のプロ-バに接触するテスト対象デバイス単位でバーンイン回数を決定するテストを行なう(ステップSP4)。この回数決定テストにおいて決定されたバーンイン回数のバーンインを実施し、その後、テスト対象デバイス単位で機能テストを行なって、バーンイン不良率をモニタする(ステップSP5,SP6)。

(もっと読む)

半導体装置及びテスト方法

【課題】

評価・解析において、特性の劣化、不良等が周波数同期回路に因るのか否か等、不良原因の特定を容易化する半導体装置の提供。

【解決手段】

外部クロック端子13、14から外部クロック信号を入力して前記外部クロック信号に同期した信号を生成するDLL回路10と、外部端子15から入力されたクロック信号と、DLL回路10からの出力信号とを入力し、テストモード信号に基づき、テスト時には、外部端子15から入力されたクロック信号を出力し、通常動作時には、DLL回路10からの出力信号を出力するセレクタ11を備える。

(もっと読む)

1 - 20 / 38

[ Back to top ]