Fターム[5M024KK35]の内容

DRAM (26,723) | 特定の機能を有するメモリ、特殊なメモリ (655) | DRAM以外のものとの組合せ (290) | 論理回路とDRAM (202)

Fターム[5M024KK35]に分類される特許

1 - 20 / 202

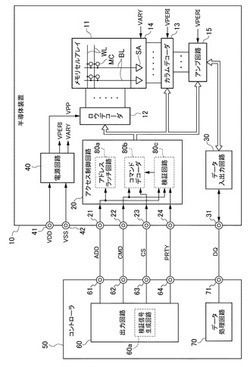

半導体装置

【課題】パリティエラーが発生した場合に適切な処理を実行する。

【解決手段】例えば、アクセスすべきメモリセルMCのアドレスを示すアドレス信号ADD及びアクセスの種別を示すコマンド信号CMDを外部から受け、これらに基づいてメモリセルアレイ11にアクセスするアクセス制御回路20を備える。アクセス制御回路20は、外部から供給される検証信号PRTYに基づいてアドレス信号ADD及びコマンド信号CMDを検証する検証回路90を含む。検証回路90は、アドレス信号ADD又はコマンド信号CMDがエラーであると判定した場合、メモリセルアレイ11へのアクセスを停止する。これにより、いわゆるパリティエラーなどの不良が検出された場合、誤ったコマンドの実行によってデータが破壊されたり、誤ったアドレスにデータを上書きしたりすることがない。

(もっと読む)

半導体装置およびそれを利用した情報処理システム

【課題】半導体装置において、温度変化によるデータのラッチタイミングの調整によって生ずるシステムのビジー期間を抑制しなければならない。

【解決手段】タイミング制御回路116は、任意の温度でデータDQiとストローブ信号がキャリブレーションによってマッチングされたストローブ信号DQS,DQSBを受信し、内部ストローブ信号IDQS、IDQSBを生成し、ラッチ回路118に出力する。ラッチ回路118は、内部ストローブ信号IDQS、IDQSBのエッジのタイミングでデータDQiをラッチする。タイミング制御回路116は、温度検知回路124と内部ストローブ信号IDQS、IDQSBの伝送経路に間挿され、温度検知回路124からの温度信号Tにしたがって、前記マッチングを維持するように内部ストローブ信号IDQS、IDQSBの時間変動を抑制する可変遅延回路122を含む。

(もっと読む)

半導体装置

【課題】データ処理性能の低下を防止可能な半導体装置を提供すること。

【解決手段】本発明にかかる半導体装置は、インターフェイス回路105−1,105−2と、インターフェイス回路105−1に第1のデータバスを介して結合されると共に、インターフェイス回路105−1から出力される第1のアクセス制御信号に結合されたメモリコア106−1と、インターフェイス回路105−2に第2のデータバスを介して結合されたメモリコア106−2と、第1のアクセス制御信号、又は、インターフェイス回路105−2から出力される第2のアクセス制御信号を選択的にメモリコア106−2に結合させる選択回路107−1と、を備える。

(もっと読む)

記憶回路、信号処理回路、電子機器

【課題】新たな構成の不揮発性の記憶回路を用いた信号処理回路を提供する。

【解決手段】酸化物半導体を用いて形成されたトランジスタと、該トランジスタのソース電極またはドレイン電極の一方と接続された容量素子を用いて、不揮発性の記憶回路を構成する。記憶回路に予めハイレベル電位を書き込んでおき、退避させるデータがハイレベル電位の場合は、そのままの状態を維持し、退避させるデータがローレベル電位の場合は、ローレベル電位を記憶回路に書き込むことで、書き込み速度を向上させた信号処理回路を実現できる。

(もっと読む)

信号処理回路

【課題】新たな構成の不揮発性の記憶回路を用いた信号処理回路を提供する。

【解決手段】演算部と、メモリと、演算部及びメモリを制御する制御部と、を有し、制御部は、揮発性の記憶回路と揮発性の記憶回路に保持されたデータを記憶するための第1の不揮発性の記憶回路との組を複数有し、メモリは、第2の不揮発性の記憶回路を複数有し、第1の不揮発性の記憶回路及び第2の不揮発性の記憶回路は、チャネルが酸化物半導体層に形成されるトランジスタと、トランジスタがオフ状態となることによってフローティングとなるノードに一対の電極のうちの一方が電気的に接続された容量素子とを有する。

(もっと読む)

コンピュータシステム及び揮発性メモリ装置

【課題】DRAMなどの揮発性メモリ装置に係わり、リフレッシュ時に必要な消費電力の低減を実現できる技術を提供する。

【解決手段】本コンピュータシステム1は、DRAM2とCPU4を含んで成り、例えばCPU4側にデータ反転制御回路100を備える。データ反転制御回路100は、DRAM2への書き込み時(a)のデータにおける所定幅の書込データ単位ごとに、値“1”の数が過半数かどうかを判定し、過半数である場合は、値“1”/“0”を反転処理する。またデータ反転制御回路100は、DRAM2からの読み出し時(b)のデータにおける所定幅の読出データ単位ごとに、上記反転状態の値“1”/“0”を反転処理して復元し、読み出しデータとする。上記構成により、DRAM2におけるリフレッシュ動作の対象となる値“1”が記憶されるメモリセルの数を少なくする。

(もっと読む)

ロジックプロセスで埋め込まれたDRAMのためのワード線ドライバ

【課題】慣用のロジックプロセスによる埋込みDRAMセルのデータ保持性能を改善できるワード線ドライバを提供する。

【解決手段】慣用のロジックプロセスによるpチャネルトランジスタ101を含むDRAMセルにアクセスするためのワード線ドライバを提供する。このワード線ドライバは、p型基板の中の深いn型ウェル領域の中に配置したp型ウェル領域に設けたnチャネルトランジスタ313を含む。負極性のブースト電圧供給源から前記p型ウェルおよび前記nチャネルトランジスタのソースに負極性ブースト電圧を供給する。この負極性ブースト電圧は、pチャネルアクセストランジスタのスレッショルド電圧以上の電圧値だけ接地電位よりも低い。深いn型ウェルおよびp型基板は接地電位点に接続する。

(もっと読む)

メモリインタフェース回路

【課題】データストローブ信号に発生するグリッジを有効に除去し、正確なデータ転送を可能にするメモリインタフェース回路を提供する。

【解決手段】システムクロック信号CLKに同期したマスク制御信号RENをある遅延調整値αだけ遅延させた信号を用いてデータラッチに使用するようにデータストローブ信号DQSをマスクする第1のマスク回路103と、遅延調整値αに一定の余裕度tを持たせてマスク制御信号RENを遅延させた信号を用いてデータストローブ信号DQSをマスクする第2のマスク回路104と、第1のマスク回路103の出力におけるエッジ回数のカウント値と第2のマスク回路104の出力におけるエッジ回数のカウント値とを比較して、両カウント値の一致を確認しつつ遅延調整値αを変更し、不一致が起こった場合には遅延調整値αを戻すように動作する比較回路1112とを設ける。

(もっと読む)

メモリ制御装置および画像形成装置

【課題】セルフリフレッシュモード時の消費電流量を低減させる。

【解決手段】データを格納する複数のメモリ2,3と、メモリ2,3を制御する各信号を入出力するメモリコントローラ1と、各信号を接続/切断可能なスイッチ20と、を備え、メモリコントローラ1は、セルフリフレッシュモードへの移行時に、スイッチを切り替えて複数のメモリ2,3を、セルフリフレッシュモード時に電源供給されるメモリ2と、セルフリフレッシュモード時に電源遮断されるメモリ3と、に分け、電源遮断されるメモリ3上における保持が必要なデータを電源供給するメモリ2上に格納する。

(もっと読む)

半導体記憶装置

【課題】CMOSプロセスで、ダイナミック型半導体記憶装置を形成し、ロジックとの混載に適したダイナミック型半導体記憶装置を実現する。

【解決手段】メモリセル(MC)のワード線(WL)を形成する導電線(3)とメモリセルセルプレート電極(CP)を形成する導電線(5)とを、異なる配線層に形成する。対をなすビット線に並行してメモリセルを接続し、2つのメモリセルで1ビットのデータを記憶する。

(もっと読む)

半導体システム、半導体メモリ装置及びこれを用いたデータ出力方法

【課題】データ入出力マージンを向上させ、低い電力消耗量でデータを安定的に出力できる半導体システム、半導体メモリ装置及びこれを用いたデータ出力方法を提供する。

【解決手段】半導体システム100は、クロック信号、データ出力命令語、アドレス信号及び第2ストローブ信号をメモリ装置へ伝送するコントローラ110及びコントローラ110から伝送されるクロック信号、データ出力命令語、アドレス信号及び第2ストローブ信号に応答して、第2ストローブ信号に同期されたデータをコントローラへ提供するメモリ装置120を含む。

(もっと読む)

半導体装置

【課題】積層型の半導体装置においてインターフェースチップからコアチップへのクロック信号の供給を不要とする。

【解決手段】外部から供給されるコマンド信号CMD及びクロック信号CKを受けて、各々がクロック信号CKに同期し、且つ、互いにタイミングが異なる複数のリード制御信号R1,R2を出力するリードタイミング制御回路100を有するインターフェースチップIFと、インターフェースチップIFに積層され、コマンド信号CMDが示す動作をリード制御信号R1,R2に同期してそれぞれ実行する複数の内部回路を有するコアチップCC0〜CC7とを備える。本発明によれば、コアチップに内でのレイテンシ制御が不要となることから、コアチップにクロック信号を供給する必要がなくなる。

(もっと読む)

半導体メモリ装置

【課題】半導体メモリ装置を提供する。

【解決手段】少なくともターミナルの第1対を含むパッケージインターフェースと、半導体チップのスタックと、それぞれ半導体メモリチップに備えられ、すぐに隣接した半導体チップの貫通電極と電気的に連結される貫通電極の複数のスタックと、第1情報を提供するディファレンシャル信号を受信するターミナルの第1対と連結される入力、及び貫通電極の複数のスタックのうち少なくとも一つに、第1情報を含む出力信号をシングルエンド信号のフォーマットで提供する出力を含むインターフェース回路と、を備える半導体パッケージである。

(もっと読む)

複合メモリ

【課題】 製造コストの上昇を招くことなくNANDフラッシュメモリにDRAMを混載することができ、且つチップ面積の増大を招くことなくシステム性能の向上をはかる。

【解決手段】 半導体基板10上に、NANDセルユニットからなる第1のメモリセルアレイとDRAMセルからなる第2のメモリセルアレイとを搭載した複合メモリであって、NANDセルユニットは、第1のゲート14と第2のゲート16を積層した2層ゲート構成の不揮発性メモリセル100と不揮発性メモリセル100の第1及び第2のゲート14,16間を接続した選択トランジスタ200で構成され、DRAMセルは、選択トランジスタ200と同じ構成のセルトランジスタ300と、不揮発性メモリセル100又は選択トランジスタ200と同じ構成のMOSキャパシタ400で構成されている。

(もっと読む)

フラッシュROMエミュレータおよびデータ制御方法

【課題】DDR2−SDRAM等のDRAMを使用した場合のリフレッシュ期間中であってもDRAMのリードを実施できるフラッシュROMエミュレータ等を提供すること。

【解決手段】フラッシュROMエミュレータは、ミラーリングされている複数のDDR2−SDRAM等のDRAMを備え、プロセッサおよび外部装置からのリード要求に対して複数のDRAMのうちリフレッシュをしていないものからデータを読み出す。

(もっと読む)

半導体装置

【課題】リフレッシュ動作のモード変更を柔軟に行う。

【解決手段】外部から供給されるリフレッシュコマンドREFに応答してリフレッシュ実行信号IREFを生成するリフレッシュ制御回路12と、リフレッシュ実行信号IREFの活性化に応答してカウント動作を行うリフレッシュアドレスカウンタ16とを備える。リフレッシュ制御回路12は、リフレッシュコマンドREFが1回入力されるごとにリフレッシュ実行信号IREFを2n回(nは0以上k以下の整数)生成する。nの値はリフレッシュコマンドREFに同期して外部から供給されるリフレッシュモード指定信号RMに基づいて可変である。これにより、1回のリフレッシュコマンドREFに応答したリフレッシュ実行信号IREFの生成回数が動的に変更可能であることから、コントローラ側からみて柔軟な制御が可能となる。

(もっと読む)

揮発性メモリのために独立したバンクリフレッシュを提供する方法及びシステム

【課題】リフレッシュ動作によるシステム性能の低下を

防止する。

【解決手段】各バンクが多くの行を有する多くのバンクを有する揮発性メモリと、目標バンクアドレスを揮発性メモリに提供するように構成され、前記揮発性メモリに対して自動リフレッシュモードで動作するよう指示するメモリコントローラとを含み、前記揮発性メモリは、前記目標バンクアドレスによって識別される目標バンクについて自動リフレッシュ動作を自動リフレッシュモードで実行するように構成され、自動リフレッシュ動作が目標バンクについて実行されている間、目標バンク以外の複数のバンクにおける残りのバンクは、メモリアクセスのために利用可能に制御される。

(もっと読む)

半導体デバイス

【課題】チップの入出力構成が異なる場合でも、高い順応性を有し、異なる仕様を構成可能な半導体デバイスを提供する。

【解決手段】内部回路と、内部回路とデバイスの外部とでデータ、アドレス、コマンドまたは電圧の入力、出力または入出力を行う複数の入出力端子31と、複数の入出力端子31の各経路を内部回路の各々が接続された複数の内部経路に選択的に接続させるセレクタ50と、セレクタ50を制御して、データ、アドレス、コマンドまたは電圧と端子との対応関係を変更する経路制御回路(経路選択信号発生回路70)と、を有する。

(もっと読む)

半導体装置

【課題】本願発明の課題は、電源電圧が低電圧化されるに従いセンス時間が著しく遅くなる、低電圧でのセンス時間が高温で高速になり、さらにプロセスばらつきに対してセンス時間が大きく変化してしまうこと等に対応したDRAMメモリセル用のセンス回路を提供することにある。

【解決手段】本発明の代表的な解決手段は、以下の通りである。メモリセルの接続されるビット線BLとローカルビット線LBLの間にスイッチ手段を設け分離結合できるようにし、BLをVDL/2プリチャージとし、LBLをVDLプリチャージとする。VDLはビット線BLの最大振幅電圧である。SAにはBLに結合されたゲート受けの差動MOS対を含む第1回路とLBLに結合されフル振幅増幅及びデータ保持のための第2回路を含むようにする。BLとLBLをキャパシタを介して容量結合させた際にはSAはLBLに接続したラッチ形SAを用いると良い。

(もっと読む)

メモリモジュールとコントローラ

【課題】フラッシュメモリのアクセス時間とSDRAMのアクセス時間との整合を図り、大容量フラッシュメモリを含むメモリモジュールとコントローラを提供する。

【解決手段】フラッシュメモリと、SDRAMと、フラッシュメモリ及びSDRAMの夫々のアクセスを制御し、外部からのストア命令に従って、SDRAMに記憶されるデータをフラッシュメモリに転送するための制御回路とそれに結合された複数の入出力端子を含む。制御回路は、ストア命令に従ってSDRAMに記憶されるデータをフラッシュメモリに転送している間に、SDRAMからのデータ読出し命令が入力された場合において、そのデータ転送を中断し、読み出し命令に従ってSDRAMに記憶されるデータを外部に出力するよう制御する。

(もっと読む)

1 - 20 / 202

[ Back to top ]