Fターム[5M024KK37]の内容

DRAM (26,723) | 特定の機能を有するメモリ、特殊なメモリ (655) | DRAM以外のものとの組合せ (290) | マイコン中のDRAM (18)

Fターム[5M024KK37]に分類される特許

1 - 18 / 18

記憶装置及び半導体装置

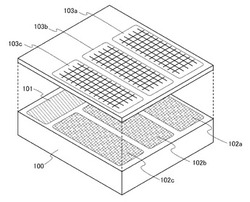

【課題】データの保持期間を確保しつつ、単位面積あたりの記憶容量を高めることができる記憶装置を提供する。

【解決手段】複数のビット線を幾つかのグループに分割し、複数のワード線も幾つかのグループに分割する。そして、一のグループに属するビット線に接続されたメモリセルには、一のグループに属するワード線が接続されるようにする。さらに、複数のビット線は、複数のビット線駆動回路102a,102b,102cによってグループごとにその駆動が制御されるようにする。加えて、複数のビット線駆動回路102a,102b,102cと、ワード線駆動回路101とを含めた駆動回路上に、セルアレイ103a,103b,103cを形成する。駆動回路とセルアレイ103a,103b,103cが重なるように三次元化することで、ビット線駆動回路が複数設けられていても、記憶装置の占有面積を小さくすることができる。

(もっと読む)

信号処理回路

【課題】新たな構成の不揮発性の記憶回路を用いた信号処理回路を提供する。

【解決手段】演算部と、メモリと、演算部及びメモリを制御する制御部と、を有し、制御部は、揮発性の記憶回路と揮発性の記憶回路に保持されたデータを記憶するための第1の不揮発性の記憶回路との組を複数有し、メモリは、第2の不揮発性の記憶回路を複数有し、第1の不揮発性の記憶回路及び第2の不揮発性の記憶回路は、チャネルが酸化物半導体層に形成されるトランジスタと、トランジスタがオフ状態となることによってフローティングとなるノードに一対の電極のうちの一方が電気的に接続された容量素子とを有する。

(もっと読む)

電子機器

【課題】リフレッシュに基づくDRAMのパフォーマンス低下を防ぐ技術を提供する。

【解決手段】電子機器100は、メモリー制御回路130は、DRAM140を構成する記憶素子について、所定期間Ts内に少なくとも1回はリフレッシュがなされるように、所定間隔でDRAM140に対してリフレッシュコマンドを発行する第1の分散リフレッシュ処理と、DRAM140への所定のリクエストがされることを契機として、当該所定間隔よりも短い間隔で集中的にリフレッシュコマンドを所定回数Nc発行する集中リフレッシュ処理と、所定回数Ncのリフレッシュコマンドを発行し終えると、所定期間Ts内において未だにリフレッシュされていない残りの記憶素子についてリフレッシュするためのリフレッシュ間隔Trを算出し、算出した当該リフレッシュ間隔Trでリフレッシュコマンドを発行する第2の分散リフレッシュ処理と、を行う。

(もっと読む)

半導体記憶装置

【課題】リフレッシュ制御信号を与える必要がなく、SRAMと同様なアクセスが可能な、DRAMコアを内蔵するシステムLSIを提供する。

【解決手段】セルフリフレッシュタイマは常に動作状態とされリフレッシュ要求信号FAYを定期的に活性化する。行選択系回路/コマンド発生系回路16は、リフレッシュ要求信号FAYと外部からのリードコマンドまたはライトコマンドとが競合したときには、たとえばリードやライト動作が終了してからリフレッシュ動作が行なわれるようにロウ系制御信号を制御する。サブメモリアレイSMAは従来と比べて細分化され、リフレッシュサイクルは短時間で終了するので、リードサイクル時間内でリードとリフレッシュとを終了させることができ、SRAMと同様な簡単な制御で使用できるDRAMコアを実現することができる。

(もっと読む)

遅延制御回路

【課題】複数の単位遅延素子から構成される可変遅延回路を用いてストローブ信号を遅延させるものであって、チップ毎の単位遅延時間のばらつきによらず、全単位遅延素子の動作テストを短時間で行うことができる遅延制御回路の提供。

【解決手段】遅延制御回路1は、基準クロック信号を遅延させる基準可変遅延回路3と、ストローブ信号を遅延させるストローブ可変遅延回路17と、同一構成である上記可変遅延回路3,17にテスト用遅延時間を設定するテスト用遅延制御回路9と、を備える。両可変遅延回路3,17のテストの際、当該回路3,17にはテスト用遅延時間が設定され、基準可変遅延回路3を経て遅延された基準クロック信号はストローブ可変遅延回路17に入力される。また、テストの際、テスト用遅延制御回路9は、合計遅延時間を一定にしたまま、テスト用遅延時間の一方を増加させ他方を減少させてゆく。

(もっと読む)

メモリデバイストレーニングのために組み込まれたプログラム可能要素

【解決手段】

メモリデバイスがその入力又は動作環境における変化に応答してそれ自身を適応させ又はトレーニングすることができるシステム及び方法。メモリデバイス、例えばDRAMは、組み込まれたプログラム可能要素をそのインタフェース内に含む。プログラム可能要素は、例えば限定はされないがマイクロプロセッサ、マイクロコントローラ、又はマイクロシーケンサであってよい。プログラム可能要素は、メモリデバイスの環境における変化に応答して、メモリデバイスのインタフェースの動作に変化を生じさせるようにプログラムされる。

(もっと読む)

共有多重ポートメモリ装置におけるバンク共有およびリフレッシュ

多重ポート(120)メモリ装置(100)内のメモリバンク(110)を構成要素間で共有するための方法およびシステムが提供される。多重ポートメモリ装置は、システムの構成要素が取り付けられる複数のポートと、ポートのそれぞれにより共有される多重ポートメモリ装置内の複数のメモリバンクとを含む。各メモリバンクの各ポートにはバンク可用性ピンが追加される。バンクが特定ポートに対して使用可能な場合にはバンク可用性ピンはシグナリングされ、バンクが使用不能な場合にはバンク可用性ピンはシグナリングされない。こうして、共有を支援する少量の追加ハードウェアのみで、多重ポートメモリ装置をいくつかの構成要素により同時に共有させることができる。また、メモリバンクをリフレッシュする方法が提供される。  (もっと読む)

(もっと読む)

記憶装置及び記憶素子のアクセス方法

【課題】フレームバッファの消費電力を低減し動作効率を向上させる。

【解決手段】 制御部108は画像データを出力部103のフレームバッファに書き込んで、出力部103はフレームバッファに記憶された画像データをLCD124に出力して表示させる。出力部103は、LCD124の周期的な表示リフレッシュに伴って、フレームバッファから画像データを読み出してLCD124に供給する一方で、読み出しにより破壊された記憶内容を復元するためにプリチャージする。ただし、次のリフレッシタイミングまでに、データの書き込みが予定されている場合には、利用されないデータを書き込むことになるプリチャージを行わない。

(もっと読む)

メモリ制御装置

【課題】DRAMのリフレッシュを実行しつつ、DRAMに係るデータ転送効率を向上する。

【解決手段】リフレッシュ制御部63は、DRAM4のリフレッシュを実行してもよいタイミングを示す第1要求信号と、リフレッシュを必ず実行しなくてはならないタイミングを示す第2要求信号との2つのリフレッシュ要求信号をアービトレータ41に発信する。一方で、アービトレータ41には、複数のデータ転送部7a〜7eそれぞれからデータ転送を要求する転送要求信号が発信される。アービトレータ41に第1要求信号が入力さたときに、転送要求信号が入力されていなければ、DRAM4においてリフレッシュが実行される。これにより、バス20が混雑度が比較的低いときにリフレッシュが実行されるため、データ転送効率を向上できる。

(もっと読む)

メモリ集積回路装置

【課題】高速でデータをアクセスすることのできる混載メモリを提供する。

【解決手段】矩形状のダイナミック・ランダム・アクセス・メモリセルアレイ(1)の4辺それぞれにレジスタ(20,22,30,32)を配置する。これらのレジスタは、メモリセルアレイの内部データ転送に用いられる内部データバス線(GIO0−GIOn;GIO0−GIO127;SGIO0−SGIOn)を介して相互接続される。内部データバス線はメモリセル上を渡って列方向に延在するように配置される。

(もっと読む)

半導体集積回路装置

【課題】安定的に動作する内部電源回路等を備えた半導体集積回路装置を提供する。

【解決手段】外部からの電源電圧で動作し内部電圧を形成する電源回路と、内部電圧が印加された内部回路とを備える。チャージポンプ回路の出力電圧と内部電圧との間に可変インピーダンス手段を設け、内部電圧に対応された基準電圧と内部電圧とを比較して両者が一致するよう可変インピーダンス手段を制御し、外部から供給された電圧と同じ極性の電圧を形成する第1電源回路及び異なる極性の電圧を形成する第2電源回路を設ける。第1電源回路のチャージポンプ回路の出力電圧は、内部回路を構成する素子が形成されるP型ウェルが形成されるN型ウェルに印加する。第2電源回路のチャージポンプ回路で形成された出力電圧は、内部回路を構成する素子が形成される上記P型ウェルに与えられる基板バックバイアス電圧としても用いる。

(もっと読む)

半導体記憶装置

【課題】2のべき乗より少ない個数のメモリセルを有する半導体メモリにおいて、物理的に存在しないメモリセルを選択した際の消費電力を削減する。

【解決手段】アドレス入力がなされた場合、物理的に存在しない無効なアドレス入力か否か判断する回路を設け、無効なアドレスである場合にはセンスアンプやライトアンプ等の周辺回路を不活性化することにより消費電力を削減する。

(もっと読む)

半導体メモリ

【課題】 電源ノイズを小さくし、半導体メモリの誤動作を防止する。

【解決手段】 コラムメモリブロック群は、縦方向に配列されたメモリブロックにより構成される。ロウメモリブロック群は、横方向に配列されたメモリブロックにより構成される。第1ロウアドレスデコーダは、第1ロウアドレスに応じて複数の第1デコード信号のいずれかを活性化する。各ロウメモリブロック群に対応し、共通の電源線に接続された複数の増幅回路ブロックは、互いに異なる第1デコード信号を受ける。同時に動作する増幅回路ブロックに、異なる電源線を用いて電源が供給されるため、電源電圧のドロップを小さくでき、電源線に発生する電源ノイズを低減できる。この結果、半導体メモリの誤動作を防止できる。増幅回路ブロック上に配線される電源線の本数を少なくできるため、電源線のレイアウトの余裕度を大きくできる。

(もっと読む)

半導体記憶装置

【課題】1つのメモリセルMCに対して2系統でアクセスできるようにする。

【解決手段】複数のメモリセルから構成されたメモリセルアレイを有し、各メモリセルは、フローティングボディを共有する第1、第2MISFETからなり、それぞれのドレインは異なるビット線に、ゲートは異なるワード線に接続されており、前記メモリセルアレイのビット線の一方側に配置された第1センスアンプ回路と、ビット線の他方側に配置された第2センスアンプ回路と、前記メモリセルに対して第1の動作サイクルで読み出し又は書き込み動作である通常動作を行うために入力される第1外部ローアドレスと、第2の動作サイクルで通常動作を行うために入力される第2外部ローアドレスとを比較するローアドレス比較回路と、前記ローアドレス比較回路の比較結果に基づいて、前記第1、第2の動作サイクルにおけるアクセスをコントロールするコントロール回路と、を更に備える。

(もっと読む)

ゲート制御ダイオードを使用するメモリ・セルおよびこれの使用方法、半導体構造

【課題】改良型3T1Dメモリ・セルを提供する。

【解決手段】メモリ・セルは、(1)第1の端子がビットラインに結合され、制御端子が第1の制御線に結合されている書込みスイッチ1325と、(2)2端子半導体デバイスの第1の端子が書込みスイッチの第2の端子に結合され、第2の端子が少なくとも1つの第2の制御線に結合され、第2の端子に対する第1の端子の電圧が閾値電圧を超えるときのキャパシタンスが閾値電圧を超えないときのキャパシタンスよりも大きくなる2端子半導体デバイス1330と、(3)制御端子が第2の制御線に結合され、第1の端子がビットラインに結合されている読出し選択スイッチ1340と、(4)制御端子がゲート制御ダイオードの第1の端子と書込みスイッチの第2の端子とに結合され、第1の端子が読出し選択ゲートの第2の端子に結合され、さらに、第2の端子が接地されている読出しスイッチ1345と、を備える。

(もっと読む)

半導体集積回路装置およびその制御方法

【課題】 DRAMおよびシステムLSIを備える半導体集積回路装置の円滑かつ効率的な検査を可能とする。

【解決手段】 システムLSI102の内部に、通常動作用のDRAM制御回路108とは別に、テスト用DRAM制御回路112を設ける。そして、システムLSI102の個別検査時において、DRAM104が悪影響を与えないように、DRAM104のデータバスをハイインピーダンス状態とする、あるいは、DRAM104をディープパワーダウンモード等に移行させる。

(もっと読む)

半導体装置

【課題】アドレス空間が異なる複数のメモリブロックに対して、同時にテストを行う。

【解決手段】半導体装置1は、第1アドレス空間を有する第1メモリブロックMCR1と、前記第1アドレス空間より小さい第2アドレス空間を有する第2メモリブロックMCR2と、前記第1及び第2メモリブロックに対してテストアドレス及びテスト制御信号を供給し、且つ前記第1及び第2メモリブロックのテストを同時に行うテスト回路2とを具備し、前記第2メモリブロックMCR2は、前記第2アドレス空間に対応するアドレスを記憶する記憶回路3aと、前記第2アドレス空間を超えたアドレスが前記テスト回路2により指定された場合に、前記テスト制御信号を不活性にする制御回路3bとを含む。

(もっと読む)

メモリテストモードインターフェース方法及び装置

メモリシステムに実装されたメモリモジュールやメモリモジュール上に装着されたメモリをよいにテストモードに移行させることができる方法及びそれを実施するためのメモリ制御用レジスタの構造を提供する。メモリ製造会社毎にテストモードで移行するためのMRSコード及び移行方法を異なるようにするので、メモリ制御用レジスタにメモリのテストMTS回数を入力し、テストMRSコードを設定する。また、テストMRS回数を決定するレジスタのそれぞれのビットにはテストMRSコードを格納しているレジスタが割り当てられている。  (もっと読む)

(もっと読む)

1 - 18 / 18

[ Back to top ]