国際特許分類[C25D7/12]の内容

化学;冶金 (1,075,549) | 電気分解または電気泳動方法;そのための装置 (15,555) | 電気分解または電気泳動による被覆方法;電鋳 (10,553) | 被覆される物品に特徴のある電気鍍金 (2,030) | 半導体 (400)

国際特許分類[C25D7/12]に分類される特許

101 - 110 / 400

半導体ウエハ上に実質的に均一な銅析出を行う方法

先の出願に記載された2以上の電極を備える電気化学析出装置にて用いられる方法が開示される。この方法によれば、0.02〜0.8S/cmの範囲の伝導度の硫酸銅ベースの電解液にて、50〜900Åの厚さの抵抗銅シード層を有する半導体ウエハに、WFNUが2.5%より小さい値で均一な銅フィルムが形成される。  (もっと読む)

(もっと読む)

半導体上での光誘導めっき方法

【課題】太陽光発電および太陽電池のような半導体上にニッケルを光誘導めっきする方法において、均一であり、かつドープされた半導体基体への許容できる接着性を有する、厚みの薄いニッケル堆積物を提供する。

【解決手段】めっきプロセスを開始するために、半導体に初期光強度8000ルクス〜20,000ルクス、または例えば10,000ルクス〜15,000ルクスの光を、典型的には、0.25秒〜15秒間、より典型的には2秒〜15秒間、最も典型的には5秒〜10秒間適用し、続いて、残りの期間、光の強度を典型的には、初期光強度の20%〜50%、または例えば30%〜40%低減させる。

(もっと読む)

金属配線膜の抽出洗浄方法、抽出洗浄処理された金属配線およびこの金属配線を有するデバイス

【課題】 銅等の金属配線の電気抵抗低減および安定化を実現し、銅等の金属配線の信頼性を向上させることが可能な金属配線膜の抽出洗浄方法、抽出洗浄処理された金属配線およびこの金属配線を有するデバイスを提供することである。また、配線構造を形成する過程で配線あるいはデバイス構成材料中に取り込まれた不純物を除去し、配線膜の比抵抗値の上昇を防止し、信頼性を高めることのできる金属配線膜の抽出洗浄方法、抽出洗浄処理された金属配線およびこの金属配線を有するデバイスを提供する。

【解決手段】 半導体ウエハー上にめっき法あるいは気相堆積法により形成された金属配線膜を常圧より高圧の二酸化炭素または不活性の気体ないし流体中に一定時間曝して処理する金属配線膜の抽出洗浄方法、抽出洗浄処理された配線およびこの配線を有するデバイスとした。

(もっと読む)

フープ部材への部分メッキ膜の形成方法

【課題】微細且つ複雑な形状に加工されたフープ部材の所望の位置に高精度にメッキ膜を形成する方法を提供することを目的とする。

【解決手段】連続して送り出されるフープ状の導電性基材の表面に自己組織化膜を形成する自己組織化膜形成工程と、連続して送り出されるフープ状の導電性基材表面の前記自己組織化膜の所望の部分を除去する膜除去工程と、連続して送り出されるフープ状の導電性基材表面の前記自己組織化膜が除去された部分に電気メッキにより導電膜を形成するする電気メッキ工程とを備えるフープ部材への部分メッキ膜の形成方法を用いる。

(もっと読む)

電解処理装置及び電解処理方法

【課題】例えばルテニウム膜をシード層として該ルテニウム膜の表面にダイレクトめっきを行うのに先立って、たとえ300mmウェーハ等の大型の高抵抗基板であっても、ルテニウム膜表面の不動態層を確実に除去することで、その後のめっき時におけるターミナルエフェクトを改善し、しかも、めっき膜の膜質を改善し、微細配線パターンの内部にボイドのないめっき膜を埋込むことができる電解処理装置及び電解方法を提供する。

【解決手段】貴金属または高融点金属からなるシード層を有する基板Wの該シード層と対向する位置に配置されるアノード52と、電解液62で満たされた基板Wとアノード52との間に、内部に電解液を含浸させて配置される多孔質体46と、シード層表面の電場を制御してシード層表面に形成された不動態層を電解処理により電気化学的に除去する制御部58を有する。

(もっと読む)

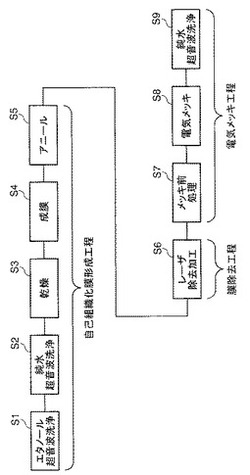

半導体装置の製造方法および半導体装置の製造装置

【課題】めっき液に含まれる構成成分の濃度を演算し、めっき液の調整を適正に行い、めっき処理の品質を維持する。

【解決手段】めっき液に一または複数の添加剤を加えて半導体ウエハにめっき処理を行う工程(ステップS1)と、めっき処理の処理状態を示す一または複数のパラメータを測定する工程(ステップS3)と、パラメータからめっき液に含まれる構成成分の濃度を演算する工程(ステップS4)と、演算された構成成分の濃度が予め定めた閾値以内に収まるように、めっき液の調整処理を行う工程(ステップS6)と、を備える。

(もっと読む)

半導体装置の製造方法、半導体装置及び半導体装置の製造装置

【課題】製造工程数を増加させることなく配線上にキャップメタル膜を選択的に形成することにより、配線間リーク電流の増大及び配線間ショートを抑制する。

【解決手段】絶縁膜に埋め込まれた配線を有する半導体装置の製造方法において、基板上に形成された絶縁膜に溝を形成する工程と、前記溝に導電膜を埋め込む工程と、それぞれに電解液が注入された複数の貫通孔を有する基体を前記導電膜の表面に接触させながら、前記電解液と電気的に接続されたアノードと前記基体表面に露出したカソードとの間に電位差を付与することで、前記導電膜が埋め込まれた前記絶縁膜を表面処理する工程と、を有することを特徴とする半導体装置の製造方法。

(もっと読む)

電気めっき装置、及び電気めっき方法

【課題】通電電極を下地電極に接続する際のウエハに対する物理的ストレス軽減するめっき装置及びめっき方法を提供する。

【解決手段】本発明によるめっき装置は、半導体基板31上の下地電極層に密着可能な開口部220を有するカバー22と、下地電極層上の絶縁膜33を溶解する溶剤をカバー22によって覆われた領域に供給し、カバー22によって覆われた下地電極32上の絶縁膜33を除去する溶剤供給部40と、絶縁膜33が除去されることで露出した下地電極32に、開口部220を介して当接する通電電極21とを具備する。

(もっと読む)

めっき装置及びめっき方法

【課題】表面により高いシート抵抗をもつ基板に対しても、基板の全表面により均一な膜厚のめっき膜を形成できるようにする。

【解決手段】基板Wの表面の周縁部に当接して該周縁部をシールするシール材90と、基板Wの表面に形成した導電層に接触して通電させるカソード接点88と、ハウジング94の内部にアノード98を収納し開口端部に多孔質体110を配置してめっき液室100を区画形成した電極ヘッド28と、基板Wと多孔質体110との間にめっき液を満たしたまま、電極ヘッド28を第1めっき位置から該第1めっき位置よりも基板Wと多孔質体110との距離が離れた第2めっき位置に移動させて停止させる駆動機構136と、基板Wの外周部に対向する位置に該基板Wと離間して配置され、基板Wと多孔質体110との間に満たしためっき液に浸漬される補助カソード部124を有する。

(もっと読む)

導電材料構造体の形成方法

【課題】実用化の障害となるめっきの長時間化を改善し、貫通電極による三次元実装を実現するのに好適な導電材料構造体をより短時間で形成できるようにする。

【解決手段】貫通電極用凹部12を形成した基板Wの表面の該凹部12表面を含む全表面に導電膜14を形成し、基板W表面の所定位置にレジストパターン30を形成し、導電膜14を給電層とした第1めっき条件で第1電解めっきを行って貫通電極用凹部12内に第1めっき膜36を埋込み、貫通電極用凹12部内への第1めっき膜36の埋込みが終了した後に、導電膜14及び第1めっき膜36を給電層とした第2めっき条件で第2電解めっきを行って、レジストパターン30のレジスト開口部32に露出した導電膜14及び第1めっき膜36上に第2めっき膜38を成長させる。

(もっと読む)

101 - 110 / 400

[ Back to top ]