国際特許分類[G06F1/24]の内容

物理学 (1,541,580) | 計算;計数 (381,677) | 電気的デジタルデータ処理 (228,215) | グループ3/00〜13/00および21/00に包含されないデータ処理装置の細部 (14,213) | リセット手段 (409)

国際特許分類[G06F1/24]に分類される特許

81 - 90 / 409

データ処理装置

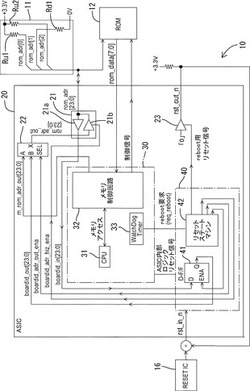

【課題】リブート時の初期値設定を速やかに行うデータ処理装置を提供すること。

【解決手段】データ処理装置10は、プルアップ抵抗Ruあるいはプルダウン抵抗Rdに接続される複数の信号線であって、初期設定データboardid_in[2:0]を生成する複数の信号線rom_adr[2:0]と、当該装置10の電源投入時において、前記初期設定データboardid_in[2:0]によって当該装置10の初期設定を行う設定部42と、初期設定データboardid_in[2:0]を保持する保持部41とを含む。設定部42は、電源投入時に初期設定データboardid_in[2:0]を保持部41に保持させ、当該装置10のリブート時において、保持部41に保持された初期設定データboardid_in[2:0]を利用して当該装置10を再初期設定する。

(もっと読む)

制御装置の初期化方法

【課題】制御装置において初期化処理する回路の初期設定値に変更が必要になった場合にファームウェア自体を変更せずに初期化処理を変更可能とし、また、保存されている初期設定値に不測の誤りが生じた場合でも誤った設定値で該回路を初期化してしまうことを防ぐことができる制御装置の初期化方法を提供する。

【解決手段】制御装置の初期化方法は、初期化対象回路を初期化するための初期設定プログラムが記憶された第1の記憶部と前記初期化対象回路の初期設定値が記憶された第2の記憶部とを具備し、初期設定プログラムを実行するにあたり前記第2の記憶部から前記誤り検出符号を読み出して前記初期設定値の誤りの有無を検出し、誤りが検出されない場合に前記初期設定値を用いて前記初期化対象回路の初期化を行い、誤りが検出された場合に前記別の初期設定値を用いて前記初期化対象回路の初期化を行う。

(もっと読む)

処理システム、動作状態制御方法及びコンピュータプログラム

【課題】一の処理装置からの制御にて他の処理装置の動作を停止又は起動させ、消費電力をより効果的に低減させることができる処理システム、動作状態制御方法及びコンピュータプログラムを提供する。

【解決手段】ECU2は、ECU1が休止(スリープ)状態へ遷移可と判断した場合、ECU1のマイコンのRESET端子へのRESET信号を入力し続ける。マイコン100では、RESET信号が入力され続けると、リセットがかかり続けて動作が停止する。

(もっと読む)

情報処理装置、情報処理方法、及びプログラム

【課題】デバイスドライバの解析及びデバイスドライバの改竄を防止し、より高い安全性を確保することを目的とする。

【解決手段】第1のオペレーションシステム及び第2のオペレーションシステムを含むマルチOS環境下において、第2のオペレーションシステムが、第1のオペレーションシステムが使用するデバイスについて、デバイスの初期化を行うデバイス初期化部と、デバイスの利用状況を監視するデバイス監視部と、デバイスの異常を検知する異常検知部と、を有することによって課題を解決する。

(もっと読む)

システム初期化の動作中にプラットフォーム・グラフィクスを表示するための方法及びシステム

【課題】 オペレーティング・システムの初期化に割り込む機能と、オペレーティング・システムの初期化が割り込まれるとビデオ・フレーム・バッファをプラットフォーム・グラフィクス・データで更新する機能と、オペレーティング・システム初期化ロジックによって生成されたグラフィクス、及びプラットフォーム・グラフィクス・データをマージする機能とを含む、コンピュータの初期化中にプラットフォーム・グラフィクスを表示するための方法及びシステム。

【解決手段】 方法及びシステムは、仮想化方法及び仮想化システム、並びにシステム管理モード方法及びシステム管理モード・システムを含む。

(もっと読む)

集積回路

【課題】 クロックゲーテイングの同期リセット型同期FFを用いたASICのパワーオン時や、ASICのリセット端子を用いたスタンバイ時のローノイズ化、低昇温化、省電力に関する。

【解決手段】 同期リセットFF回路や、クロックドゲートで制御される同期リセットFF回路で設計された同期リセットFF回路で構成された回路を含むASICで、ASICの外部から外部リセット信号が入力できるリセット端子を具備し、少なくともそのリセット端子には、パワーオン時にリセットICによるパワーオンリセット信号が入力され、その外部リセット信号がアクテブ状態から非アクテブ状態に遷移するタイミングを基準として、ASIC内部の回路(リセット制御回路を除く)を初期化するためのリセット信号を生成するリセット制御回路を具備する。

(もっと読む)

パワーオンリセット回路および該パワーオンリセット回路を有するモジュールならびに電子回路

【課題】パワーオンリセット信号を誤作動せず確実に発生させることができ、従来技術より短時間で電源電圧や製造時のバラツキによらない任意の一定時間オンとなるパワーオンリセット信号を発生するパワーオンリセット回路技術の提供。

【解決手段】P型MOSトランジスタP1と第1のコンデンサC1からなる充電回路1と、該充電回路1の出力とパワーオンリセット信号PORを入力して動作するNOR回路NOR1と、NOR回路NOR1と直列に接続されたインバータ回路INV1と、NOR回路NOR1の入力とインバータ回路INV1の出力の間に接続されるコンデンサC2と、クロックCKをカウントするカウンタ回路2と、カウンタ回路2の出力によりクロックの出力または停止を選択するクロック選択回路3と、カウンタ回路2の出力に接続されパワーオンリセット信号PORを出力するインバータ回路INV2を備える。カウンタ回路2は一段以上のフリップフロップから構成される。

(もっと読む)

電子機器、起動方法および起動プログラム

【課題】 起動までの時間を短くするととともにバッテリを有効に利用すること。

【解決手段】 デジタルスチルカメラは、バッテリから電力の供給を受けて駆動するレンズ駆動部、手振れ補正ユニット、イメージセンサ、LCDを含む複数の負荷手段と、バッテリの残量を検出する検出手段(S01)と、複数の負荷手段を制御する制御部11と、を備え、制御部11は、起動までの時間の異なる第1および第2のシーケンスのうちから検出された残量が少ないほど起動までの時間の長いシーケンスを選択し、選ばれたシーケンスに従って複数の負荷手段を初期化する(S02、S03)。

(もっと読む)

コンフィグレーション装置、コンフィグレーション方法、及びコンフィグレーションプログラム

【課題】集積回路のコンフィグレーションを、短時間で効率よく行うコンフィグレーション装置等を提供する。

【解決手段】FPGA140の回路設定情報を固定長に分割されたブロック単位で格納する回路設定情報格納メモリ120と、回路設定情報をブロック単位で読み出し、FPGA140に、読み出したブロック単位の回路設定情報を出力する設定情報制御デバイス130と、FPGA140における回路設定情報の書き込みが可能な設定情報書込可能領域150が、ブロックごとに物理的に分割されており、設定情報制御デバイス130が出力したブロック単位の回路設定情報を入力し、入力した回路設定情報を書き込む対象となる領域を分割された書込可能領域から選択する書込領域選択部220と、選択された書込対象領域に、設定情報制御デバイス130から出力されたブロック単位の回路設定情報を書き込むコンフィグレーション制御部210とを備える。

(もっと読む)

USB機器、及びUSB接続システム

【課題】ホストからのリセットに基づいてリセット動作を実行できるUSB機器、これに接続するホスト装置、及びUSB接続システムを提供し、内部通信障害の復旧等のリセット動作を可能として可用性を向上する。

【解決手段】USB機器に、通常モードでは機器全体の制御動作を実行すると共に、省エネモードではその動作を停止するCPUと、CPUの通常モード及び省エネモードを監視すると共に、CPUに供給するクロック信号の切り替えにより両モード間を状態遷移させる状態監視回路を備え、リセット信号を受信したとき、CPUが省エネモードの場合には、CPUを通常モードへ状態遷移させる一方、CPUが通常モードの場合には、CPU及びUSB通信手段をリセットさせる信号をリセット回路に送信することを特徴とする。

(もっと読む)

81 - 90 / 409

[ Back to top ]