国際特許分類[G06F12/02]の内容

物理学 (1,541,580) | 計算;計数 (381,677) | 電気的デジタルデータ処理 (228,215) | メモリ・システムまたはアーキテクチャ内でのアクセシング,アドレシングまたはアロケーティング (20,382) | アドレシングまたはアロケーション;リロケーション (4,708)

国際特許分類[G06F12/02]の下位に属する分類

可変長語,または語の一部,のアドレシング (194)

ロケーションの物理的ブロックのアドレシング,例.ベース・アドレシング,モジュール・アドレシング,メモリ空間拡張,メモリ専用 (1,078)

階層構造のメモリ・システム,例.仮想メモリ・システム,におけるもの (2,277)

国際特許分類[G06F12/02]に分類される特許

81 - 90 / 1,159

半導体記憶装置、及び記憶媒体

【課題】ガベージコレクション処理による処理負荷を軽減し、ガベージコレクション処理の処理時間を短縮する。

【解決手段】フラッシュメモリ10は、予め定められたデータサイズ領域を示すページ単位でデータを書き込み可能な不揮発性記憶部11と、不揮発性記憶部11の指定された領域であって、複数のページを含む該指定された領域における有効データを一時記憶する記憶部12と、不揮発性記憶部11のページに有効なデータがあるか否かを示すアドレスマップ情報に基づいて、指定された領域における有効データを記憶部12に記憶させた後に、記憶部12に記憶された有効データを連続したページに書き込むガベージコレクション処理、及びガベージコレクション処理によって変更されたアドレスマップ情報を出力する処理を実行するコントロールロジック部13とを備える。

(もっと読む)

メモリコントローラ、及びデータ記録装置

【課題】管理テーブルを不揮発性メモリに保存する時の応答遅延時間を縮減し、データ記録装置の電源遮断後に、不揮発性メモリに保存した情報から管理テーブルを復元する機能を備えるメモリコントローラを提供する。

【解決手段】不揮発性メモリ1011は、管理テーブル格納ブロックと、データ書き込みのために割り当てたスクラッチブロックと、データを保持するデータブロックと、データを消去した消去済みブロックを持つ。メモリ1012は、データの格納場所を管理する論理・物理アドレス変換テーブル10120と、ブロック履歴管理テーブル10125を持つ。管理テーブル格納ブロックは、論理・物理アドレス変換テーブル10120とブロック履歴管理テーブル10125を保存する管理テーブルページを持つ。メモリコントローラ1010は、論理・物理アドレス変換テーブル10120の一部を不揮発性メモリ1011の管理テーブル格納ブロックに保存する。

(もっと読む)

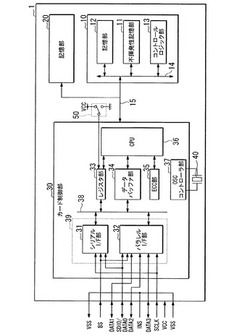

情報処理装置及び情報処理装置におけるデータ管理方法

【課題】電源オン/オフの際に、ブロックを分割した複数のデータ領域のうち読出し元及び書込み先のデータ領域を比較的簡単に特定できる情報処理装置及情報処理装置におけるデータ管理方法を提供する。

【解決手段】フラッシュメモリー装置の2つのブロックA,Bは、それぞれ1つの管理領域と複数のデータ領域とに分割され、管理領域にはROM状態とブロック状態と選択領域の各情報が格納される。電源オン時のデータ読出し時には、まず各ブロックA,Bの管理領域を読み出す(S11,S12)。管理領域Aのブロック状態が「使用中」であれば選択領域の指すデータ領域からデータを読み出す。一方、「消去可」であればブロックAのデータ消去を行う(S15)。ブロックBも同様に処理される(S17〜S20)。なお、電源オフ時のデータ書込みの際は、ブロックの全てのデータ領域が使い終わると、ブロック状態が「使用中」から「消去可」に変更される。

(もっと読む)

メモリシステム

【課題】転送効率を可及的に向上させること。

【解決手段】メモリシステムは、ストレージ領域を備える不揮発性メモリと、書き込みデータをストレージ領域に格納する転送処理部と、不要な書き込みデータを指定した削除通知を蓄積記憶する削除通知バッファと、削除通知にかかる書き込みデータを無効化する削除通知処理部とを備えている。削除通知処理部は、削除通知バッファから複数の削除通知を一括して読み出してストレージ領域よりも小さい単位領域毎に分類し、同一の単位領域に分類された削除通知にかかる書き込みデータを一括して無効化する処理を単位領域毎に実行する。削除通知処理部は、1つの単位領域にかかる処理を実行する際、無効化対象の書き込みデータを除く書き込みデータを別の単位領域に複製した後、前記1つの単位領域が記憶している全ての書き込みデータを無効化する。

(もっと読む)

画像処理装置及び画像処理プログラム

【課題】不要なメモリを早急に解放することができる。

【解決手段】ワークフロー管理部46Aは、画像処理モジュール38から自モジュールの消去通知が出力された場合において、該画像処理モジュール38の前段のバッファモジュール40の消去が可能と判断したときに、消去要求を該バッファモジュール40の前段の画像処理モジュール38に入力する。バッファモジュール40は、自モジュールに連結された全画像処理モジュール38が消去されると自モジュールを消去し、画像処理モジュール38は、画像処理部を構築する画像処理モジュール38の全ての処理が終了した場合、自モジュールの全処理が終了した場合、並びに消去要求が入力された場合又は消去要求が入力され且つ自モジュールの消去が可能と判断した場合に、消去通知をワークフロー管理部46Aに出力し自モジュールを消去する。消去されたモジュールに割り当てられていたメモリは解放される。

(もっと読む)

メモリ装置及びメモリ制御方法

【課題】ユーザデータの書き込み処理速度を向上することが可能なメモリ装置及びメモリ制御方法を提供する。

【解決手段】実施形態のメモリ装置によれば、第3の記憶部は、前記論理アドレスと前記中間アドレスに対応され、前記論理アドレス及び前記中間アドレスを用いた読み出し動作により、最新データの読み出しが成功したかどうかを示すフラグを記憶する。データ移動処理部は、前記メモリ部内のデータを移動処理する。制御手段は、前記データ移動処理部によるデータの移動処理において、前記第3の記憶部に記憶された前記フラグが最新データの読み出し成功を示す場合、前記データの移動処理中に前記メモリ部の同一論理アドレスに対して、書き込みが行われたかどうかを判定し、書き込みが行われている場合、前記データの移動処理を無効化させる。

(もっと読む)

メモリ装置、メモリ制御回路及びメモリ制御システム

【課題】画像データの矩形アクセスを効率的に行うメモリ装置、メモリ制御回路及びメモリ制御システムを提供すること。

【解決手段】メモリ装置は、Mビットのデータ入出力バスを備え入力クロックに同期してバンクアドレスとロウアドレスとコラムアドレスに対応した記憶セルに対してデータの読み書きを行い、入力クロックの1サイクル毎に2つのアクセス入力と読み出しバースト長フラグを受信し、第1の制御アクセスコマンドと第2の制御アクセスコマンドと読み出しバースト長信号とを出力する。制御アクセスコマンドが読み出し要求の場合に、読み出しバースト長信号で指定されたバースト長で指定する期間に、記憶セルからのデータ読み出し後にデータ入出力バスに読み出しデータを出力する。2バースト長の場合は、制御アクセスコマンドそれぞれに対応する記憶セルからの2つのMビットの読み出しデータを2サイクルの期間データ入出力バスに出力する。

(もっと読む)

マルチタイリングを用いたメモリアクセス

【課題】タイル状および非タイル状メモリアクセスを含むメモリアクセスタイプのデータを動的に操作する。

【解決手段】アドレス前スウィズル回路330は、アクセス制御信号に従い、プロセッサにより提供されるアドレスビットを調整する。データステアリング回路310は、メモリにおけるN個のサブチャネルに接続し、アクセス制御信号、調整済みアドレスビット、および、N個のサブチャネルに関連付けられたサブチャネル識別子に従い、タイル状および非タイル状メモリアクセスを含むメモリアクセスタイプのデータを動的に操作する。タイル状メモリアクセスは、水平および垂直のタイル状メモリアクセスを含む。アドレス後スウィズル回路3350〜3353は、調整済みアドレスビットを用い、アクセス制御信号およびサブチャネル識別子に従い、N個のサブチャネルに対するサブチャネルアドレスビットを生成する。

(もっと読む)

記憶装置

【課題】書き込み効率の向上を図る。

【解決手段】第1記憶部と第2記憶部と制御部とを具備する記憶装置であって、第1記憶部は複数のページを含む複数のブロックを有し、第2記憶部は第1記憶部における書き込み可能なブロックの情報を保持するフリーブロックリストと第1記憶部における書き込み可能なページの情報を保持するフリーページリストとを有し、制御部は第1記憶部にホストからのデータを転送する際、ブロック単位のデータを圧縮して圧縮ブロックデータを生成し、圧縮ブロックデータをフリーブロックリストに情報が保持されたブロックに書き込み、圧縮ブロックデータが書き込まれたブロック内において圧縮ブロックデータが書き込まれていないフリー領域に存在するページの情報をフリーページリストに保持し、ページ単位のデータをフリーページリストに情報が保持されたページに書き込む。

(もっと読む)

共有されるL2マッピング・キャッシュのための対称的割り当てのための方法およびシステム

【課題】タイル式メモリからデータを読み取るための方法、装置、システムおよび媒体を提供する。

【解決手段】一つのタイル式X方式キャッシュ読み取り要求について、そのタイル式X方式キャッシュ読み取り要求を分解することなくタイル式メモリから二つのキャッシュ・ラインを要求する段階305と、二つの要求されたキャッシュ・ラインに関連付けられたデータを返す段階325とを含む。また、二つのキャッシュ・ラインを並列に割り当てる段階310と、二つのキャッシュ・ラインの整合性を並列に維持する段階315と、二つのキャッシュ・ラインに関連付けられたデータをデータ・キャッシュから並列に読む段階320を含む。

(もっと読む)

81 - 90 / 1,159

[ Back to top ]