国際特許分類[G06F15/167]の内容

物理学 (1,541,580) | 計算;計数 (381,677) | 電気的デジタルデータ処理 (228,215) | デジタル計算機一般 (4,503) | 各々が少くとも算術演算ユニット,プログラム・ユニットおよびレジスタをもつ2つ以上のデジタル計算機が結合されたもの,例.数個のプログラムの同時処理を行うためのもの (694) | プロセッサ間通信 (496) | 共通メモリ,例.メイルボックス,を用いるもの (160)

国際特許分類[G06F15/167]に分類される特許

11 - 20 / 160

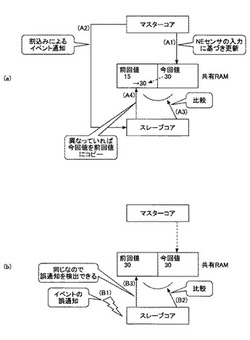

マイコン、処理同期方法

【課題】一方のコアから他方のコアに割込みによりイベントを通知する際、イベントの誤通知を検知できるマイコンを提供すること。

【解決手段】第1のコア52と第2のコア53間で通信する通信手段43と、第1のコアと第2のコアが共有する共有メモリ51と、外部信号を取得して第1の処理を実行し、第1の処理毎に所定情報を共有メモリに書き込む第1の処理手段55と、通信手段を介して第2のコアに処理要求を出力する処理要求手段33と、処理要求をトリガーに第2の処理を実行する第2の処理手段56と、を有するマイコン100において、第2のコアは、処理要求を受け付けた場合、共有メモリから最新の所定情報と前回の所定情報を読み出し、最新の所定情報と前回の所定情報に規定された関係がある場合のみ、第2の処理手段に第2の処理の実行を許可する比較手段57、を有する。

(もっと読む)

要求転送装置及び要求転送方法

【課題】スループットを維持しつつ、命令間の順序保証を行うこと。

【解決手段】本発明にかかる要求転送装置は、複数の要求元のそれぞれから、複数の要求先のいずれかが指定された複数の要求を含む要求群を受け付け、受け付けた要求群に含まれる各要求に対して、当該要求群を識別するための識別情報を付加し、識別情報を対応付けた複数の領域に予め分割され、複数の要求先に対応する複数のバッファのうち、各要求に指定された要求先に対応するバッファ内で付加された識別情報に対応付けられた領域へ各要求を格納し、複数のバッファのそれぞれから、識別情報に対応付けられた領域単位に、格納された要求を読み出し、読み出した要求を、当該要求に指定された要求先へ出力する。

(もっと読む)

メモリ管理装置、マルチプロセッサシステム、及びメモリ管理方法

【課題】共有メモリを共有するための処理を並列化し、共有メモリのフラグメンテーションを抑制し、データのコピー回数を低減し、且つDMAモジュールが要求するサイズの境界とデータの先頭アドレスとの間のアライメントをとる。

【解決手段】メモリ管理装置13は、複数のプロセッサ12a,12bにより共有される共有メモリ14を管理する。各プロセッサに割り当てられる共有メモリ14のメモリ領域を確保し、各メモリ領域に複数のプロセッサと1対1に対応する複数のリファレンスカウンタを設ける。メモリ領域を各プロセッサに割り当てるときに、メモリ領域を管理するプロセッサに対応するリファレンスカウンタに1を加算し、メモリ領域を解放するときにリファレンスカウンタから1を減算する。更新されたメモリ領域における複数のリファレンスカウンタの値の合算結果が0である場合に、メモリ領域が割り当てられたプロセッサからメモリ領域を解放する。

(もっと読む)

制御装置

【課題】装置の小型化を図ること。

【解決手段】制御回路100は、CPU10と、CPU10で動作させる第1のプログラムを記憶するフラッシュメモリ22を有するCPU20と、第1のプログラムをCPU10に読み込ませる第2のプログラムを記憶するROM33とを有している。CPU10は、読み出した第2のプログラムを実行することで第1のプログラムの読み込み準備完了をCPU20に通知する。CPU20は、第1のプログラムの読み込み準備完了に基づいて、CPU10への第1のプログラムの転送を開始する。

(もっと読む)

共有キャッシュメモリ装置

【課題】2個のプロセッサに、より高速に連携した処理を行わせることが可能な共有キャッシュメモリ装置を提供する。

【解決手段】共有キャッシュメモリ装置を、第1プロセッサが生成して第2プロセッサが利用するデータを記憶するための幾つかの監視対象記憶領域をデータメモリ部33に確保する機能、管理対象記憶領域毎に第1プロセッサによるデータの書き込みが行われたか否かを管理する機能、データの書き込みが完了していない監視対象記憶領域上のデータを要求するリード要求を受信したときに、その監視対象記憶領域へのデータの書き込みが第1プロセッサにより行われるのを待機してから、当該リード要求に応答する機能を有する装置として構成しておく。

(もっと読む)

電子機器

【課題】複数のCPU間で効率よくデータ授受を行うことができる電子機器を提供すること。

【解決手段】共有メモリを介して複数のCPU間でデータの授受を行うように構成された電子機器において、前記共有メモリには、

前記授受されるデータを格納する唯一のFIFOと、前記FIFOのデータ格納位置情報とデータ取り出し位置情報と作業情報としてのデータ取り出し位置情報を含むFIFOの管理情報を格納するFIFO管理情報格納部と、前記データの処理を即座に実行できないときに当該データ処理を保留にするための保留要求管理情報を格納する保留要求管理情報格納部が設けられていることを特徴とするもの。

(もっと読む)

共有メモリシステム及びその制御方法

【課題】処理時間の短縮及び消費電力の低減が可能な共有メモリシステムを提供すること。

【解決手段】共有メモリシステムは、アクセス監視機構112に対し、動画属性用のクラスタをクラスタメモリ1、2とする定義を行う。アクセス監視機構112は、DSP(2)104が画像の属性情報を付加してメモリアクセスを行うと、クラスタメモリ1、2に対してアクセス許可を示す制御情報131をクラスタメモリ空間選択装置119に出力する。クラスタメモリ空間選択装置119は、制御情報131に従って、DSP(2)104からのアクセスをクラスタメモリ1もしくは2に振り分ける。GPU105からのアクセスも同様である。複数のクラスタ111に分割された共有メモリ110を複数のマスタが共有することで、キャッシュメモリのコヒーレンシを保つ。

(もっと読む)

FIFOデータ読出装置

【課題】1個のFIFO回路に格納されているデータを複数のCPUが互いに独立して読出せるFIFOデータ読出装置を提供する。

【解決手段】CPU2およびCPU4によるFIFO回路12に対する読出要求は、FIFO読出回路20により処理される。FIFO回路12に対するCPU2による総読出回数がCPU4による総読出回数以上であれば、FIFO読出回路20はFIFO回路12からデータを読み出してCPU2に送出するとともに、CPU4用のDPRAM32にそのデータを書き込む。CPU2による総読出回数がCPU4による総読出回数よりも小さい場合、CPU2によるFIFO回路12に対する読出要求に対応するデータは、すでにCPU4に送出されているとともにCPU2用のDPRAM30に書き込まれているので、FIFO読出回路20は、DPRAM30の該当アドレス位置からデータを読出してCPU2に出力する。

(もっと読む)

CPU間通信システム及びCPU間通信方法

【課題】CPU間通信において、同期の待ち時間に応じてウェイト処理を最適に制御できるようにする。

【解決手段】送信側CPUと受信側CPUとがメモリ104を介してデータ通信を行うCPU間通信システム800において、送信側CPUは、メモリ104に空き領域があるかを判定するメモリ領域判定部351と、空き領域がある場合に、メモリ104にデータを書き込むデータ書き込み部352と、空き領域がない場合に、受信側CPUの状態を判定する受信側CPU判定部353と、受信側CPUの状態がデータ読み出し処理の実行状態である場合に、メモリ104に空き領域ができるまでデータ書き込み部352を待ち状態とし、受信側CPUの状態がデータ読み出し処理の実行状態でない場合に、受信側CPUにデータ読み出し処理の実行を開始させるための読み出し開始要求を受信側CPUへ送信する送信側制御部354とを備える。

(もっと読む)

半導体装置

【課題】複数のバスマスタを備えた半導体装置において、バススレーブに対する処理を従来よりも効率的に実行できる半導体装置を提供する。

【解決手段】半導体装置100において、各マスタ装置M0〜Mnは、複数のバスB0〜B4に接続され、複数のバスのうちの割当てられた1本のバスを介してスレーブ装置30に対する処理要求をコントローラ20に出力する。複数のマスタ装置M0〜Mnの各々には割当優先度が定められる。調停回路11は、複数のマスタ装置M0〜Mnのうちバスの割当を要求している1または複数のマスタ装置に対して、バスの割当を要求したタイミングと割当優先度とに基づいて不使用のバスを割当てるとともに、バスを割当てたマスタ装置の処理要求に対して処理順位を設定する。コントローラ20は、バスが割当てられたマスタ装置から受けた処理要求の内容と処理順位とに基づいて、スレーブ装置30に対して処理を実行する。

(もっと読む)

11 - 20 / 160

[ Back to top ]