国際特許分類[G06F15/167]の内容

物理学 (1,541,580) | 計算;計数 (381,677) | 電気的デジタルデータ処理 (228,215) | デジタル計算機一般 (4,503) | 各々が少くとも算術演算ユニット,プログラム・ユニットおよびレジスタをもつ2つ以上のデジタル計算機が結合されたもの,例.数個のプログラムの同時処理を行うためのもの (694) | プロセッサ間通信 (496) | 共通メモリ,例.メイルボックス,を用いるもの (160)

国際特許分類[G06F15/167]に分類される特許

21 - 30 / 160

マルチコア・プロセッサ

【課題】共有アクセス対象へのアクセスに関する調停を確実に行うことが可能なマルチコア・プロセッサを提供すること。

【解決手段】複数のプロセッサコアによって読み書き可能なメモリ上に、特定の共有アクセス対象に対するアクセスの内容及び順序を規定するためのメッセージキューが設定され、複数のプロセッサコアは、メッセージキューに対する所定の書き込み制御に応じて自己が実行すべきタスクに含まれる処理のうち特定の共有アクセス対象に対するアクセスを含む処理に関するジョブ情報を排他的にメッセージキューに書き込み、複数のプロセッサコアのうち少なくとも一の特定対象アクセス実行用プロセッサコアは、メッセージキューに書き込まれたジョブ情報に従って特定の共有アクセス対象に対するアクセスを含む処理を実行することを特徴とする、マルチコア・プロセッサ。

(もっと読む)

信号制御装置及び信号制御方法

【課題】2つのCPUがデュアルポートRAMに同じタイミングで読出し又は書込みを行う場合に、データ信号を正しく読出すこと。

【解決手段】信号制御装置4は、第1及び第2のCPUがデュアルポートRAM5に書き込むアドレスの衝突を検出するアドレス衝突検出部14を備える。また、アドレスの衝突が検出された場合に、デュアルポートRAM5に書込みを行う第1又は第2のCPUのいずれかに設けられたバッファメモリに、衝突したアドレスから読出したデータ信号を保存する制御を行う制御部13を備える。また、第1及び第2のCPUの読出し可能状態又は書込み可能状態に応じて、データ信号の読出し元であるレジスタ又はバッファメモリを切替えて、読出し可能状態となるCPUに読出した前記データ信号を出力するマルチプレクサ15a,15bを備える。

(もっと読む)

マルチプロセッサシステムおよびマルチプロセッサシステムのプログラム

【課題】 マルチプロセッサシステムの計算処理の効率を向上させる。

【解決手段】 マルチプロセッサシステムは、第1メモリと、第1メモリに接続され、第1メモリに記憶されたデータを用いて処理を実施する処理部とを有している。処理部は、第2メモリと、データおよび処理の結果である処理データの少なくとも一方を第1メモリと第2メモリとの間で転送するデータ転送を実施する第1プロセッサと、第1メモリと第2メモリとの間でのデータ転送と処理とを切り替え可能に実施する第2プロセッサと、第2メモリに転送されたデータを用いて、処理を実施する第3プロセッサとを有している。

(もっと読む)

関連コンピューティングシステム間でコンピューティングオペレーションの結果を共有するためのシステムおよび方法

関連コンピューティングシステム間でコンピューティングオペレーションの結果を共有するためのコンピュータ実装は、1)ファイルに対してコンピューティングオペレーションを実行する必要があるかを確認する工程、2)ファイルに関連するユニークな識別子を特定する工程、3)ユニークな識別子を使用して関連コンピューティングシステムのグループによって共有される共有ストアにクエリを行うことによって、関連コンピューティングシステムのグループ内の少なくとも1つのコンピューティングシステムがファイルのインスタンスに対してコンピューティングオペレーションを事前に実行したかを判断する工程、および、4)コンピューティングオペレーションを実行する代わりに、共有ストアからコンピューティングオペレーションの結果を取り込む工程を含み得る。さまざまな他の方法、システムおよびコンピュータ可読媒体も開示される。  (もっと読む)

(もっと読む)

SIMDベクトルの同期

プロセッシングデバイス内のデコーダによって、第1記憶ロケーション、第2記憶ロケーション及び第3記憶ロケーションの間の複数のデータ要素に対するベクトル比較/交換オペレーションを規定する単一命令をデコードする段階と、プロセッシングデバイス内の実行ユニットによって実行するために、単一命令を発行する段階と、単一命令の実行に応答して、第1記憶ロケーションからのデータ要素と、第2記憶ロケーションにおける対応するデータ要素とを比較する段階と、一致が存在するかに応じて、第1記憶ロケーションからのデータ要素を、第3記憶ロケーションからの対応するデータ要素で置き換える段階とを実行することによって、ベクトル比較/交換オペレーションが実行される。 (もっと読む)

並列信号処理装置

【課題】データ転送におけるレイテンシーの遅れや、データ転送機構以外の回路の増大を伴うことなく、演算器の並列度を高めても、急激な回路規模の増大を抑えることができるようにする。

【解決手段】演算器1−1〜1−nが、自己が接続されているローカル共有バス2に接続されている共有メモリ3から隣接している他の演算器1の演算結果を読み出して、その演算結果に対する所定の演算処理を実施し、その演算処理の演算結果を上記ローカル共有バス2に接続されている上記共有メモリ3以外の共有メモリ3に書き込むように構成する。

(もっと読む)

情報処理装置

【課題】アクセラレータが使用するローカルメモリに対するデータの入れ替え処理のオーバヘッドを大幅に低減し、アクセラレータによる演算処理を高速化する。

【解決手段】ローカルメモリ5を複数バンク5a〜5cに分割し、各バンクを切り替えて使用し、アクセラレータ3のコンフィギュレーションは変更せずに別のバンクをアクセス可能とする。コンフィギュレーションがプログラムの場合は演算の終了時に、この切り替えのタイミングが発生する。アクセラレータ3の状態を示す機能レジスタにどのバンクをCPUが使用しているかの情報を保持し、使用中であればアクセラレータ3は実行を保留し、使用しなくなり次第割り当てられたバンクで起動する。各バンクはアクセラレータ3の機能レジスタの情報に基づいて演算器と結びつけられる。演算の切れ目でバンクの切り替えを発生させ、演算器と結びつくバンクを別のものに切り替える。

(もっと読む)

複数メモリ特定用途向けデジタル信号プロセッサ

回路基板(210)と、この回路基板上に実装された1又はそれ以上のデジタル信号プロセッサ(100)とを含む集積回路装置(200)を提供する。デジタル信号プロセッサ(100)は、データユニット(120)及び制御ユニット(110)を含み、データユニットは、特定のアプリケーションの少なくとも一部を実行するために特定の数式を実行するように構成された関数コア(124)と、特定のアプリケーションを実行するためのコマンドを制御ユニット及びデータユニットに送信するように構成された1又はそれ以上の命令を記憶する命令メモリ(122)とを含み、制御ユニットは、複数のメモリバンク(130、140)と関数コアの間の、特定のアプリケーションを実行するためのデータの流れを制御するように構成され、複数のメモリバンクは、1又はそれ以上のデジタル信号プロセッサの各々に結合されるとともに、回路基板上に統合された少なくとも2又はそれ以上のローカルメモリバンク(130)を含む。 (もっと読む)

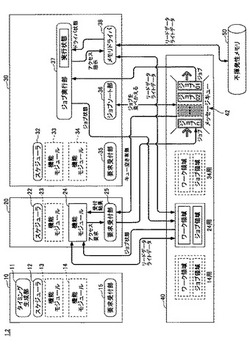

情報処理システム

【課題】データ転送時に発生するデータの書き込み完了通知及びデータの読み出し完了通知を抑制する。

【解決手段】情報処理システム90には、情報処理装置1、情報処理装置2、及び共有部3が設けられる。情報処理システム90では、情報処理装置1及び情報処理装置2の間の共有部3に設けられる共有メモリ31を介して、情報処理装置1と報処理装置2の間のデータ転送を行っている。連続したデータ転送の場合、データ転送が終了後或いは所定回数のデータ転送が終了後に転送データの完了通知が送信される。

(もっと読む)

マルチプロセッサシステム及びメモリアクセス制御方法

【課題】プロセッサエレメントごとにアクセス可能なメモリ領域を設定できるようにすること。

【解決手段】マルチプロセッサシステムは、共有バスを介して互いに接続された複数のプロセッサノードを備え、当該複数のプロセッサノードは、それぞれ、プロセッサエレメントと、当該プロセッサエレメントによる物理メモリに対するアクセスを制御するメモリ管理ユニットとを備えている。

(もっと読む)

21 - 30 / 160

[ Back to top ]