国際特許分類[G06F17/50]の内容

物理学 (1,541,580) | 計算;計数 (381,677) | 電気的デジタルデータ処理 (228,215) | 特定の機能に特に適合したデジタル計算またはデータ処理の装置または方法 (34,028) | 計算機利用設計 (7,589)

国際特許分類[G06F17/50]に分類される特許

1,101 - 1,110 / 7,589

半導体集積回路設計装置、半導体集積回路設計方法及びプログラム

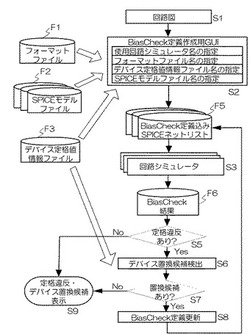

【課題】設計者の負担を軽減しつつ、定格を満たす半導体集積回路を設計できるようにすること。

【解決手段】半導体集積回路設計方法は、コンピュータが、各回路シミュレータのバイアスチェック定義の書式を格納したフォーマットファイルと、各デバイスの定格値情報を格納したデバイス定格値情報ファイルと、各デバイスのモデルの端子情報を格納したモデルファイルを参照し、使用する回路シミュレータに応じたバイアスチェック定義を生成する生成工程と、バイアスチェック定義を含むネットリストを回路シミュレータに入力して、定格違反となるデバイスの有無を検証する検証工程と、定格違反となるデバイスが存在する場合には、該デバイスに対する代替候補を、デバイス定格値情報ファイルに含まれるデバイスの中から抽出する抽出工程と、を含む。

(もっと読む)

タイヤモデル作成方法、及びタイヤモデル作成装置

【課題】複雑な表面形状を有する空気入りタイヤのタイヤモデルを効率的に、かつ精度良く作成する。

【解決手段】細溝10の壁面10aに配置された突起20を有する空気入りタイヤを有限個の要素に分割したタイヤモデルを作成する際、細溝10の壁面10aを含む基本ブロックモデル130を作成するステップ(S11〜S17)と、基本ブロックモデル130に設定された第1要素のサイズと突起の設計値に基づくサイズとを比較するステップ(S182)と、突起の設計値に基づくサイズの最小値が第1要素のサイズよりも小さいとき、突起を第1要素に不連続な別の第2要素に分割した突起モデルを作成するステップ(S184)と、基本ブロックモデル130と突起モデルとを結合させる処理を実行するステップとを実行することにより、細溝10の壁面10aに突起20を有する空気入りタイヤのモデルを作成する。

(もっと読む)

電磁場シミュレーション方法、電磁場シミュレーション装置、半導体装置の製造方法

【課題】計算時間を短縮できる電磁場シミュレーション方法、電磁場シミュレーション装置、半導体装置の製造方法を提供する。

【解決手段】電磁場シミュレーション方法は、電磁波が伝播する媒質に基づいて与えられた計算領域に第1のメッシュを設定する工程と、第1のメッシュ上に割り当てられた媒質の特性値に基づいて、周波数領域解法により第1のメッシュ上での電磁場分布を算出する工程と、計算領域に第2のメッシュを設定する工程と、周波数領域解法により得た電磁場分布を、第2のメッシュに割り当てる工程と、第2のメッシュに割り当てた電磁場分布を、時間領域解法により所定の時間単位で更新する工程と、を備えた。

(もっと読む)

基板の配線設計方法及びプログラム

【課題】配線設計において、簡易的に配線混雑を回避することが可能な配線設計方法を提供することを目的とする。

【解決手段】複数の第1方向配線の配線層及び複数の第2方向配線の配線層を備える基板対して概略配線を行い、基板を複数のタイルに分割し、複数のタイルに対応するように、複数の第1方向配線の配線層及び複数の第2方向配線の配線層を分割して、複数の第1方向配線の部分配線領域と、複数の第2方向配線の部分配線領域と、を形成し、タイルにおける第1方向配線がオーバーフローしている場合には、このタイルに対応する第2方向配線の部分配線領域を、第1方向配線の部分配線領域に変更する。

(もっと読む)

チェックリスト自動生成装置、チェックリスト自動生成方法およびチェックリスト自動生成プログラム

【課題】図面チェック用のチェックリストを自動生成可能なチェックリスト自動生成装置を得ること。

【解決手段】図面上に描画された形状等をそれぞれ1つのオブジェクトとし、オブジェクトごとの描画データを記憶し、各オブジェクトに対してIDおよびオブジェクト種類を付与するCAD図面作成部2と、オブジェクト種類と関連付けて、判定条件およびチェック項目文書を記載したルールを記録するためのチェック項目DB4と、オブジェクトごとにCAD図面作成部2から情報を取得し、チェック項目DB4からオブジェクト種類に該当するルールをすべて抽出し、オブジェクトごとの描画データおよび判定条件に基づいて、オブジェクトごとに当該判定条件に適合するかどうかを判定し、適合すると判定されたルールに記載されたチェック項目文書を用いてチェックリストを生成するチェックリスト生成部3と、を備える。

(もっと読む)

半導体集積回路の検証装置及び検証方法

【課題】設計品質の向上を可能とする。

【解決手段】半導体集積回路を構成する回路の接続関係を示す接続仕様情報と、前記半導体集積回路の構成を記述した回路記述情報との回路接続関係の一致性を検証する半導体集積回路の検証装置であって、前記接続仕様情報をアサーション言語で記述された接続情報ファイルに変換するアサーション生成部と、前記接続仕様情報からオープンである端子を抽出した第1の端子情報と、前記回路記述情報からオープンである端子の情報を抽出した第2の端子情報とに応じて、前記第1の端子情報と第2の端子情報の一致性を比較する比較部と、前記接続情報ファイルと前記回路記述情報とに応じてフォーマル検証を行うフォーマル検証部と、を有し、前記フォーマル検証部の検証結果と前記比較部の比較結果から、半導体集積回路を構成する回路の接続関係を検証する半導体集積回路の検証装置。

(もっと読む)

半導体装置の電源配線レイアウト方法及び電源配線レイアウト装置

【課題】基板ノイズ違反を解消しつつ、半導体集積回路の大型化を抑制することができる半導体装置の電源配線レイアウト方法。

【解決手段】アナログ回路とデジタル回路とが混載された半導体集積回路の電源配線レイアウト方法。電源配線を、複数のノードと、それぞれが互いに隣接するノード間に配置された複数の要素抵抗と、を含む解析モデルとしてモデル化し、回路シミュレーションにより各複数のノードにおける電圧値を求め、アナログ回路のノードの電圧値に基板ノイズ違反がある場合、デジタル回路のノードのうち当該アナログ回路のノードへ流れ込む電流量が最大となる最大電流ノードを探索し、デジタル回路において最大電流ノードへ流れ込む電流経路を探索し、複数の要素抵抗のうち、電流経路に含まれる要素抵抗からボトルネック要素抵抗を選択し、ボトルネック要素抵抗の抵抗値を変更する。

(もっと読む)

製造を容易にする設計

【課題】製造容易性を改善するために、既存の超小型装置設計を変更する技術を提供する。

【解決手段】これらの技術により、設計者は、設計に於けるデータに関連した製造基準を受領する。次に、関連した設計データが識別されて、超小型装置設計者へ供給され、該設計者は、製造基準に基づいて設計変更を選択することが出来る。このようにして、設計者は、超小型装置の元の設計に於いて、半導体ファンドリからの製造基準を直接的に包含させることが出来る。

(もっと読む)

レイアウト設計装置、レイアウト設計方法、及びレイアウト設計プログラム

【課題】

複数階層を有する半導体集積回路の階層レイアウトを行なう際に、複数個所で使用される下位モジュールについての各配置箇所における下位モジュール近傍の上位階層の配線状況を考慮して、下位モジュールのレイアウト設計を行なうことを課題とする。

【解決手段】

上記課題を解決するために、本発明に係るレイアウト設計装置は、複数階層を有する半導体集積回路のレイアウト設計装置であって、複数個所で使用される下位モジュールについて、前記下位モジュールが配置される上位モジュール内のそれぞれの配置箇所近傍の上位階層の配線情報を抽出し、抽出した上位階層の配線情報を、前記下位モジュールのレイアウト設計を行なう際の配線禁止領域として設定し、前記下位モジュールのレイアウトを行なう。

(もっと読む)

端子割り当て装置及び端子割り当て方法

【課題】容易に各端子に割り付けられる機能が決定できる端子割り当て装置を提供する。

【解決手段】設計対象装置に含まれる端子と、割り当てることが可能な候補機能群との対応関係を示す情報を、端子情報として格納する、端子情報格納部と、前記端子情報に基づいて、前記各端子に割り当てられる機能を決定し、割り当て結果データを生成する処理部とを具備する。前記端子情報において、前記候補機能群に含まれる各候補機能には、前記各候補機能が所属する関連機能グループを示す関連情報が対応付けられている。前記処理部は、前記関連情報を参照して、前記選択機能が所属する関連機能グループを特定関連機能グループとして特定する。前記複数の端子の中から、前記特定関連機能グループに所属する候補機能を有する他の端子が、関連端子として選択される。前記関連端子に、特定関連機能グループに所属する候補機能が割り付けられ、割り当て結果データが生成される。

(もっと読む)

1,101 - 1,110 / 7,589

[ Back to top ]