国際特許分類[G06T1/20]の内容

物理学 (1,541,580) | 計算;計数 (381,677) | イメージデータ処理または発生一般 (58,387) | 汎用イメージデータ処理 (27,485) | プロセッサアーキテクチャ;プロセッサ構成,例.パイプライン (990)

国際特許分類[G06T1/20]の下位に属する分類

ニューラルネットワーク (39)

国際特許分類[G06T1/20]に分類される特許

921 - 930 / 951

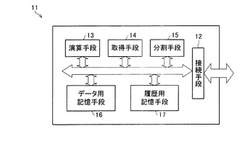

情報処理装置、情報処理方法、情報処理プログラムおよびコンピュータ読み取り可能な記録媒体

【課題】 対象となる処理に対する処理能力の正確な通知無しに、複数のプロセッサの間で処理を分担しあうシステム全体での処理時間を短くする。

【解決手段】 画像処理装置11は、接続した他の画像処理装置の識別結果に基づいて履歴用記憶手段17から過去の処理の結果を取得する取得手段14と、その過去の処理の結果に応じて演算手段13と他の画像処理装置との間で画像処理量を分割する分割手段15とを備えているので、各画像処理装置の処理速度を処理前にユーザーが正確に把握しておくことが困難であっても、また、各画像処理装置の理論的な処理速度とインターフェース等周辺機器の性能も加味した実際の処理速度とのずれをユーザーが把握していなくても、処理にかかる時間を短くすることができる。

(もっと読む)

解像度変換回路及び表示装置

【課題】 解像度変換処理において入力画素毎に異なる使用回数(解像度変換処理に使用される回数または対応する出力画素数)に対応するための記憶手段とその制御手段とを簡略化することを目的とする。

【解決手段】 入力された入力画像を解像度変換して出力画像を出力する解像度変換回路であって、入力画像を記憶する第1の記憶手段と、入力画像及び出力画像の画素数を使用して、出力画像の出力画素毎に、解像度変換処理による出力画素を生成するために必要な入力画像の入力画素を対応付ける入力画素対応付け手段と、を有し、対応付けした入力画素を使用して解像度変換処理を行う。

(もっと読む)

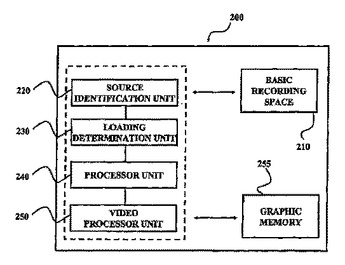

イメージリソースをローディングする方法及びイメージリソースローディングシステム

本発明は、特定のセルに対するレンダリング処理イベントが発生する場合、所定の基本記録空間から前記セルと連関したソースデータを識別する段階と、前記識別されたソースデータを構成する単位ソースデータを、所定周期間隔で、第1ローディングキューに順次移動させる段階と、前記第1ローディングキューに位置した前記単位ソースデータに対して、所定の判断基準によってローディングの適合度を判断する段階と、判断の結果、前記ローディングの適合度がノンパスの場合、前記単位ソースデータを第2ローディングキューに移動させる段階と、判断の結果、前記ローディングの適合度がパスの場合、前記プロセッサ手段は、前記第1ローディングキューに位置した前記単位ソースデータを所定のグラフィックメモリにローディングさせる段階と、所定のビデオプロセッサ手段において、前記グラフィックメモリにローディングされた前記単位ソースデータをレンダリングする段階と、を含み、前記ローディングの適合度を判断する前記段階は、前記プロセッサ手段のローディング処理の能力、または前記ビデオプロセッサ手段のレンダリング処理の能力を考慮して、前記ローディングの適合度を判断することを特徴とするイメージリソースをローディング方法及びイメージリソースをローディングシステムを開示する。  (もっと読む)

(もっと読む)

画像処理装置及びロボット装置ならびに車両誘導装置

【課題】

画像処理装置において、広い範囲にある対象物に対して、屋外や強い照明下においても安定して形状復元する。

【解決手段】

画像処理装置において、画像入力手段1aが時系列的に入力した画像上の特徴的な点の位置関係の変化を第1の計算手段1bが抽出する。位置関係の変化から特徴的な点の三次元位置と画像を捉えた際の視点の位置と方向を第2の計算手段1cが計算する。入力した画像と特徴的な点の三次元位置とから画像に捉えられている物体の三次元形状データを第3の計算手段が計算する。

(もっと読む)

ビデオ処理のための階層的プロセッサ構造

システムはメモリ、いくつかの低レベルプロセッサおよび制御プロセッサを含みうる。メモリは指標データ、該指標データによって記述される他のデータおよび命令を保存しうる。低レベルプロセッサは前記他のデータを前記命令に基づいて処理しうる。制御プロセッサは前記指標データから前記他のデータを処理するのに必要とされる命令のサブセットを決定しうる。制御プロセッサはまた、命令のサブセットが前記いくつかの低レベルプロセッサにロードされるようにしうる。  (もっと読む)

(もっと読む)

低電力プログラマブルプロセッサ

本グラフィックスプロセッサは、画素パケットを処理するためのスカラ算術演算を行うことのできるプログラマブル算術論理演算装置(ALU)段を有する。画素パケット内のオペランドは、ダイナミックレンジを改善するためにS1.8形式でフォーマット設定されてもよく、異なるデータ形式でフォーマット設定されてもよい。グラフィックスプロセッサは、構成可能なグラフィックスパイプラインとして実施されてもよい。一実装形態では、パイプラインを通る画素パケットのプロセスフローが、ホストからのコマンドに応答して再構成され得るようにするために、分配器がグラフィックスパイプラインの要素を結合する。各画素は、偶数画素または奇数画素に割り当てられ、次いで、奇数と偶数の画素の画素パケットがALU待ち時間を引き受けるようにインターリーブされてもよい。 (もっと読む)

SIMDアレープロセッサ用のビットシリアル処理要素

画像処理システムにおいては、画素データについての計算を、ビットシリアル処理要素(PE)のアレーにより実行できる。該アレーを構成するPEの密度を最大にするために、ビットシリアルPEは、最小のロジックにて実現される。より少ないクロックサイクルで演算を実行できるようにするために、PEのアーキテクチャーの改良が行われる。その際、改良に必要な追加のロジックを最小にするよう注意が払われる。アレーにおけるPEの密度を最高にする一方、PEのビットシリアルの性質もまた維持される。ここに記載したPEの改良は、差分絶対値和(SAD)演算、除算、乗算、及び変換(例えばFFT)シャッフル工程の性能の改善、強化を含む。 (もっと読む)

画像処理装置及び方法

画像処理装置及び方法は、画像フレームで例えば線分などの関心領域22aを識別する。望ましくは、関心領域は、最適合境界ボックス23aを決定するために使用される進路境界ボックス21aの範囲内に定められる。次に、最適合境界ボックス23aは直交グリッド25aへ再走査される。従って、線分22aは、2次元配列によって表され、線分22aの全長は第1の次元にあり、線分22aの左側及び/又は右側の画素データは2次元にある。次に、直交グリッド25aは、例えばラインデータの補間、増強、エッジ検出といった画素並列処理のために、SIMD処理装置26によって処理される。線分22aは、その全長が1つの次元で検出されるように再走査されたので、画像データは、SIMD処理装置26によるライン領域に基づく処理により適する。望ましくは、第1の次元は画像内の行に対応し、第2の次元は画像内の列に対応する。画素データがSIMD処理装置により処理されると、再走査動作中に記憶された走査情報は、画像データを元の画像フレームへと逆に走査するために使用される。  (もっと読む)

(もっと読む)

グラフィックオペレーションのための高レベルプログラムインターフェース

アプリケーションプログラムインターフェースを含むイメージを生成するためのシステムが開示される。本システムは、フィルタとイメージとの間の関係を定義することによって、イメージを生成するためのAPI及び技術を含み、このような関係は、要求しているアプリケーションとグラフィックサービス資源との間の協働セッションによってプログラム的にオブジェクトで組み立てられる。本システムはまた、プログラム的に組み立てられたオブジェクトの最適化とマルチプロセッサ環境でのレンダリングのための技術とに関する態様を含む。 (もっと読む)

コンピューティングデバイスのための相互交換可能なグラフィックカード

コンピューティングデバイスのためのフィールドチェンジアブル(その場で交換可能)なグラフィックシステムの一実施形態は、グラフィックカードとインタフェースアセンブリとを含む。インタフェースアセンブリは、グラフィックカードをコンピューティングデバイスのマザーボードに直接取り付けることなく、グラフィックカードをマザーボードに接続するようにされている。開示したグラフィックシステムの1つの利点は、このグラフィックシステムによって、コンピューティングデバイスのユーザが既存のデバイスのグラフィックシステムをアップグレードできることである。従って、ユーザはグラフィックの新しい技術を利用するために新しいコンピューティングデバイス全体を購入する必要はない。この利点は、携帯型のコンピューティングデバイス(ラップトップコンピュータ、携帯情報端末)のユーザにとって大きい。 (もっと読む)

921 - 930 / 951

[ Back to top ]