国際特許分類[G09G3/36]の内容

物理学 (1,541,580) | 教育;暗号方法;表示;広告;シール (131,780) | 静的手段を用いて可変情報を表示する表示装置の制御のための装置または回路 (71,488) | 陰極線管以外の可視的表示器にのみ関連した,制御装置または回路 (45,667) | マトリックス状に配置された個々の要素の組み合わせによりその集合を構成することによって多数の文字の集合,例.1頁,を表示するためのもの (44,823) | 独立の光源よりの光の制御によるもの (16,353) | 液晶を用いるもの (11,628)

国際特許分類[G09G3/36]に分類される特許

41 - 50 / 11,628

電力供給装置、液晶モジュールおよび電力供給装置の制御方法

【課題】液晶モジュールの内部回路の温度上昇を抑制すると共に、表示品質を維持しつつ、液晶モジュールのコストを低減する。

【解決手段】液晶モジュール1におけるソースドライバ3に電力を供給する電力供給装置10において、ソースドライバ3に供給する電流の電流値が所定の検出閾値を超えている場合、ソースドライバ3に供給する出力電圧の電圧値を降下して、ソースドライバ3に電力を供給する。

(もっと読む)

出力回路及びそれを備えた増幅器

【課題】出力波形に付加される遅延の増大を抑制することが可能な出力回路を提供すること。

【解決手段】本発明にかかる出力回路は、高電位側電源端子と外部出力端子Voutとの間に設けられ、電源電圧VDD〜接地電圧VSS間の電圧範囲を振幅する一対の増幅信号の一方に基づいてソース−ドレイン間に流れる電流が制御される出力トランジスタMP11と、低電位側電源端子と外部出力端子Voutとの間に設けられ、一対の増幅信号の他方に基づいてソース−ドレイン間に流れる電流が制御される出力トランジスタMN11と、電源電圧VDDより低く接地電圧VSSより高い中間電圧VMLが供給されている低電位側電源端子と、出力トランジスタMP11のゲートと、の間に設けられ、出力トランジスタMP11のゲート電圧と中間電圧VMLとの電圧差に基づいて出力トランジスタMP11のゲートをクランプするクランプ用トランジスタMP12と、を備える。

(もっと読む)

映像表示装置およびテレビ受信装置

【課題】映像信号の発光している部分を検出し、発光部分の表示輝度をエンハンスして表示させることにより、輝き感をより増して、高いコントラストで映像表現を行う。

【解決手段】発光検出部1は、入力映像信号の明るさに関連する所定の特徴量を用い、映像信号の発光量を特徴量との関係によって予め規定しておき、入力映像信号のフレームごとの特徴量から発光量を検出する。バックライト輝度ストレッチ部3は、検出した発光量に応じてバックライトの光源輝度をストレッチする。映像信号輝度ストレッチ部6は、入力映像信号の発光量もしくは輝度分布に応じて、映像信号をストレッチする。マッピング部7では、非発光部の輝度を低下させて映像信号のマッピングを行う。これにより、発光しているとみなされる入力映像信号の部分が、バックライトの輝度ストレッチと映像信号のストレッチによってエンハンスされる。

(もっと読む)

頭部装着型表示装置および頭部装着型表示装置の制御方法

【課題】頭部装着型表示装置内部におけるデーター送受信の乱れに起因する画像表示の乱れが生じた場合に、使用者に与える不快感を軽減可能な頭部装着型表示装置を提供する。

【解決手段】使用者に虚像を視認させる頭部装着型表示装置は、画像データーを用いて画像を表す画像光を生成し射出させる画像光生成部と、射出された画像光を使用者の眼に導く導光部と、画像データーを受信する受信部と、受信部と接続されると共に、画像光生成部による画像表示を制御する制御部であって、受信部に対して画像データーを送信する送信部を有する制御部とを備える。制御部は、送信部と受信部との間のデーター送受信の乱れが推定される場合に、所定の間、虚像の視認性を低下させるように画像光生成部の輝度を調整する。

(もっと読む)

液晶表示装置

【課題】ジグザグパターンを採用する場合に、製品開発・製造における迅速化および低コスト化に貢献し且つ違和感の無い画像表示を実現する。

【解決手段】液晶セルと、ゲートドライバと、ソースドライバと、ゲートドライバおよびソースドライバによる出力を制御することにより画像表示を実現させる制御部とを備え、第1方向を向く画素列を構成する各画素が、所定画素数毎に、当該画素列を挟む両側のソースラインへ交互に接続する配線パターンを有する液晶表示装置であって、液晶セルにおけるソースラインの総数がソースドライバの出力ラインの総数よりも1本多く、液晶セルにおける最外側のソースラインは近隣のソースラインが接続するソースドライバの出力ラインに対して接続され、上記制御部は上記最も外側のソースラインおよび上記近隣のソースラインが接続する画素列を含む領域に黒表示を実行させる。

(もっと読む)

レジスタ設定装置およびレジスタ設定方法

【課題】任意の同じ値のデータを複数のレジスタに書き込むことができ、かつ、従来よりもレジスタの設定に要する時間を短縮することのできるレジスタ設定装置を実現する。

【解決手段】レジスタ設定部100には、複数のレジスタのうちの2以上の任意の数のレジスタの指定が可能なように構成された書き込み対象指定レジスタ130と、書き込み対象指定レジスタ130で指定されたレジスタに設定されるべき値を保持するための書き込みデータ保持レジスタ120と、書き込みデータ保持レジスタ120に保持されている値を書き込み対象指定レジスタ130で指定された2以上のレジスタに同時に書き込むための書き込み制御部140とが設けられる。

(もっと読む)

階調データ検出装置、電気光学表示装置および電子機器

【課題】回路規模の増大を抑制しつつ、映像データの中から数が多い階調データを検出する。

【解決手段】階調データ検出装置230には、複数ビットの階調データをそれぞれ有する複数の画素を含むデジタル映像が入力される。該装置は、複数の画素が有する複数の階調データにおいて同一ビットの0又は1である特定値の数をビット毎にカウントするカウント部231と、該カウント部によりカウントされた特定値の数が所定数であるか否かを判定する判定部232と、該判定部での判定結果を用いて、複数の階調データからその半数よりも多い数の特定階調データを検出する検出部233とを有する。

(もっと読む)

電気光学表示装置および電子機器

【課題】電気光学表示装置において負荷変動により発生する表示品位の低下を防止する。

【解決手段】表示装置は、1本の走査線135に選択電圧が印加されることに応じて該1本の走査線に対応する画素列に含まれる画素へのデータ線134を介した画素電圧の印加を可能とする複数の画素スイッチング素子136と、複数のデータ線に供給可能なサンプリング用電圧を1本の走査線に選択電圧が印加される期間において単調変化させる電圧生成部300と、順次選択した1本の走査線に選択電圧を印加する走査線駆動回路120およびデータ線へのサンプリング用電圧の供給をオン/オフするデータ線スイッチ133とを有する。同一の画素電圧がサンプリングされた画素の数である同一電圧サンプリング数を検出し、検出された同一電圧サンプリング数が所定数である場合にサンプリングを一時的に停止させ、かつ電圧生成部でのサンプリング用電圧の単調変化を停止させる。

(もっと読む)

液晶表示装置

【課題】DACのためのカウンタクロック周波数を高くすることなく、またコスト増加を抑えた構成により、DACのビット数を増加する。

【解決手段】コンパレータ161は、カウンタ値とデジタル画像データの画素値とが一致した時に一致パルスを出力する。4入力1出力D/S162は、位相が90度ずつ異なる4本のコンパレータクロックCP1〜CP4の中から一つのコンパレータクロックをデジタル画像データの下位2ビットデータの値に基づいて選択する。DFF163は、選択された一本のコンパレータクロックの立ち上がりエッジのタイミングで一致パルスをラッチしてローレベルのゲート信号VSW_GATEをアナログSW164に出力し、これをオフに制御する。これにより、ランプ信号がサンプリングされる。このランプ信号のサンプリングレベルは、デジタル画像データをDA変換して得たアナログ信号電圧に相当する。

(もっと読む)

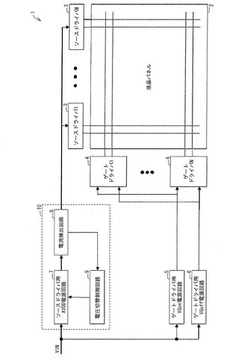

表示装置及びその駆動方法

【課題】各データライングループに割り当てられた電荷充電部を通じて短時間でチャージシェアを行うことができる表示装置及びその駆動方法を提供する。

【解決手段】表示装置は、複数のデータラインを通じて伝達された複数のデータ信号に対応する映像を表示する表示パネル10と、前記複数のデータラインを駆動するデータ駆動部30と、前記データ駆動部の駆動タイミングを制御するタイミングコントローラ40と、前記複数のデータラインのうち、第1データライングループに割り当てられた第1電荷充電部52、及び第2データライングループに割り当てられた第2電荷充電部53を有し、前記タイミングコントローラの制御に応じて、前記第1データライングループ、前記第2データライングループ、前記第1電荷充電部及び前記第2電荷充電部間の充電及び放電動作を選択的に行うチャージシェアリング部50と、を備える。

(もっと読む)

41 - 50 / 11,628

[ Back to top ]