国際特許分類[G11C11/41]の内容

物理学 (1,541,580) | 情報記憶 (112,808) | 静的記憶 (17,688) | 特定の電気的または磁気的記憶素子の使用によって特徴づけられたデジタル記憶装置;そのための記憶素子 (6,432) | 電気的素子を用いるもの (5,515) | 半導体装置を用いるもの (5,114) | トランジスタを用いるもの (5,110) | 正帰還によるセル,すなわちリフレッシングまたは電荷再生を必要としないセルを形成するもの,例.双安定マルチバイブレータまたはシュミットトリガ (1,516)

国際特許分類[G11C11/41]の下位に属する分類

バイポーラトランジスタのみを用いるもの

電界効果トランジスタのみを用いるもの (157)

周辺回路,例.アドレシング,復号化,駆動,書込み,検知,同期および低電力化用 (887)

国際特許分類[G11C11/41]に分類される特許

1 - 10 / 472

半導体メモリおよびシステム

Notice: Undefined index: from_cache in /mnt/www/gzt_ipc_list.php on line 285

半導体記憶装置

【課題】1つの実施形態は、例えば、電源オフ時における消費電力を低減することを目的とする。

【解決手段】1つの実施形態によれば、メモリセルは、第1の駆動トランジスタと第1の負荷トランジスタと第1の読み出し転送トランジスタと第1の書き込み転送トランジスタと第2の駆動トランジスタと第2の負荷トランジスタと第2の読み出し転送トランジスタと第2の書き込み転送トランジスタと1以上の抵抗変化素子とを有する。1以上の抵抗変化素子は、両端に印加されるバイアスの方向に依存して抵抗が変化する。1以上の抵抗変化素子は、第1の記憶ノード及び第1の書き込み転送トランジスタの間と第2の記憶ノード及び第2の書き込み転送トランジスタの間との少なくとも一方に配される。

(もっと読む)

半導体記憶装置

【課題】不揮発性メモリ部内蔵のSRAMの特性の向上を図る。

【解決手段】SRAMを構成するアクセストランジスタAcc1とビット線BLとの間に抵抗変化層Rを有するReRAM部RM1を設け、アクセストランジスタAcc2とビット線/BLとの間に抵抗変化層Rを有するReRAM部RM2を設ける。SRAM通常動作期間の終了時において、例えば、蓄積ノードAに低電位(L=0V)、蓄積ノードBに高電位(H=1.5V)が保持されている場合、ReRAM部RM1をオン状態(ON)とし、ReRAM部RM2をオフ状態(OFF)とすることで、SRAMの保持データをReRAM部へ書き込み、再び、SRAM通常動作となった場合には、蓄積ノードAおよびBに対応するデータ書き戻すとともに、ReRAM部RM1、RM2の双方をオン状態に(リセット)する。

(もっと読む)

半導体装置

【課題】メモリの大容量化と図りつつ、消費電力を軽減でき、且つ、消費電力を一定にす

る。

【解決手段】メモリを、複数のメモリブロックを対称に配置して構成する。また、メモリ

に供給されるアドレス信号のうち、特定の信号の組み合わせにより、データ読み出しまた

は書き込みの対象となるメモリセルを含むメモリブロックを一意に特定する。さらに、当

該メモリブロック以外のメモリブロックに供給される信号を一定値に保つ。このようにす

ることで、メモリアレイにおけるビット線の配線長を短縮し、負荷容量を軽減すると同時

に、メモリ内のあらゆるアドレスのメモリセルに対するデータ読み出しもしくは書き込み

において、消費電流を一定にできる。

(もっと読む)

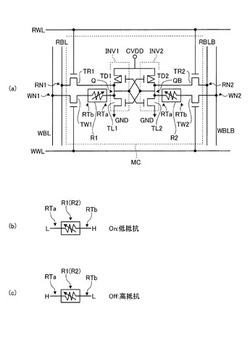

SRAMおよびその制御方法

【課題】

断熱的SRAM回路の回路構造と制御方法を改良し、さらなる低消費電力化を実現するためのSRAM回路を提供すること。

【解決手段】

従来の断熱的SRAMで記憶保持として用いられているインバータからなるフリップフロップ回路を抵抗負荷型のMOSトランジスタに置き換え、かつ読み込み・書き込み選択線の切り替えにCMOSトランスミッションゲートを配置することで、書き込み時における消費電力の増加を解決できる。

(もっと読む)

半導体記憶装置

【課題】SRAMの書き込み時間の増大を抑制しつつ、ライトマージンを増大させる。

【解決手段】メモリセルMCは、相補的にデータを記憶する1対の記憶ノードが設けられている。1対のビット線blt_0〜blt_k、blc_0〜blc_kは、メモリセルMCに書き込まれるデータに基づいて相補的に駆動される。ワード線wl_0〜wl_mは、メモリセルMCのロウ選択を行う。セル電源制御回路3は、メモリセルMCへのデータの書き込み時にビット線線blt_0〜blt_k、blc_0〜blc_kの電位に基づいて記憶ノードに供給されるセル電源を遮断する。

(もっと読む)

記憶回路

【課題】回路構成の自由度を広げた記憶回路と記憶回路に適したセンスアンプを提供する。

【解決手段】p型の第1のMOSFETP10と第2のMOSFETP9からなり、第1のMOSFETP10はソースが電源電圧VDDに接続され、このゲートに複数のメモリセルの一方のトランスファートランジスタN3からの読み出し信号を共通に入力し、このドレインと第2のビット線BLとを第2のMOSFETP9を介して接続する読み出し回路を備え、データの読み出し時に第1のビット線BLiおよび第2のビット線BLを予め所定の電圧VP2,VP1にプリチャージしておき、第2のMOSFETP9をONとしたときの第2のビット線BLの電圧降下をセンスアンプ10で検出することによりデータを読み出す。

(もっと読む)

半導体記憶装置

【課題】TFTなどのトランジスタ特性がばらつく状況や、RF回路から電源が供給され

電源が安定しない状況で、SRAMを作製する場合、従来の1つのメモリセルに6つのト

ランジスタの構成では読み出し時にメモリセルが保持する値が書き換わる誤書き込みが発

生してしまう。

【解決手段】SRAMのメモリセルは、書き込みの回路と読み出しの回路を分離する事に

より、SRAMの誤書き込みを防ぎ、安定した動作を行うことを可能にする。また、書き

込みのタイミングを考慮する事により、誤書き込みを起こさず、より確実に書き込みの動

作を行うことが可能なSRAMを提供する。

(もっと読む)

半導体記憶装置及び半導体記憶装置の制御方法

【課題】データを確実に書き込むこと。

【解決手段】メモリセルC00に接続されたAポート用のビット線対BL0a,XBL0a間にはアシスト線AL0aが形成されている。ライトアンプはライトデータとライトコントロール信号に基づいて、ビット線BL0aと反転ビット線BL0aの電位を制御する。そして、ライトアンプは、HレベルからLレベルに遷移させた反転ビット線XBL0aをフローティング状態にする。アシストコントロールは、ライトコントロール信号に基づいて、アシスト線AL0aを、HレベルからLレベルへと急峻に立ち下げる。フローティング状態の反転ビット線XBL0aの電位は、容量結合されたアシスト線AL0aの電位変化により、低電位側の電源電圧VSSレベル(Lレベル)から更に低下する。

(もっと読む)

記憶装置及び信号処理回路

【課題】電源の供給を停止しても、記憶している論理状態が消えない記憶装置を提供する。また、該記憶装置を用いることで、電源供給停止により消費電力を抑えることができる信号処理回路を提供する。

【解決手段】第1乃至第4のノードを有する論理回路と、第1のノード、第2のノード、及び第3のノードと接続された第1の制御回路と、第1のノード、第2のノード、及び第4のノードと接続された第2の制御回路と、第1のノード、第1の制御回路、及び第2の制御回路に接続された第1の記憶回路と、第2のノード、第1の制御回路、及び第2の制御回路に接続された第2の記憶回路と、を有する記憶装置である。

(もっと読む)

1 - 10 / 472

[ Back to top ]