国際特許分類[H01L21/02]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 半導体装置またはその部品の製造または処理 (125,986)

国際特許分類[H01L21/02]の下位に属する分類

その後のフォトリソグラフィック工程のために半導体本体にマスクするもので,グループ21/18または21/34に分類されないもの (23,597)

少なくとも一つの電位障壁または表面障壁,例.PN接合,空乏層,キャリア集中層,を有する装置 (97,574)

電位障壁または表面障壁をもたない装置

国際特許分類[H01L21/02]に分類される特許

951 - 960 / 4,815

半導体装置の作製方法

【課題】半導体膜への不純物の拡散を抑えつつ、歩留まりの低下を抑えることができるSOI基板の作製方法を提供することを、目的の一とする。

【解決手段】半導体基板の表面を熱酸化させることで、酸化膜が形成された半導体基板を形成する。そして、窒素原子を有するガス雰囲気下においてプラズマを発生させることにより、上記酸化膜の一部をプラズマ窒化させ、酸化膜上に窒素原子を含む絶縁膜が形成された半導体基板を得る。そして、窒素原子を含む絶縁膜とガラス基板を接合させた後、半導体基板を分離することで、ガラス基板上に窒素原子を含む絶縁膜、酸化膜、薄膜の半導体膜が順に積層されたSOI基板を形成する。

(もっと読む)

貼合せSOIウェーハ及びその製造方法

【課題】厚さが数μm〜数百μmであって、テラスフリーでかつデバイス形成面積が広いSOI層を有し、通常の表裏対称なウェーハと同様の取扱いが可能な、貼合せSOIウェーハ及びその製造方法を提供する。

【解決手段】支持用ウェーハの上に埋込み酸化膜を介してSOI層が形成された貼合せSOIウェーハにおいて、SOI層の端面及び支持用ウェーハの端面が断面方向に連続したラウンド端面又はテーパ付き端面に形成され、支持用ウェーハの裏面に酸化膜を有し、かつSOI層の端面及び支持用ウェーハの端面がそれぞれ加工歪みを有さず、それぞれの端面の表面粗さRaが0.1μm以下であることを特徴とする。

(もっと読む)

基板処理装置

【課題】工程管理を正しく行うためのレシピ処理時間を正確に予測することができる基板処理装置を提供する。

【解決手段】複数のステップにより構成されるレシピを実行することで、基板に所定の処理を行う基板処理装置であって、この基板処理装置は、各ステップを終了する時間を満たすまでに所定時間を越えて保持する待機時間を考慮してレシピの終了時刻又は終了までの時間を予測する制御手段を備えた。

(もっと読む)

半導体基板の再生方法、再生半導体基板の作製方法、および、SOI基板の作製方法

【課題】良好な平坦性を有する半導体基板の再生に適した方法を提供することを課題の一つとし、良好な平坦性を有する半導体基板の再生に適した方法を用いて再生半導体基板を作製することを課題の一つとし、当該再生半導体基板を用いてSOI基板を作製することを課題の一つとする。

【解決手段】イオンの照射等により損傷した半導体領域を選択的に除去することが可能な方法を用いて半導体基板の凸部を除去し、さらに、CMP法をはじめとする研磨処理によって、半導体基板の平坦化を行う際に、半導体基板表面に酸化膜を形成することにより、半導体基板の研磨レートを均一にして、一様に研磨処理を行う。または、上記方法を用いて再生半導体基板を作製し、当該再生半導体基板を用いてSOI基板を作製する。

(もっと読む)

炭化珪素基板およびその製造方法

【課題】化学強化以外の方法で炭化珪素基板を強化することや、炭化珪素基板の薄板化の手法を工夫することで、割れやクラックの発生、進展を抑制した炭化珪素基板およびその製造方法を提供する。

【解決手段】基板の表裏主面のうち半導体装置の形成領域に対応する中央部CPの周辺領域部PPと基板側面部SPとを含んで構成される炭化珪素基板WFの外周部に、膨張力発生部EXを形成することで、基板内部に向かうように圧縮応力CSが生じる。このために、基板加工中または、プロセス中に、微小な割れの起点が発生しても、圧縮応力で抑えられて割れが広がらないために、ウエハ割れが発生せず、実質的に基板外周部が強化された構成となる。

(もっと読む)

基板カートリッジ、基板処理装置、基板処理システム、制御装置及び表示素子の製造方法

【課題】基板に異物が付着するのを防ぐことができる基板カートリッジ、基板処理装置、基板処理システム、制御装置及び表示素子の製造方法を提供すること。

【解決手段】基板が出し入れされる開口部を有し、前記開口部を介した前記基板を収容するカートリッジ本体と、前記カートリッジ本体に設けられ、外部接続部に対して着脱可能に接続されるマウント部と、前記マウント部と前記外部接続部との間の接続状態に応じて前記開口部を閉塞する閉塞部とを備える。

(もっと読む)

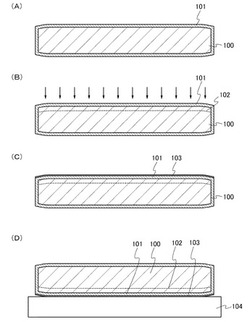

層の貼り合わせおよび転写プロセス

【課題】SOI基板の外周のトリミング残渣が残らない技術を提供する。

【解決手段】レシーバ基板2およびドナー基板1を分子付着により貼り合わせるステップと、貼り合わせ界面5を強固にするために、前述した積層体に熱処理を施すステップと、ドナー基板1を研削により薄化するステップと、ドナー基板1およびレシーバ基板2の一部の環状トリミングを実行するステップと、前述したステップの後、ドナー基板1の残りの部分の露出表面およびレシーバ基板2の露出表面の化学エッチングステップを実行するステップとを含む。

(もっと読む)

半導体基板の製造方法

【課題】SiCを用いた半導体装置を効率よく製造するための半導体基板の製造方法を提供する。

【解決手段】互いに対向する第1の表面F1および第1の裏面B1を有し、かつ単結晶構造を有する第1の炭化珪素基板11と、互いに対向する第2の表面F2および第2の裏面B2を有し、かつ単結晶構造を有する第2の炭化珪素基板12とが準備される。第1および第2の裏面B1、B2の各々が一の方向を向くように第1および第2の炭化珪素基板11、12が配置される。上記配置する工程の後に、第1および第2の裏面B1、B2を互いにつなぐように第1および第2の裏面B1、B2に接合された、炭素を含む接続層30が形成される。

(もっと読む)

基板貼り合せ装置及び半導体装置の製造方法

【課題】基板貼り合せ装置における冷却過程で放出される熱エネルギーを回収する。

【解決手段】複数の基板を加熱して貼り合せる加熱部と、加熱部を冷却する冷却媒体を供給する供給部と、冷却媒体が加熱部で気化した蒸気により発電する蒸気発電機とを備える基板貼り合せ装置が提供される。加熱部は複数設けられ、蒸気発電機には、複数の加熱部からの蒸気が導入される。供給部は、複数の加熱部のうち、温度の低い加熱部から高い加熱部へ冷却媒体を直列的に供給し、蒸気発電機には、温度の高い加熱部からの蒸気が導入される。蒸気発電機で発電された電力を用いて、加熱部が加熱される。

(もっと読む)

半導体装置およびその製造方法

【課題】オン抵抗の低い半導体装置およびその製造方法を提供する。

【解決手段】複数の層を有する半導体層37の第1の面37aに形成されたソース電極12およびゲート取り出し電極14と、第1の面37aと対向する第2の面37bに形成されたドレイン電極16と、ソース電極12上に分散して形成された複数の第1柱状電極13と、ゲート取り出し電極14上に形成された第2柱状電極15と、ドレイン電極16上に分散して形成された複数の第3柱状電極17と、複数の第1柱状電極13の間、および第2柱状電極15と隣接する第1柱状電極13との間を埋めて、ソース電極12、ゲート取り出し電極14、および半導体層37を覆う第1樹脂層18と、複数の第3柱状電極17の間を埋めて、ドレイン電極16を覆い、第1樹脂層18に連接した第2樹脂層19と、を具備する。

(もっと読む)

951 - 960 / 4,815

[ Back to top ]