国際特許分類[H01L21/762]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 1つの共通基板内または上に形成された複数の固体構成部品または集積回路からなる装置またはその特定部品の製造または処理;集積回路装置またはその特定部品の製造 (40,275) | グループ21/70で限定された装置の特定部品の製造 (8,583) | 構成部品間の分離領域の形成 (3,154) | 誘電体領域 (749)

国際特許分類[H01L21/762]に分類される特許

11 - 20 / 749

半導体装置及びその製造方法

【課題】SOI構造のフラッシュメモリーの提供

【解決手段】

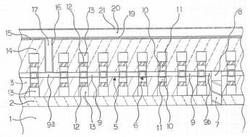

半導体基板1上にシリコン窒化膜2及びシリコン酸化膜3が選択的に設けられ、シリコン酸化膜3上には、選択的に横(水平)方向エピタキシャルSi層5が設けられ、Si層5の両側面には、それぞれ側面を接して横(水平)方向エピタキシャルSi層6が設けられた構造からなる半導体層が素子分離領域のシリコン窒化膜4により絶縁分離されている。Si層6の残りの周囲には第1のゲート酸化膜10を介して包囲型フローティングゲート電極11が設けられ、包囲型フローティングゲート電極11の周囲には第2のゲート酸化膜12を介して包囲型コントロールゲート電極13(ワード線)が設けられ、Si層5には概略ソースドレイン領域9が設けられている2重包囲型ゲート電極を有するMIS電界効果トランジスタより構成したフラッシュメモリー。

(もっと読む)

半導体装置の製造方法

【課題】SOI基板を使用せずバルク基板を用いてフィン型FETを製造すると、従来技術では素子領域と半導体基板との間の絶縁耐圧が低くなっていた。

【解決手段】本発明の半導体装置の製造方法では、素子分離膜の形成時にマスクとして用いる耐酸化用膜を、半導体基板表面に設ける溝部の底部から所定の距離まで離間した部分を除いて立設部の表面に形成することで、立設部の下部の素子分離膜がほぼ一定の膜厚にすることができた。このため、立設部と半導体基板との間の絶縁耐圧が向上し、リークもなく、信頼性が向上した。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】SOIウェハに高耐圧素子の領域と低耐圧素子の領域とが形成された半導体装置であって、製造工程の中で、作業ステージに静電吸着したり、異常放電を引き起こしたりすることを抑えることができる半導体装置を提供する。

【解決手段】半導体層2と、半導体層2の上に形成された絶縁層3と、絶縁層3の上に形成された半導体の第1領域10aと、絶縁層3の上に形成され、第1領域10aに隣接する半導体の第2領域20と、絶縁層3の上に形成され、第1領域10aの側面を覆うように取り囲み、第1領域10aと第2領域20とが直接接続するように開口された開口部31aを有する絶縁体の第1絶縁壁30aとを具備する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】露光光源として真空紫外光を用いるホトリソ技術のパターン解像限界より微細な拡散抵抗を製造することはできないから、高抵抗の拡散抵抗は実現できなかった。

【解決手段】一組の薄膜構造体の対向する間隔に、サイドウォール形成用の絶縁膜を形成する際に生じる空隙を利用して露光光源として真空紫外光を用いるホトリソ技術のパターン解像限界より微細な拡散抵抗を形成する。薄膜構造体を配線抵抗として利用すれば、これらを接続して設けることにより温度特性に優れる抵抗素子を構成することもできる。

(もっと読む)

誘電体分離基板および半導体装置

【課題】深い不純物拡散層の形成が容易な誘電体分離基板および半導体装置を提供する。

【解決手段】誘電体分離基板10では、半導体基板11に第1の厚さt1を有する絶縁膜12が設けられている。絶縁膜12上に第2の厚さt2を有する第1導電型の半導体層13が設けられている。半導体層13の下部に絶縁膜12に接して第2導電型の不純物拡散層14が部分的に設けられている。

(もっと読む)

半導体装置の製造方法、半導体装置、SOI基板の製造方法およびSOI基板

【課題】SOI基板のチャージ蓄積による不良を抑制する。

【解決手段】まず、シード基板100の一面に、シード基板100の表面と同一面を形成するように、開口部220を有する絶縁層200を形成する(絶縁層形成工程)。次いで、シード基板100の一面に接するように、支持基板300を貼り合せる(貼り合せ工程)。次いで、シード基板100または支持基板300の一方を薄板化することにより、当該薄板化基板からなる半導体層120を形成する(半導体層形成工程)。以上の工程により、SOI基板を準備する。次いで、半導体層120に半導体素子60を形成する(半導体素子形成工程)。

(もっと読む)

半導体基板の製造方法及び半導体装置の製造方法

【課題】大面積のアクティブ面積を有するSOI基板を製造する。

【解決手段】Siを含む基板の一つの面の一部の上方に、SiGeを含む第1の層と、Siを含む第2の層とを基板側からこの順に配置する積層部を形成する工程(a)と、積層部の上方と基板の積層部が形成された領域とは異なる領域の上方とにまたがる第3の層を形成する工程(b)と、積層部の上方に位置する第3の層及び第2の層の各一部をエッチングすることにより、第1の層の一部を露出させる工程(c)と、工程(c)において露出した第1の層を、基板の第1の面に沿った方向にエッチングする工程(d)と、工程(c)においてエッチングされた第2の層を、基板の第1の面に沿った方向にエピタキシャル成長させる工程(e)と、積層部が形成された領域の基板と、第2の層との間にSiO2を含む第4の層を形成する工程(f)と、を含む。

(もっと読む)

半導体装置、半導体ウエハ、及びこれらの製造方法

【課題】トランジスタ特性のバラツキが低減された半導体装置を提供する。

【解決手段】SOI基板101は、P型半導体層102の上にN型半導体層104が形成された半導体基板12、その上に形成されたBOX層106、及びBOX層上に形成されたSOI層108を有する。第1素子分離絶縁層110bは、SOI基板101に埋め込まれ、下端16がP型半導体層102に達し、第1素子領域(NFET領域30)と第2素子領域(PFET領域40)とを分離する。P型トランジスタ130bは、第1素子領域40に位置し、チャネル領域120bを有し、N型トランジスタ130aは、NFET領域30に位置し、チャネル領域120aを有する。第1バックゲートコンタクト134bは、第1素子領域40に位置する第2導電型層層104に、第2バックゲートコンタクト134aは、第2素子領域30に位置する第2導電型層104に接続される。

(もっと読む)

半導体基板、その製造方法及び半導体装置

【課題】実施形態は、異なる種類の半導体素子のそれぞれに適合した半導体層が1つの絶縁膜上に設けられた半導体基板、その製造方法及び半導体装置を提供する。

【解決手段】実施形態に係る半導体基板は、第1絶縁層と、前記第1絶縁層の上に設けられた第1半導体層と、前記第1半導体層の上に選択的に設けられた第2絶縁層と、前記第2絶縁層を介して前記第1半導体層の上に設けられた第2半導体層と、を備える。さらに、前記第1半導体層の表面から前記第1絶縁膜に至る深さに延設され、前記第1半導体層における前記第1絶縁層と前記第2絶縁層との間の部分と、前記第1半導体層の残りの部分と、を電気的に分離した第3絶縁層を備える。

(もっと読む)

半導体基板およびその製造方法、その半導体基板を用いた半導体装置

【課題】実施形態は、異なる種類の半導体素子のそれぞれに適合した厚さを有する半導体層が1つの絶縁膜上に設けられた半導体基板およびその製造方法、その半導体基板を用いた半導体装置を提供する。

【解決手段】実施形態に係る半導体基板10は、第1絶縁層5と、前記第1絶縁層の上に設けられた半導体層7とを有する半導体基板であって、前記半導体層の中に選択的に設けられ、前記半導体層の表面に平行に延在し、その延在方向の長さが前記第1絶縁層よりも短い第2絶縁層13と、前記半導体層の表面から前記第1絶縁膜に至る深さに延設され、前記半導体層の前記第2絶縁層を含む部分と、前記半導体層の残りの部分と、を電気的に分離する第3絶縁層15と、を備える。

(もっと読む)

11 - 20 / 749

[ Back to top ]