国際特許分類[H01L21/764]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 1つの共通基板内または上に形成された複数の固体構成部品または集積回路からなる装置またはその特定部品の製造または処理;集積回路装置またはその特定部品の製造 (40,275) | グループ21/70で限定された装置の特定部品の製造 (8,583) | 構成部品間の分離領域の形成 (3,154) | 空隙 (98)

国際特許分類[H01L21/764]に分類される特許

1 - 10 / 98

半導体装置の製造方法

【課題】素子分離用の大きなエアギャップを容易に形成することが可能な半導体装置の製造方法を提供する。

【解決手段】一の実施形態による半導体装置の製造方法では、基板内に素子分離溝を形成し、前記素子分離溝の側壁面にアモルファス層を形成する。さらに、前記方法では、前記素子分離溝内に前記アモルファス層を介して犠牲膜を形成し、前記犠牲膜上にエアギャップ膜を形成する。さらに、前記方法では、前記エアギャップ膜の形成後に前記犠牲膜を除去することで、前記エアギャップ膜の下部の前記素子分離溝内にエアギャップを形成する。

(もっと読む)

高電子移動度トランジスタ及びその製造方法

【課題】高電子移動度トランジスタ及びその製造方法を提供する。

【解決手段】高電子移動度トランジスタ(HEMT)及びその製造方法に係り、該高電子移動度トランジスタは、基板と、基板から離隔された位置に備わった高電子移動度トランジスタ積層物と、基板と高電子移動度トランジスタ積層物との間に位置した疑似絶縁層と、を含み、該疑似絶縁層は、異なる相の少なくとも2つの物質を含む。前記異なる相の少なくとも2つの物質は、固体物質と非固体物質とを含む。前記固体物質は、半導体物質であり、前記非固体物質は、空気である。

(もっと読む)

半導体装置及びその製造方法

【課題】 対象セルのワード線に隣接するワード線の電位の影響に伴う対象セルのビット線への電界を緩和する。

【解決手段】 半導体基板100に形成され、半導体素子101を形成するための活性領域と、半導体基板100内に形成され、活性領域を分離するための素子分離領域(STI102、NF104)と、素子分離領域(STI102、NF104)内に設けられた空洞部105を有する半導体装置。

(もっと読む)

半導体装置

【課題】ブートストラップ方式のドライブ回路を有する半導体装置において、ブートストラップダイオードの順バイアス時にp-基板側に流れるホールによるリーク電流を抑制することができる半導体装置を提供することにある。

【解決手段】ブートストラップダイオードDb下にSON構造の空洞3を形成し、ブートストラップダイオードDbとグランド電位(GND)となるGNDp領域4との間のn-エピ層2にその空洞3に達するフローティングp領域5を形成することで、外部のブートストラップコンデンサC1充電時のp-基板1へのホールによるリーク電流を抑えることができる。

(もっと読む)

半導体基板または半導体装置の製造方法

【課題】平板状空洞を形成する際におけるホール半径Rと、ホールとホールの最短距離Sのプロセスマージンを広げ、信頼性の高い半導体装置の製造方法を提供すること。

【解決手段】半導体基板1の表面にホール4を複数形成し、非酸化性雰囲気のアニール処理により、該半導体基板1の表面を半導体の表面マイグレーションを利用して平坦化し、基板内部に平板状空洞6を形成する際に、前記ホール4の開口部が閉じる前に半導体のソースガスを供給する。

(もっと読む)

半導体装置およびその製造方法

【課題】 本発明は、より寄生容量の少ない素子の実現が可能な素子分離構造を有する半導体装置およびその製造方法を提供することにある。

【解決手段】 SOI基板上に形成される半導体装置は、素子分離領域に形成される素子分離溝(空洞)17と、半導体層11と支持基板13の間に介在する埋め込み絶縁層の一部に素子分離溝(空洞)17に接する空洞領域20を有する。

【効果】寄生容量を低減でき、また、素子の耐圧を高めることができる。

(もっと読む)

半導体装置の製造方法

【課題】SON構造の半導体装置において、フォトリソグラフィー工程で高精度の位置合わせができ、プロセスラインの汚染を防止することができて、素子特性の劣化が防止され、信頼性の高い半導体装置の製造方法を提供する。

【解決手段】SON構造9上部のシリコン層32の段差18をアライメントマーク20として用いることによって、アライメントマーク20の形状崩れが防止されて、フォトリソグラフィー工程で高精度の位置合わせができるようになる。また、段差18が小さいためにフォトリソグラフィー工程で凹部へのレジストの残留やプロセス途中で発生するゴミの残留が防止され、プロセスラインの汚染が防止できる。その結果、素子特性の劣化が防止され、信頼性の高い半導体装置の製造方法を提供することができる。

(もっと読む)

不揮発性半導体記憶装置および不揮発性半導体記憶装置の製造方法

【課題】隣接する浮遊ゲート電極間の間隔を増大させることなく、隣接する浮遊ゲート電極間の寄生容量を低減する。

【解決手段】空隙AG1の埋め込み絶縁膜4が除去される前に側壁保護膜3´にてトンネル絶縁膜5の側壁を覆うことにより、埋め込み絶縁膜4とトンネル絶縁膜5との間でウェット処理のエッチング選択比が確保できない場合においても、トンネル絶縁膜5を保護できるようにする。

(もっと読む)

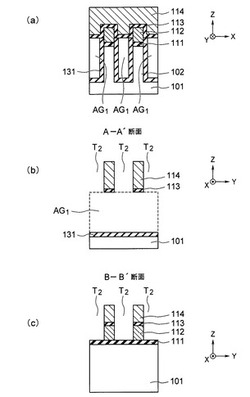

不揮発性半導体記憶装置および不揮発性半導体記憶装置の製造方法

【課題】隣接する浮遊ゲート電極間の間隔を増大させることなく、隣接する浮遊ゲート電極間の寄生容量を低減する。

【解決手段】電極間絶縁膜7下において、埋め込み絶縁膜9が上下に分離されることで、ワード線方向DWに隣接する浮遊ゲート電極6間に空隙AG1が形成され、空隙AG1にて分離された上側の埋め込み絶縁膜9は電極間絶縁膜7下に積層し、下側の埋め込み絶縁膜9はトレンチ2内に配置する。

(もっと読む)

不揮発性半導体記憶装置および不揮発性半導体記憶装置の製造方法

【課題】隣接する浮遊ゲート電極間の間隔を増大させることなく、隣接する浮遊ゲート電極間の寄生容量を低減する。

【解決手段】トレンチ2内に埋め込まれた第2の埋め込み絶縁膜4の一部が除去されることで、ワード線方向DWに隣接する浮遊ゲート電極6間に空隙AG1が形成され、浮遊ゲート電極6間が完全に埋め込まれないようにして制御ゲート電極8間にカバー絶縁膜10が掛け渡されることで、ビット線方向にDBに隣接する浮遊ゲート電極6間に空隙AG2が形成されている。

(もっと読む)

1 - 10 / 98

[ Back to top ]