国際特許分類[H01L21/8246]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 1つの共通基板内または上に形成された複数の固体構成部品または集積回路からなる装置またはその特定部品の製造または処理;集積回路装置またはその特定部品の製造 (40,275) | 1つの共通基板内または上に形成される複数の固体構成部品または集積回路からなる装置の製造または処理 (31,691) | 複数の別個の装置に基板を分割することによるもの (31,691) | それぞれが複数の構成部品からなる装置,例.集積回路の製造 (31,684) | 基板がシリコン技術を用いる半導体であるもの (27,844) | 電界効果技術 (17,660) | MIS技術 (17,448) | メモリ構造 (10,964) | リードオンリーメモリ構造 (7,638)

国際特許分類[H01L21/8246]の下位に属する分類

電気的にプログラムできるもの (4,399)

国際特許分類[H01L21/8246]に分類される特許

171 - 180 / 3,239

磁気スタックおよびこのようなスタックを備えたメモリセル

【課題】磁気スタックおよびこのようなスタックを備えたメモリセルを提供すること。

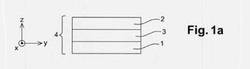

【解決手段】本発明は、平面外磁化を有する磁気スタック(4)に関し、前記スタックは、

−コバルト、鉄およびニッケル、ならびにこれらの材料をベースとする磁気合金の群から選択される1つまたは複数の材料で構成された第1の磁気層(1)と、

−第1の層の材料と共有界面を形成すると界面起源の垂直異方性を与えることができる金属材料で構成された第2の層(2)と

を備え、スタック(4)は、第1の層(1)の上に堆積した第3の層(3)をさらに備え、第2の層(2)が第3の層(3)の上に堆積し、第3の層(3)が、第1の層の材料との10%未満の混和性を有する金属材料で構成されていることを特徴としている。

(もっと読む)

磁気抵抗効果素子およびその製造方法

【課題】安定して動作可能な磁気抵抗効果素子およびその製造方法を提供する。

【解決手段】実施形態の磁気抵抗効果は、下部電極と、第1の磁性層と、第1の金属層と、第1の界面磁性層と、非磁性層と、第2の界面磁性層と、第2の金属層と、第2の磁性層と、上部電極層と、を持つ。前記第1の磁性層は、前記下部電極上に設けられて第1の金属原子を含む。前記第1の金属層は、前記第1の磁性層上に設けられて前記第1の金属原子を含む。前記第1の界面磁性層は、前記第1の金属層上に設けられる。前記非磁性層は、前記第1の界面磁性層上に設けられる。前記第2の界面磁性層は、前記非磁性層上に設けられる。前記第2の金属層は、前記第2の界面磁性層上に設けられ、第2の金属原子を含む。前記第2の磁性層は、前記第2の金属層上に設けられ、前記第2の金属原子を含む。前記上部電極層は、前記第2の磁性層上に設けられる。前記第1の界面磁性層は、前記非磁性層側と反対側の界面にアモルファス金属層を含む。

(もっと読む)

磁気記録素子及び磁気メモリ

【課題】磁気記録素子のMR比の向上を図る。

【解決手段】実施形態に係わる磁気記録素子は、磁化が可変で磁化容易軸方向が膜面に垂直となる方向の磁気記録層11と、磁化が膜面に垂直となる方向に固定される磁気固着層12と、磁気記録層11と磁気固着層12との間の非磁性バリア層13と、磁気記録層11と非磁性バリア層13との間の挿入層14とを備える。挿入層14は、軟磁性材料、ホイスラー合金、ハーフメタル酸化物、及び、ハーフメタル窒化物のうちの1つを含む。

(もっと読む)

半導体記憶装置

【課題】安定した特性の磁気抵抗効果素子を有する半導体記憶装置を提供する。

【解決手段】本発明の実施形態にかかる半導体記憶装置は、複数の磁気抵抗効果素子を有し、この各磁気抵抗効果素子は、半導体基板上に形成され、且つ、その膜面に対して垂直な磁化容易軸を有する第1の磁性層と、第1の磁性層上に形成された非磁性層と、非磁性層上に形成され、且つ、その膜面に対して垂直な磁化容易軸を有する第2の磁性層と、からなる積層構造を有し、保護膜を介して各磁気抵抗効果素子の側壁を覆うように設けられ、且つ、磁気抵抗効果素子に対して、磁化容易軸に沿った方向に引張応力を与える側壁膜を備え、側壁膜のうちの第1の磁性層を覆う部分は、側壁膜のうちの第2の磁性層を覆う部分と比べて厚い。

(もっと読む)

半導体記憶装置

【課題】、半導体記憶装置自身に、適切に自半導体記憶装置に関する装置情報を記憶することができる、半導体記憶装置を提供する。

【解決手段】特定ワード線(1024番目のワード線)上のステータスレジスタ42が設けられていない領域である、8番目〜255番目のビット線と交差する領域に設けられている強誘電体メモリにより生産履歴記憶容量44を構成し、生産履歴記憶容量44に、半導体記憶装置10(半導体チップ20)の生産履歴に関する情報を記憶させている。また、生産履歴記憶容量44への記憶・参照は、主記憶容量40への記憶・参照に使用される通常のコマンドと異なる特殊なコマンドが用いられる。

(もっと読む)

半導体記憶装置

【課題】磁気抵抗効果素子間の磁気的な干渉作用を遮断し、安定した動作を可能にし、且つ、容易に製造することができる半導体記憶装置を提供する。

【解決手段】本発明の実施形態にかかる半導体記憶装置は、半導体基板上にマトリックス状に配列した複数の磁気抵抗効果素子を有し、各磁気抵抗効果素子は、半導体基板上に形成された第1の磁性層と、第1の磁性層上に形成された非磁性層と、非磁性層上に形成された第2の磁性層とからなる積層構造を有し、隣り合う各磁気抵抗効果素子の間には、金属、又は、磁性体材料が分散された絶縁膜が埋め込まれている。

(もっと読む)

磁気抵抗素子及び磁気記憶装置

【課題】書き込み電流を低減させたまま、リテンション、特に固定磁化層の大きなリテンションを十分に確保することができ、熱的に安定な動作を可能とする信頼性の高い磁気抵抗素子を実現する。

【解決手段】MTJ10は、下部磁性層1と上部磁性層3とでトンネルバリア層2を挟持し、上部磁性層3上にキャップ層4が形成されてなり、下部磁性層1は、トンネルバリア層2と接するCoFeBからなる第1自由層1aと、第1自由層1aに接するTaからなる挿入層1bと、挿入層1bに接するRuからなるスペーサ層1cと、スペーサ層1cに接するCoPtからなる第2自由層1dとを有して構成される。

(もっと読む)

セルの配置構造、半導体集積回路、及び回路素子セルの配置方法

【課題】セルベース設計において複数の記憶素子セルが配置される構成において、効率的に且つ確実に複数ビットのソフトエラーの発生を抑制することが可能なセルの配置構造を提供する。

【解決手段】回路素子セルの配置構造は、第1の方向に延展するセル配置列上に並べられた複数の記憶素子セルと、複数の記憶素子セルの各々の領域において第1の方向に垂直な第2の方向に並べられた第1のNウェル及び第1のPウェルと、複数の記憶素子セルのうち少なくとも2つの互いに隣接する記憶素子セルの間に設けられ、セル配置列の幅に亘る長さを各々が有する第2のNウェル及び第2のPウェルとを含み、第1のNウェルと第2のNウェルとは一体であり、第1のPウェルと第2のPウェルとは一体である。

(もっと読む)

ニッケル酸ランタン膜形成用組成物の製造方法、ニッケル酸ランタン膜の製造方法、及び圧電素子の製造方法

【課題】特殊な環境が不要で短時間且つ低コストでニッケル酸ランタン膜形成用組成物を製造することができるニッケル酸ランタン膜形成用組成物の製造方法、ニッケル酸ランタン膜の製造方法、及び圧電素子の製造方法を提供する。

【解決手段】圧電素子300(アクチュエーター)は、絶縁体膜55上に、第1電極60と、第1電極60の上方に設けられて厚さが3μm以下、好ましくは0.3〜1.5μmの薄膜である圧電体層70と、圧電体層70の上方に設けられた第2電極80とが、積層形成される。圧電膜70であるニッケル酸ランタン膜形成用組成物は、ランタンアセチルアセトナート、ニッケルアセチルアセトナート、酢酸、及び水を混合して混合溶液を得た後、混合溶液を加熱する。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造において基板の金属汚染を抑える。

【解決手段】半導体素子が設けられた基板の、半導体素子形成面とは反対側の裏面および端部に保護膜を形成する工程と、前記半導体素子形成面に設けられた金属含有膜を加工する工程と、前記金属含有膜の加工後に前記保護膜を除去する工程と、を含む半導体装置の製造方法。

(もっと読む)

171 - 180 / 3,239

[ Back to top ]