国際特許分類[H01L21/8246]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 1つの共通基板内または上に形成された複数の固体構成部品または集積回路からなる装置またはその特定部品の製造または処理;集積回路装置またはその特定部品の製造 (40,275) | 1つの共通基板内または上に形成される複数の固体構成部品または集積回路からなる装置の製造または処理 (31,691) | 複数の別個の装置に基板を分割することによるもの (31,691) | それぞれが複数の構成部品からなる装置,例.集積回路の製造 (31,684) | 基板がシリコン技術を用いる半導体であるもの (27,844) | 電界効果技術 (17,660) | MIS技術 (17,448) | メモリ構造 (10,964) | リードオンリーメモリ構造 (7,638)

国際特許分類[H01L21/8246]の下位に属する分類

電気的にプログラムできるもの (4,399)

国際特許分類[H01L21/8246]に分類される特許

151 - 160 / 3,239

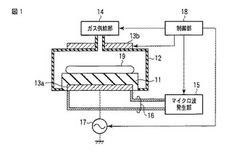

エッチング装置及び半導体装置の製造方法

【課題】難エッチング材料を、高速、高精度及び低ダメージでエッチングする。

【解決手段】実施形態に係わるエッチング装置は、上面側に披処理基板19が搭載されるステージ11と、ステージ11の上面側を覆うチャンバー12と、ステージ11の下面側に付加され、開口部を有する下部電極13aと、チャンバー12内にエッチングガスを供給するガス供給部14と、下部電極13aに高周波を印加することにより、チャンバー12内のエッチングガスをプラズマ化する高周波電源部17と、下部電極13aの開口部を介して被処理基板19にマイクロ波を印加することにより、披処理基板19の温度を最適範囲内に設定するマイクロ波発生部15と、ガス供給部14、高周波電源部17及びマイクロ波発生部15を制御する制御部18とを備える。

(もっと読む)

スピン注入磁化反転素子

【課題】MgOを障壁層として磁化反転電流を低減したTMR素子構造を備える光変調素子を提供する。

【解決手段】光変調素子5は、磁化固定層11、MgOからなる障壁層12、磁化自由層13を積層してなるTMR素子構造1と、その上下に接続した上部電極3、下部電極2を備える。下部電極2は、組成がCu1-xCrx(0.07<x<0.42)である非晶質のCu−Cr合金からなり、磁化固定層11は非晶質の磁性体からなり、このような非晶質の層の上に、障壁層12としてMgO膜が形成されるため、MgO膜が強い(001)面配向を示して、TMR素子構造1の磁化反転電流を低減できる。

(もっと読む)

トンネル磁気抵抗効果素子、それを用いた磁気メモリセル及びランダムアクセスメモリ

【課題】高熱安定性を有する高速超低消費電力不揮発性メモリを提供する。

【解決手段】不揮発性磁気メモリに、高い熱安定性をもつ自由層を適用した高出力なトンネル磁気抵抗効果素子を装備し、スピントランスファートルクによる書込み方式を適用する。トンネル磁気抵抗効果素子1は、CoとFeとBを含有する体心立方構造の第一の強磁性膜306と第二の強磁性膜308と第一の非磁性膜307で構成される自由層を持ち、自由層に(100)配向した岩塩構造のMgO絶縁膜305を介して固定層3021を積層した構造を有する。

(もっと読む)

磁気抵抗素子及び磁気メモリ

【課題】磁気抵抗素子の微細化に伴って増大する漏洩磁界をキャンセルする。

【解決手段】実施形態に係わる磁気抵抗素子は、垂直及び可変の磁化を持つ記憶層2と、垂直及び不変の磁化を持つ参照層4と、垂直、不変及び参照層3の磁化に対して逆向きの磁化を持つシフト調整層6と、記憶層2及び参照層4間の第1の非磁性層3と、参照層4及びシフト調整層6間の第2の非磁性層5とを備える。参照層4の反転磁界は、記憶層2の反転磁界と同じ又はそれよりも小さく、参照層4の磁気緩和定数は、記憶層2の磁気緩和定数よりも大きい。

(もっと読む)

半導体装置、電子装置、配線基板、半導体装置の製造方法、及び配線基板の製造方法

【課題】配線基板に半導体素子を形成する場合において、配線基板の製造工程数を少なくする。

【解決手段】コア層200の一面上には、第1配線232が設けられている。第1配線232上、及びその周囲に位置するコア層200の一面上には、半導体層236が形成されている。第1配線232及び半導体層236は、半導体素子を形成している。本実施形態において半導体素子は、第1配線232をゲート電極としたトランジスタ230であり、半導体層236と第1配線232の間に、ゲート絶縁膜234を有している。

(もっと読む)

磁気抵抗素子及び磁気メモリ

【課題】記憶層にかかる参照層からの漏れ磁場をキャンセルするシフト調整層の膜厚を低減することできる磁気抵抗素子を提供する。

【解決手段】磁化の向きが一方向に固定された参照層3と、磁化の向きが可変である記憶層2と、参照層3と記憶層2との間に設けられた非磁性層4と、参照層3の、非磁性層4が配置された面と反対の面側に配置され、参照層3が有する磁化の向きと反平行な磁化の向きを有する上部シフト層6と、記憶層2の、非磁性層4が配置された面と反対の面側に配置され、参照層3が有する磁化の向きと反平行な磁化の向きを有する下部シフト層8と、参照層3と上部シフト層6との間に配置された非磁性層5と、記憶層2と下部シフト層8との間に配置された非磁性層7とを備える。下部シフト層8の膜厚は、上部シフト層6の膜厚より薄い。

(もっと読む)

パターン形成用基板、圧電アクチュエータ製造方法、圧電アクチュエータ、液滴吐出ヘッド、および、液滴吐出装置

【課題】流動体を付着させて熱処理を行う工程を繰り返し行うことにより微細パターンの膜を所望の膜厚で精密に作製可能とするパターン形成用基板と、パターン形成用基板を用いた圧電アクチュエータの製造方法を提供する。

【解決手段】所定の流動体を特定領域に付着させて熱処理を行うことによりパターン化された膜を形成するためのパターン形成用基板10で、特定領域を親和性とし、それ以外の領域を非親和性とする表面改質をおこなう。パターン形成用基板10の表面改質処理対象となる金属膜はPt膜53を積層し、基体として、Ti,Ta,Zr,V,Nb,Mo,Wから選ばれる少なくとも1つの金属元素、酸素元素および炭素元素から構成されるMOC膜52を用いる。

(もっと読む)

磁気抵抗素子及び磁気メモリ

【課題】微細化に伴って増大する固定層からの漏れ磁場を低減でき、記憶層における磁化の平行と反平行の2つの状態を安定に存在できるようにした磁気抵抗素子を提供する。

【解決手段】磁気抵抗素子1は、固定層2、記憶層3、及び非磁性層4を備える。固定層2は、非磁性層4に接する第1強磁性材料31、第2強磁性材料32、第1強磁性材料31と第2強磁性材料32との間に設けられた第1非磁性材料33を有する。第1強磁性材料31は、Zr、Nb、Mo、Hf、Ta、Wのうちの少なくとも1つの元素と、Coとを含む。

(もっと読む)

スピン依存伝達特性を有する電界効果トランジスタ及びそれを用いた不揮発性メモリ

【課題】ソース及びドレインにハーフメタルを用いたトランジスタを提供する。

【解決手段】一方のスピンに対し金属的スピンバンド構造を、他方のスピンに対し半導体的スピンバンド構造をとるハーフメタルからなり、スピン偏極した伝導キャリアを注入する強磁性ソースと、注入されたスピン偏極した伝導キャリアを受けるハーフメタルからなる強磁性ドレインと、強磁性ソースと強磁性ドレインとの間に設けられた半導体層と、強磁性ソースと半導体層との間及び強磁性ドレインと半導体層との間に設けられた金属層と、半導体層に対して形成されるゲート電極と、ソース及びドレインに対して形成された非磁性コンタクトと、を有し、金属層は、半導体層との界面において、ショットキー接合を形成し、非磁性コンタクトのフェルミエネルギーは、それぞれ強磁性ソース及び強磁性ドレインの半導体的スピンバンドのバンドギャップ中を横切るトランジスタ。

(もっと読む)

磁気抵抗効果素子及びその製造方法

【課題】素子特性の劣化なしにリデポ現象による電気的ショートを防止する。

【解決手段】実施形態に係わる磁気抵抗効果素子は、磁化方向が可変の記憶層11と、記憶層11上のトンネルバリア層12と、トンネルバリア層12上の磁化方向が不変の参照層13と、参照層13上のハードマスク層14と、参照層13及びハードマスク層14の側壁上の側壁スペーサ層17とを備える。記憶層11及び参照層13は、垂直磁化を有し、参照層13の平面サイズは、記憶層11の平面サイズよりも小さい。記憶層11及び参照層13のサイズ差は、2nm以下であり、側壁スペーサ層17は、ダイアモンド、DLC、BN、SiC、B4C、Al2O3及びAlNのうちの1つを備える。

(もっと読む)

151 - 160 / 3,239

[ Back to top ]