国際特許分類[H01L21/8246]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 1つの共通基板内または上に形成された複数の固体構成部品または集積回路からなる装置またはその特定部品の製造または処理;集積回路装置またはその特定部品の製造 (40,275) | 1つの共通基板内または上に形成される複数の固体構成部品または集積回路からなる装置の製造または処理 (31,691) | 複数の別個の装置に基板を分割することによるもの (31,691) | それぞれが複数の構成部品からなる装置,例.集積回路の製造 (31,684) | 基板がシリコン技術を用いる半導体であるもの (27,844) | 電界効果技術 (17,660) | MIS技術 (17,448) | メモリ構造 (10,964) | リードオンリーメモリ構造 (7,638)

国際特許分類[H01L21/8246]の下位に属する分類

電気的にプログラムできるもの (4,399)

国際特許分類[H01L21/8246]に分類される特許

121 - 130 / 3,239

半導体装置の作製方法

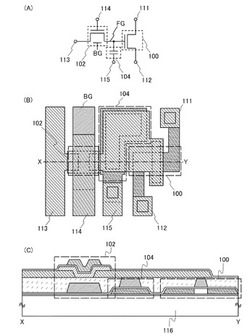

【課題】複数のトランジスタが高集積化された素子の少なくとも一のトランジスタに、作製工程数を増加させることなくバックゲートを設ける半導体装置を提供する。

【解決手段】複数のトランジスタが上下に積層されて設けられた素子において、少なくとも上部のトランジスタ102は、半導体特性を示す金属酸化物により設けられ、下部のトランジスタ100が有するゲート電極層を上部のトランジスタのチャネル形成領域と重畳するように配して、ゲート電極層と同一の層の一部を上部のトランジスタ102のバックゲートBGとして機能させる。下部のトランジスタ100は、絶縁層で覆われた状態で平坦化処理が施され、ゲート電極が露出され、上部のトランジスタ102のソース電極及びドレイン電極となる層に接続されている。

(もっと読む)

記憶装置及び記憶装置の製造方法

【課題】低電圧で動作する分極率の高い強誘電体メモリを提供する。

【解決手段】基板の上に形成された下部電極と、前記下部電極上に形成された強誘電体膜と、前記強誘電体膜上に形成された上部電極と、を有し、前記強誘電体膜は、第1の強誘電体膜と第2の強誘電体膜とを有しており、前記第1の強誘電体膜は、チタン酸ジルコン酸鉛を含む材料により形成されており、前記第2の強誘電体膜は、チタン酸ジルコン酸鉛を含む材料にRuがドープされているものにより形成されており、前記第2の強誘電体膜において、前記Ruは前記第2の強誘電体膜におけるPb、Zr、Tiのいずれかと置換しているものであることを特徴とする記憶装置により上記課題を解決する。

(もっと読む)

抵抗変化型メモリデバイスおよびその駆動方法

【課題】リファレンスセルの抵抗状態に応じて、読み出し電流を設定する構成で、誤書き込みによる抵抗の変化が発生することなく、より信頼性の高いリファレンス電流を得ることが可能な抵抗変化型メモリデバイスおよびその駆動方法を提供する。

【解決手段】素子両端に極性の異なる信号を印加することで可逆的に記憶素子の抵抗値が変化するメインメモリセルを含むメモリアレイ部と、素子両端に極性の異なる信号を印加することで可逆的に抵抗値が変化する記憶素子を含み、メインメモリセルのデータを識別するために必要な参照電流を発生させるリファレンスセルを含むリファレンスセル部と、を有し、リファレンスセルの抵抗状態に応じた参照電流の印加電流の向きが設定されている。

(もっと読む)

トンネル磁気抵抗効果素子、非局所スピン注入素子、及びそれを用いた磁気ヘッド

【課題】小さいバンドギャップを持つ障壁膜を岩塩構造の(001)方向に高配向させて、低抵抗かつ高効率なスピン注入素子を提供する。

【解決手段】下地膜300、非磁性シード膜310、強磁性膜305、障壁膜307、強磁性膜308、保護膜309を積層してトンネル磁気抵抗効果素子1を形成する。非磁性シード膜310として、格子定数が強磁性膜305の格子定数の√2倍よりも小さい面心立方格子の物質を用いる。

(もっと読む)

強誘電体膜の作製方法

【課題】 良好な規格化保持時間を有するエピタキシャル成長させて得られた強誘電体膜の作製方法を提供すること。

【解決手段】 チタン酸ストロンチウム単結晶基板又はシリコン単結晶基板上に、電極層を介して、強誘電体膜をエピタキシャル成長させて形成し、次いでエピタキシャル成長させて形成された強誘電体膜を冷却する強誘電体膜の作製方法において、この冷却を、少なくとも冷却を開始した後から該強誘電体のキュリー温度より15%高い温度〜15%低い温度の範囲までの冷却速度をその範囲の温度から室温までの冷却速度より遅くして実施する第1冷却工程と、次いで該第1冷却工程の冷却速度より早い冷却速度で室温まで冷却する第2冷却工程とで実施する。

(もっと読む)

磁気ランダムアクセスメモリ

【課題】記録層に作用する参照層からの漏洩磁界を低減しつつ、トンネルバリア層の絶縁不良を低減する。

【解決手段】実施形態による磁気ランダムアクセスメモリは、膜面に垂直方向の磁気異方性を有し、磁化方向が可変である記録層18と、膜面に垂直方向の磁気異方性を有し、磁化方向が不変である参照層16と、記録層及び参照層間に設けられた第1の非磁性層15と、をそれぞれ具備する複数の磁気抵抗素子10を備え、記録層は、複数の磁気抵抗素子毎に物理的に分離され、参照層及び第1の非磁性層は、複数の磁気抵抗素子を跨いで連続的に延在する。

(もっと読む)

情報格納装置

【課題】より容易な方法で集積度を向上させた情報格納装置を提供する。

【解決手段】本発明の情報格納装置は、基板と、基板上のゲートライン構造体を含むトランジスターと、少なくとも一部が基板内に埋め込まれてトランジスターの活性領域を定義する導電性分離パターン(conductive isolation patterns)と、を有し、導電性分離パターンは、互いに電気的に連結される。

(もっと読む)

抵抗変化メモリ及びその製造方法

【課題】チップ面積の縮小を図る。

【解決手段】磁気ランダムアクセスメモリは、メモリセル部の素子領域10a上に形成された第1の拡散層17aと、第1の拡散層に接続された第1のコンタクトCB1と、第1のコンタクト上に形成された第1の下部電極層21aと、第1の下部電極層上に形成された第1の抵抗変化層22a及び第1の上部電極層23aと、周辺回路部において互いに異なる素子領域に形成された第2乃至第4の拡散層17d、17eと、第2乃至第4の拡散層に接続された第2乃至第4のコンタクトCS1、CS2と、第1の下部電極層、第1の抵抗変化層、第1の上部電極層と同じ高さに形成された第2の下部電極層21b、第2の抵抗変化層22b、第2の上部電極層23bとを具備する。第2の下部電極層は、第2及び第3のコンタクトを接続する第1のローカル配線L1として機能する。

(もっと読む)

磁気ランダムアクセスメモリ

【課題】磁壁移動型MRAMのメモリセルの面積を小さくする。

【解決手段】磁気ランダムアクセスメモリが、メモリセルC1〜C3が形成されたメモリセルライン1と、書き込みビット線12−1〜12−4とを具備する。メモリセルライン1は、磁気記録層4と、磁化固定層3−1〜3−4と、リファレンス層6−1〜6−3と、スペーサ層5−1〜5−3と、nMOSトランジスタ2−1〜2−4とを備えている。スペーサ層5−iとリファレンス層6−iとは、磁化固定層3−iと磁化固定層3−(i+1)の間に位置している。磁化固定層3−1、3−3と、磁化固定層3−2、3−4は、互いに逆の方向に固定された磁化を有している。リファレンス層6−1〜6−3も、固定された磁化を有している。nMOSトランジスタ2−iは、書き込みビット線12−iと磁化固定層3−iの間に設けられている。

(もっと読む)

光不揮発性メモリ

【課題】光信号を直接不揮発的に記憶する光不揮発性メモリを提供すること。

【解決手段】第1導電型を有する第1半導体層12と、前記第1導電型とは異なる第2導電型を有する第2半導体層16と、前記第1半導体層と前記第2半導体層とに挟まれ、逆バイアスが印加されることにより受光し、順バイアスが印加されることにより発光する活性層14と、前記活性層の受光する光の強さによって磁化方向が変化する強磁性体層20と、を具備する光不揮発性メモリ。

(もっと読む)

121 - 130 / 3,239

[ Back to top ]