国際特許分類[H01L21/8246]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 1つの共通基板内または上に形成された複数の固体構成部品または集積回路からなる装置またはその特定部品の製造または処理;集積回路装置またはその特定部品の製造 (40,275) | 1つの共通基板内または上に形成される複数の固体構成部品または集積回路からなる装置の製造または処理 (31,691) | 複数の別個の装置に基板を分割することによるもの (31,691) | それぞれが複数の構成部品からなる装置,例.集積回路の製造 (31,684) | 基板がシリコン技術を用いる半導体であるもの (27,844) | 電界効果技術 (17,660) | MIS技術 (17,448) | メモリ構造 (10,964) | リードオンリーメモリ構造 (7,638)

国際特許分類[H01L21/8246]の下位に属する分類

電気的にプログラムできるもの (4,399)

国際特許分類[H01L21/8246]に分類される特許

91 - 100 / 3,239

半導体記憶装置

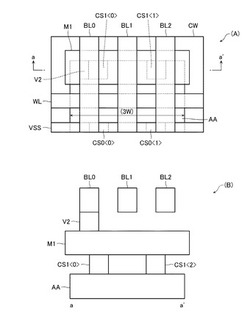

【課題】ゲート面積に依存するトランジスタばらつきを抑制し、読み出し動作を高速化した半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、ロウ方向に延びるワード線WL、カラム方向に延びる複数のビット線BL0,BL1,BL2で構成されたビット線グループ、並びに、トランジスタからなりワード線及びビット線グループの交差部に設けられたメモリセル、を有するメモリセルアレイと、ビット線を介してメモリセルからデータを読む読み出し回路とを備え、メモリセルは、トランジスタのソース又はドレインを、ビット線グループに属する複数のビット線BL0,BL1,BL2のいずれとも接続しないか又はいずれか1本とだけ接続するかの異なる接続状態を有し、トランジスタのゲートとなるアクティブ領域AAは、ビット線グループの複数のビット線BL0,BL1,BL2の配置領域及び各ビット線間のスペースに連続的に形成されている

(もっと読む)

磁気メモリ

【課題】磁気記録層の強磁性体膜が強い垂直磁気異方性を有する磁気メモリを提供する。

【解決手段】磁気メモリは、強磁性体の下地層51と、下地層51上にの第1非磁性52と、第1非磁性52上の垂直磁気異方性を有する強磁性体のデータ記憶層53と、第2非磁性層20を介してデータ記憶層53に接続された参照層30と、下地層51の下側に接した第1、第2磁化固定層41a、41bとを具備する。データ記憶層53は、反転可能な磁化を有し参照層30とオーバーラップする磁化自由領域13と、磁化自由領域13の端に接続され、第1磁化固定層41aに+z方向に磁化固定された第1磁化固定領域11aと、磁化自由領域13の他の端に接続され、第2磁化固定層41bに−z方向に磁化固定された第2磁化固定領域11bとを備える。磁化自由領域13下の第1非磁性52は、第1、第2磁化固定領域11a、11b下の第1非磁性52よりも厚い。

(もっと読む)

半導体磁気記憶装置

【課題】磁気記憶素子を構成する層を、周辺回路部内で有効に活用する。

【解決手段】実施形態によれば、半導体磁気記憶装置は、セルトランジスタを含むセル部と、周辺トランジスタを含む周辺回路部とが形成された半導体基板を備える。さらに、前記装置は、前記セル部内に配置され、下部電極と、前記下部電極上に形成された電極間層と、前記電極間層上に形成された上部電極とを含む磁気記憶素子を備える。さらに、前記装置は、前記周辺回路部内に配置され、前記下部電極を形成している第1の層と、前記電極間層を形成している第2の層と、前記上部電極を形成している第3の層とを含む構造体を備える。さらに、前記装置は、前記第1の層に電気的に接続された第1及び第2のプラグを備える。さらに、前記第1の層は、前記第1のプラグと前記第2のプラグを電気的に接続する配線として機能する。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】MTJ素子内における層間の短絡を抑制し、かつ、MTJ素子を構成する磁性層の劣化を抑制した半導体記憶装置およびその製造方法を提供する。

【解決手段】本実施形態による半導体記憶装置は半導体基板を備える。磁気トンネル接合素子は、2つの磁性層と該2つの磁性層間に設けられたトンネル絶縁膜とを含み、半導体基板の上方に設けられている。側壁膜は、磁気トンネル接合素子の側面の上部に設けられている。フェンス層は、導電性材料を含み、側壁膜の側面および磁気トンネル接合素子の側面の下部に設けられている。保護膜は、絶縁体からなりフェンス層の側面に設けられている。フェンス層の上面および保護膜の上面は、側壁膜の上面よりも低く、かつ、トンネル絶縁膜よりも高い位置にある。

(もっと読む)

二重フローティングゲート構造を有するトランジスタを備えた不揮発性メモリ

【課題】CMOS製造プロセスに用いることのできる材料を用いかつノイズマージンの広い不揮発性メモリを提供する。

【解決手段】本実施形態の不揮発性メモリによれば、第1および第2のPチャネルトランジスタはそれぞれ第1の半導体領域上に設けられ、第1の半導体領域上に、第1の絶縁膜と、第1のフローティングゲート、第2の絶縁膜、第2のフローティングゲート、第3の絶縁膜、および第1の制御ゲートが、この順序で積層された構造を有し、前記第1および第2のNチャネルトランジスタはそれぞれ第2の半導体領域上に設けられ、前記第2の半導体領域上に、第4の絶縁膜、第3のフローティングゲート、第5の絶縁膜、第4のフローティングゲート、第6の絶縁膜、および第2の制御ゲートがこの順序で積層された積層構造を有している。

(もっと読む)

ナノヘテロ構造強誘電体およびその製造方法

【課題】ナノ構造を有し、高い比誘電率を有する強誘電体を提供すること。

【解決手段】格子定数が下記式(1):

1≦(a2/a1)×100≦80 (1)

(式(1)中、a1は第一強誘電材料の格子定数であり、a2は第二強誘電材料の格子定数であり、a1>a2である。)

で表される条件を満たす第一強誘電材料および第二強誘電材料のうちの一方の無機成分からなるマトリックス中に、前記第一強誘電材料および前記第二強誘電材料のうちの他方の無機成分が、球状、柱状およびジャイロイド状からなる群から選択される形状で、三次元的且つ周期的に配置しており、繰り返し構造の一単位の長さの平均値が1nm〜100nmである三次元的周期構造を有していることを特徴とするナノヘテロ構造強誘電体。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】メモリセル部及び周辺回路部を微細化する。

【解決手段】半導体基板20に設けられたメモリセル部11及び周辺回路部12を有する半導体記憶装置の製造方法であって、メモリセル部11及び周辺回路部12にそれぞれ層間絶縁層37及び47を形成する工程と、層間絶縁層37及び47上にそれぞれ、心材50を形成する工程と、心材50をスリミングする工程と、メモリセル部11及び周辺回路部12の心材50の側面にそれぞれ、側壁38及び48を形成する工程と、側壁38及び48をマスクとして、層間絶縁層37及び47を加工する工程と、加工された層間絶縁層37及び47内にそれぞれビット線BL及び配線層44を形成する工程とを含む。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】MTJ素子内における層間の短絡を抑制し、かつ、MTJ素子を構成する磁性層の劣化を抑制した半導体記憶装置およびその製造方法を提供する。

【解決手段】本実施形態による半導体記憶装置は、半導体基板を備える。磁気トンネル接合素子は、2つの磁性層と該2つの磁性層間に設けられたトンネル絶縁膜とを含み、半導体基板の上方に設けられている。側壁膜は、磁気トンネル接合素子の側面の上部に設けられている。フェンス層は、導電性材料を含み、側壁膜の側面および磁気トンネル接合素子の側面の下部に設けられている。フェンス層の頂点は、側壁膜の頂点よりも低く、かつ、トンネル絶縁膜よりも高い位置にある。

(もっと読む)

半導体装置

【課題】オン電流が少ないトランジスタを含むメモリセルと積層方向に延びるビット線により、低い製造コストで高速動作を実現可能な半導体装置を提供する。

【解決手段】本発明の半導体装置は、例えば、記憶素子とその読み出し電流経路に挿入される第1のトランジスタとを含むメモリセルMCと、このメモリセルMCの一端に直接接続され、記憶素子の情報を伝送する第1のビット線LBLと、第2のトランジスタを含み第1のビット線LBLを介して伝送される記憶素子の情報を増幅する第1のアンプLSAとを備えている。第1のアンプLSAは基板L0に形成され、メモリセルMCは基板L0の上部の第1の層L1〜L8に形成され、第1のビット線LBLは積層方向に延びる配線構造を含んで形成される。第1のトランジスタのチャネル中のキャリアの移動度は、第2のトランジスタのチャネル中のキャリアの移動度よりも低い。

(もっと読む)

半導体装置

【課題】オフリーク電流の抑制および駆動電流の増大を図ることが可能な半導体装置を提供する。

【解決手段】実施形態の半導体装置において、ゲート電極は、第1および第2のソース・ドレイン領域の間に設けられた第1リセス内に少なくとも一部がゲート絶縁膜を介して埋め込まれて第1および第2のソース・ドレイン領域よりも深い位置まで形成される。チャネルは、素子領域においてゲート絶縁膜に隣接して第1および第2のソース・ドレイン領域の間に形成される。一対の応力付与部は、素子分離領域において、ゲート電極のゲート幅方向に垂直な面内において第1および第2のソース・ドレイン領域の下部のチャネルと重複する領域に設けられ、素子分離領域の構成材料と異なる絶縁材料からなりチャネルに対してゲート幅方向の両側から応力を付与する。

(もっと読む)

91 - 100 / 3,239

[ Back to top ]