国際特許分類[H01L21/8246]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 1つの共通基板内または上に形成された複数の固体構成部品または集積回路からなる装置またはその特定部品の製造または処理;集積回路装置またはその特定部品の製造 (40,275) | 1つの共通基板内または上に形成される複数の固体構成部品または集積回路からなる装置の製造または処理 (31,691) | 複数の別個の装置に基板を分割することによるもの (31,691) | それぞれが複数の構成部品からなる装置,例.集積回路の製造 (31,684) | 基板がシリコン技術を用いる半導体であるもの (27,844) | 電界効果技術 (17,660) | MIS技術 (17,448) | メモリ構造 (10,964) | リードオンリーメモリ構造 (7,638)

国際特許分類[H01L21/8246]の下位に属する分類

電気的にプログラムできるもの (4,399)

国際特許分類[H01L21/8246]に分類される特許

181 - 190 / 3,239

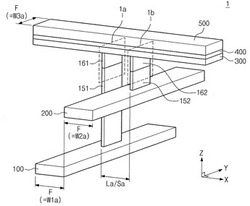

3次元ダブルクロスポイントアレイを有する半導体メモリ素子及びその製造方法

【課題】単純な方式で集積度が向上し電気的特性が改善された3次元ダブルクロスポイントアレイを有する半導体メモリ素子及びその製造方法を提供する。

【解決手段】本発明の半導体メモリ素子は、互いに異なるレベルに配置され、2つの交差点を定義する第1、第2、及び第3導線と、2つの交差点の各々に配置される2つのメモリセルを備え、第1及び第2導線は互いに平行に延長され、第3導線は延長されて第1及び第2導線と交差し、第1及び第2導線は垂直断面で見た時に第3導線の長さに沿って交互に配列され、第3導線は第1及び第2導線から垂直に離隔される。

(もっと読む)

セルの配置構造、半導体集積回路、及び回路素子セルの配置方法

【課題】セルベース設計において複数の記憶素子セルが配置される構成において、効率的に且つ確実に複数ビットのソフトエラーの発生を抑制することが可能なセルの配置構造を提供する。

【解決手段】回路素子セルの配置構造は、第1の方向に延展するセル配置列上に並べられた複数の記憶素子セルと、複数の記憶素子セルの各々の領域において第1の方向に垂直な第2の方向に並べられた第1のNウェル及び第1のPウェルと、複数の記憶素子セルのうち少なくとも2つの互いに隣接する記憶素子セルの間に設けられ、セル配置列の幅に亘る長さを各々が有する第2のNウェル及び第2のPウェルとを含み、第1のNウェルと第2のNウェルとは一体であり、第1のPウェルと第2のPウェルとは一体である。

(もっと読む)

ニッケル酸ランタン膜形成用組成物の製造方法、ニッケル酸ランタン膜の製造方法、及び圧電素子の製造方法

【課題】特殊な環境が不要で短時間且つ低コストでニッケル酸ランタン膜形成用組成物を製造することができるニッケル酸ランタン膜形成用組成物の製造方法、ニッケル酸ランタン膜の製造方法、及び圧電素子の製造方法を提供する。

【解決手段】圧電素子300(アクチュエーター)は、絶縁体膜55上に、第1電極60と、第1電極60の上方に設けられて厚さが3μm以下、好ましくは0.3〜1.5μmの薄膜である圧電体層70と、圧電体層70の上方に設けられた第2電極80とが、積層形成される。圧電膜70であるニッケル酸ランタン膜形成用組成物は、ランタンアセチルアセトナート、ニッケルアセチルアセトナート、酢酸、及び水を混合して混合溶液を得た後、混合溶液を加熱する。

(もっと読む)

半導体記憶装置

【課題】記憶素子に充分な電流を流すことができるようにセルトランジスタの電流駆動能力を充分に確保しつつ、ユニットセルのレイアウト面積が従来よりも小さい半導体記憶装置を提供する。

【解決手段】本実施形態による半導体記憶装置は、半導体基板と、半導体基板に形成されたアクティブエリアを備える。複数のセルトランジスタがアクティブエリアに形成されている。第1のビット線および第2のビット線は、互いに対をなす。複数のワード線は第1および第2のビット線と交差する。複数の記憶素子の一端がセルトランジスタのソースまたはドレインに電気的に接続され、他端が第1または第2のビット線に接続されている。第1および第2のビット線は、両方とも同一のアクティブエリアに対して記憶素子を介して接続されている。

(もっと読む)

信号処理回路

【課題】新たな構成の不揮発性の記憶回路を用いた信号処理回路を提供する。

【解決手段】信号処理回路は、電源電圧が選択的に供給され、第1の高電源電位が選択的に与えられる第1のノードを有する回路と、第1のノードの電位を保持する不揮発性の記憶回路とを有する。不揮発性の記憶回路は、チャネルが酸化物半導体層に形成されるトランジスタと、トランジスタがオフ状態となることによってフローティングとなる第2のノードとを有する。トランジスタはエンハンスメント型のnチャネル型のトランジスタである。トランジスタのゲートには、第2の高電源電位または接地電位が入力される。電源電圧が供給されないとき、トランジスタはゲートに接地電位が入力されてオフ状態を維持する。第2の高電源電位は、第1の高電源電位よりも高い。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】メモリセルを微細化しても、抵抗変化動作に十分な電流を流すことが可能なダイオードを備える抵抗変化型の不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置は、X方向に延在する第1配線13と、Y方向に延在する第2配線20と、第1配線13と第2配線20との交点に設けられたメモリセル10とを具備する。メモリセル10は、第1配線13上に設けられ一端を第1配線13に接続されたダイオード15と、ダイオード15上方に設けられ一端をダイオード15に直列接続され、他端を第2配線20に接続され、抵抗値の変化で情報を記憶する抵抗変化部19とを備えている。ダイオード15は、第1導電型の第1半導体層13と、第2導電型で、第1半導体層13の内部に伸びている第2半導体層14とを含んでいる。

(もっと読む)

半導体装置

【課題】瞬断もしくは瞬時電圧低下等の極めて短時間の電源停止又は電源電圧低下の場合でさえ、揮発性メモリ内のデータが消失してしまう場合があった。そこで、高速データ処理のために揮発性メモリを用いた場合であっても、データの保持時間を延ばす。

【解決手段】容量素子及び酸化物半導体を用いたトランジスタを有するメモリに揮発性メモリのデータ内容をバックアップしておくことによって、データの保持時間を長くすることができる。

(もっと読む)

強誘電体薄膜の製造方法

【課題】(100)面に優先的に結晶配向が制御された強誘電体薄膜をシード層やバッファ層を設けることなく、簡便に得ることが可能な、強誘電体薄膜の製造方法を提供する。

【解決手段】結晶面が(111)軸方向に配向した下部電極を有する基板の下部電極上に、強誘電体薄膜形成用組成物を塗布し、加熱して結晶化させることにより下部電極上に強誘電体薄膜を製造する方法の改良であり、強誘電体薄膜が(100)面に優先的に結晶配向が制御された配向制御層により構成され、配向制御層を結晶化後の層厚を35nm〜150nmの範囲内にすることにより形成することを特徴とする。

(もっと読む)

強誘電体キャパシタ

【課題】還元性雰囲気による特性劣化を抑制することができる構造の強誘電体キャパシタを提供する。

【解決手段】強誘電体キャパシタ積層構造8は、強誘電体膜3と、強誘電体膜の一方表面に接する下部電極2と、強誘電体膜3の他方表面に接する上部電極4とを含む。上部電極4および下部電極2のうちのうちの少なくともいずれか一方が、酸化物導電体層と金属層とを交互に積層した積層電極構造を有している。この積層電極構造は、酸化物導電体層および金属層のうちの少なくともいずれか一方を2層以上含む。

(もっと読む)

半導体記憶装置

【課題】電源電圧の供給の停止及び再開を行う構成において、揮発性の記憶装置と不揮発性の記憶装置との間のデータの退避及び復帰の必要のない半導体記憶装置を提供する。

【解決手段】不揮発性の半導体記憶装置とする際、揮発性の記憶装置と不揮発性の記憶装置を分離することなく構成する。具体的に半導体記憶装置には、酸化物半導体を半導体層に有するトランジスタ及び容量素子に接続されたデータ保持部にデータを保持する構成とする。そしてデータ保持部に保持される電位は、電荷をリークすることなくデータの出力が可能なデータ電位保持回路及び電荷をリークすることなくデータ保持部に保持した電位を容量素子を介した容量結合により制御可能なデータ電位制御回路で制御される。

(もっと読む)

181 - 190 / 3,239

[ Back to top ]