国際特許分類[H01L27/04]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 1つの共通基板内または上に形成された複数の半導体構成部品または他の固体構成部品からなる装置 (52,733) | 整流,発振,増幅またはスイッチングに特に適用される半導体構成部品を含むものであり,少なくとも1つの電位障壁または表面障壁を有するもの;少なくとも1つの電位障壁または表面障壁を有する集積化された受動回路素子を含むもの (38,321) | 基板が半導体本体であるもの (36,153)

国際特許分類[H01L27/04]の下位に属する分類

複数の個々の構成部品を反復しない形で含むもの (2,326)

1種類の半導体構成部品だけを含むもの (8,288)

複数の個々の構成部品を反復した形で含むもの (15,853)

国際特許分類[H01L27/04]に分類される特許

161 - 170 / 9,686

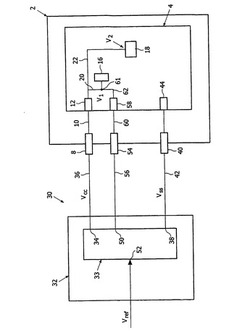

集積回路への電力供給方法、システム及びそれに使用される集積回路

【課題】半導体チップに供給する電圧を、公称最大動作電圧を超えて増加可能にする電力供給方法の提供。

【解決手段】組立てパッケージ内に所定の最大動作電圧を超えない電源電圧で動作するようにされた少なくとも一つの電力入力を有する複数の論理回路16を有するチップ4を有する集積回路2への電力供給方法は、論理回路の選択された1つの論理回路の電力入力において、論理回路の1つにおける電力入力においてチップ内に位置する計測点61で第2の電源電圧を直接測定すること、および計測点と選択された1つの論理回路の電源入力間の電圧降下に基づいて第1の電源電圧を決定するステップと、第1の電源電圧を、論理回路の選択された1つにおける所定の最大動作電圧に調節されるような値を有する基準電圧に調節するステップ、を備える。

(もっと読む)

半導体装置

【課題】寿命が長い半導体装置を提供する。

【解決手段】このLSIは、2つのCPU1,2と、CPU1,2のうちのいずれか1つのCPUを示す論理レベルのデータ信号が書き込まれた記憶回路4と、リセット信号REが非活性化レベルにされてLSIのリセットが解除された場合、記憶回路4の記憶データの論理レベルに対応するCPUのみに電源電圧を供給するとともに、記憶回路4の記憶データを現在の論理レベルと異なる論理レベルのデータ信号に書き換える制御回路3,5とを備える。したがって、故障の検知や、厳密なタイミング制御を必要とせずに、CPUの長寿命化を図ることができる。

(もっと読む)

半導体装置

【課題】残渣による配線間のショートの発生を防ぐ。

【解決手段】本発明の半導体装置は、高誘電率材料を含む第1のゲート絶縁膜4と第1のゲート絶縁膜4上に形成された第1のメタルゲート電極5とを備える第1のトランジスタが形成される半導体基板上の第1の領域と、高誘電率材料を含む第2のゲート絶縁膜4と第2のゲート絶縁膜上に形成された第2のメタルゲート電極12とを備え、第1のトランジスタとは閾値電圧の異なる第2のトランジスタが形成される半導体基板上の第1の領域に並ぶ第2の領域と、電位の異なる第1および第2の配線と、を有し、第1の領域と第2の領域との境界が、第1および第2の配線の少なくとも一方としか重ならない。

(もっと読む)

半導体集積回路装置

【課題】過電流に対して内部回路を保護する半導体集積回路装置を提供することを目的としている。

【解決手段】多層配線構造を有する半導体集積回路装置であって、半導体集積回路装置の内部にある内部回路と半導体集積回路装置の外部にある外部回路とを接続するために半導体集積回路装置の内部に設けられたパッドパターンにおいて、第1の配線層と、第1の配線層が形成されている層とは別の層に形成されている第2の配線層と、第1の配線層と第2の配線層を接続するビアと、を備え、第2の配線層にヒューズパターンが形成されており、ヒューズパターンを経由して内部回路と外部回路とを電気的に接続する。

(もっと読む)

半導体装置及びこれを備える情報処理装置

【課題】安定したチャージポンプ動作を行う。

【解決手段】ノードA,Bを有するコンデンサC1と、VDDレベルからVSSレベルの間で振幅するポンピング信号PUMP1をコンデンサC1のノードAに供給するポンピング回路110と、コンデンサC1のノードBをVPPextレベルにプリチャージし、ポンピング信号PUMP1がVSSレベルからVDDレベルに変わった時に、コンデンサC1のノードBをVPPextレベルよりも高いレベルに駆動する出力回路120とを備える。本発明によれば、コンデンサC1のノードAをポンピングするための電圧と、コンデンサC1のノードBをプリチャージするための電圧が異なっていることから、昇圧電圧を効率よく生成することできる。

(もっと読む)

半導体装置

【課題】 半導体装置の耐圧の低下を抑制する。

【解決手段】 半導体装置54は、半導体基板50と、半導体基板の表面上に配置される絶縁膜20と、絶縁膜の表面上に配置される電極16,28と、電極16,18に電圧を印加する電圧印加回路44を有している。半導体基板50は、セル領域100と、そのセル領域に隣接する非セル領域200とを備える。セル領域100には半導体素子が形成されており、非セル領域200には耐圧構造が形成されている。絶縁膜20は、非セル領域の表面に形成されている。電極16,18は、半導体基板から電気的に分離されている。電圧印加回路44は、半導体素子に電圧が印加されていない期間の少なくとも一部において電極16,18に電圧を印加する。

(もっと読む)

アナログ/デジタル変換器

【課題】変換精度が高いアナログ/デジタル変換器を提供する。

【解決手段】アナログ/デジタル変換器は、電圧生成部と複数の比較器とを備える。電圧生成部は、基準電圧を、複数の抵抗器で分圧して複数の比較用電圧を生成する。各比較器は、複数の比較用電圧のうちの何れかの比較用電圧とアナログの入力電圧との比較結果に応じたデジタル信号を出力する。各比較器は、2つの入力の電位差を検出する差動対回路を含む。差動対回路は、第1回路部50と第2回路部60とを有する。第1回路部は、第1入力トランジスタ51と、第1入力トランジスタと直列に接続される抵抗器Rrefとを含む。第2回路部は、第1入力トランジスタと差動対を形成する第2入力トランジスタ61と、第2入力トランジスタと直列に接続される可変抵抗器Rvとを含む。可変抵抗器は、直列に接続されるとともに、制御信号に応じて各々の抵抗値が可変に設定される複数の可変抵抗素子を含む。

(もっと読む)

シミュレーション装置およびシミュレーション方法

【課題】ESD保護素子を有する半導体回路の回路シミュレーションを高速かつ精度よく行うことができるシミュレーション装置を提供する。

【解決手段】ESD保護素子を有する半導体回路の動作検証を行うシミュレーション装置は、ESD保護素子の等価回路のパラメータファイルを作成する第1のパラメータファイル作成部と、半導体回路内のESD保護素子以外の内部回路のパラメータファイルを作成する第2のパラメータファイル作成部と、作成したパラメータファイルを記憶するパラメータファイル記憶部と、記憶したパラメータファイルを選択するパラメータファイル選択部と、選択したパラメータファイルを利用して半導体回路のネットリストを作成するネットリスト作成部と、ネットリストに基づいて半導体回路の動作検証を行うシミュレーション実行部とを備える。

(もっと読む)

半導体装置

【課題】耐圧を向上させ、オン抵抗を下げることが可能な半導体装置を提供する。

【解決手段】一態様に係る半導体装置は、MOSFETとして機能する第1領域、及び第1領域に隣接する第2領域を有する。第2領域は、第1半導体層、複数の第2トレンチ、第2絶縁層、及びフローティング電極層を有する。複数の第2トレンチは、第1半導体層の上面側から第1半導体層内に延びる。第2絶縁層は、第2トレンチの内壁に沿って形成される。フローティング電極層は、第2絶縁層を介して第2トレンチを埋めるように形成され且つフローティングとされる。

(もっと読む)

半導体集積回路のテスト回路及びテスト方法

【課題】外部端子数の増加を抑えつつ、半導体集積回路のテスト時間を短縮する。

【解決手段】テスト回路は、入力されるリファレンスクロック109を逓倍して、テスト対象回路106をテスト動作させるための実動作クロック112及びサンプリングクロック105を生成するPLL108と、入力されるテストコマンドに従い、テスタ同期クロック103に同期してテスト対象回路106のテスト結果を出力するテスト結果出力回路107と、を備えるテスト回路であって、テストコマンドを含むテスト入力信号104とサンプリングクロック105とに基づきテスタ同期クロック103を生成するテスタ同期クロック生成回路100を備えるものである。

(もっと読む)

161 - 170 / 9,686

[ Back to top ]