国際特許分類[H01L27/04]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 1つの共通基板内または上に形成された複数の半導体構成部品または他の固体構成部品からなる装置 (52,733) | 整流,発振,増幅またはスイッチングに特に適用される半導体構成部品を含むものであり,少なくとも1つの電位障壁または表面障壁を有するもの;少なくとも1つの電位障壁または表面障壁を有する集積化された受動回路素子を含むもの (38,321) | 基板が半導体本体であるもの (36,153)

国際特許分類[H01L27/04]の下位に属する分類

複数の個々の構成部品を反復しない形で含むもの (2,326)

1種類の半導体構成部品だけを含むもの (8,288)

複数の個々の構成部品を反復した形で含むもの (15,853)

国際特許分類[H01L27/04]に分類される特許

121 - 130 / 9,686

半導体装置及びこれを備える半導体モジュール

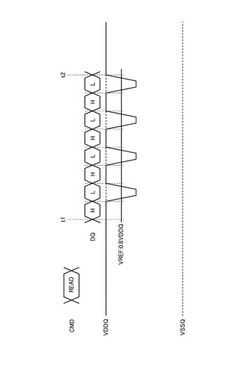

【課題】データ出力バッファの正確なインピーダンスキャリブレーション動作を行う。

【解決手段】電源ラインVL1とデータ端子24との間に接続されたP型トランジスタユニット201と、電源ラインVL1とキャリブレーション端子ZQとの間に接続されたP型トランジスタユニット111〜114と、キャリブレーション端子ZQの電位が基準電位VREFと一致するよう、P型トランジスタユニット111〜114インピーダンスを調整し、一致した状態におけるP型トランジスタユニット111〜114の一つのインピーダンスをP型トランジスタユニット201に反映させるインピーダンス制御回路とを備える。これにより、基準電位VREFが電源電位VDDの半分のレベルからオフセットしたレベルに設定されている場合であっても、正確なキャリブレーション動作を行うことができる。

(もっと読む)

半導体ウエハ、半導体装置、および、半導体装置の製造方法

【課題】半導体チップのチップ面積の削減を図るとともに、半導体チップへの入力を記憶させる時間を短縮する。

【解決手段】本発明の半導体ウエハ1は、チップ領域10に形成され、絶縁膜を有し、電圧の印加による絶縁膜の絶縁破壊により導通状態となる複数のアンチヒューズ14を有するアンチヒューズ回路12と、チップ領域10を区画するダイシング領域20に複数のアンチヒューズ14の各々に対応して形成され、配線を有し、レーザー照射による配線の切断により非導通状態となる複数のレーザーヒューズ24を有するレーザーヒューズ回路22と、複数のアンチヒューズ14のうち、半導体チップへの入力に応じて非導通状態とされたレーザーヒューズ22に対応するアンチヒューズ14の有する絶縁膜に、電源からの電圧を印加させて、そのアンチヒューズ14を導通状態とする制御回路13と、を有する。

(もっと読む)

半導体装置

【課題】従来の半導体装置においては、配線の伝送特性が不安定となってしまう。

【解決手段】半導体装置1は、配線10、およびダミー導体パターン20を備えている。配線10は、5GHz以上の周波数を有する電流が流れる配線である。配線10の近傍には、ダミー導体パターン20が配置されている。ダミー導体パターン20の平面形状は、180°を超える内角を有する図形に等しい。

(もっと読む)

半導体装置

【課題】無線通信により交信可能な半導体装置において、個体識別子を容易に付けることができるようにする。

【解決手段】薄膜トランジスタ119と、薄膜トランジスタ上に第1の層間絶縁膜156と、第1の層間絶縁膜上の、ソース領域またはドレイン領域の一方に電気的に接続される第1の電極114と、ソース領域またはドレイン領域の他方に電気的に接続される第2の電極110と、第1の層間絶縁膜、第1の電極、及び第2の電極上に形成された第2の層間絶縁膜135と、第2の層間絶縁膜上の、第1の電極または第2の電極の一方に電気的に接続される第1の配線177と、第2の層間絶縁膜上の、第1の電極または第2の電極の他方に電気的に接続されない第2の配線178とを有し、第2の配線と前記第1の電極または第2の電極の他方は、第2の層間絶縁膜中の分断領域169によって、電気的に接続されない半導体装置及びその作製方法に関するものである。

(もっと読む)

半導体装置

【課題】電源線と機能回路の間に電源スイッチとして接続されるMOSトランジスタのオン時のバックゲートの電圧を簡単な構造で調整することができる半導体装置を提供する。

【解決手段】一対の電源線2、3と、機能回路4a0〜4anと、一対の電源線2、3との少なくとも一方と機能回路4a0〜4anの間に接続されるスイッチング回路6a0〜6an、7a0〜7anとを有し、スイッチング回路6a0〜6an、7a0〜7anは、ソース/ドレインの一方が機能回路4a0〜4anに接続され、他方が前記一対の電源線2、3の一方に接続される第1のMOSトランジス11と、第1のMOSトランジスタ11のゲートとバックゲートを接続する抵抗素子12、21と、第1のMOSトランジスタ11のゲートに接続されるゲート電圧制御回路13と、を有する。

(もっと読む)

半導体ウエハ、半導体ウエハ検査装置、及び半導体ウエハの検査方法

【課題】本発明は、半導体ウエハの検査において、半導体ウエハの裏面電極の端子としての機能を維持しつつ、半導体ウエハに過度の力がかかることを防止できる半導体ウエハ、半導体ウエハ検査装置、及び半導体ウエハの検査方法を提供することを目的とする。

【解決手段】本発明に係る半導体ウエハは、ダイシングラインを隔てて複数のチップが並ぶ半導体ウエハの表面側に形成された表面電極と、該半導体ウエハの裏面側に、該ダイシングラインを隔てて形成された複数の裏面電極と、該半導体ウエハの裏面側に、該ダイシングラインを跨いで該複数の裏面電極を電気的に接続する接続パターンと、を備える。該複数の裏面電極のうちの少なくともひとつは、該半導体ウエハのバイアホールを介して該表面電極と電気的に接続される。

(もっと読む)

シリコン装置

【課題】強誘電体層中の金属原子がシリコン層に拡散することを抑制または防止して、小型化および特性の向上を図ることができる構造のシリコン装置を提供する。

【解決手段】シリコン装置としてのインクジェットプリンタヘッド1は、シリコン基板2と、シリコン基板2上に形成された酸化シリコン層5Bと、酸化シリコン層5B上に形成された拡散防止膜70と、拡散防止膜70上に設けられた圧電素子6とを含む。シリコン基板2にはインク溜まりとしての加圧室62が形成されており、その天面部の薄いシリコン層5Aと酸化シリコン層5Bとが振動膜5を構成している。圧電素子6は、拡散防止膜70に接する下部電極7と、下部電極7上に設けられた圧電体層8と、圧電体層8上に設けられた上部電極9とを含む。拡散防止膜70は、圧電体層8中の金属原子の拡散を防ぐ。

(もっと読む)

ウェハ裏面のキャパシタを有する半導体デバイスを形成する方法

【課題】 ウェハ裏面のキャパシタを有する半導体デバイスの形成方法を提供する。

【解決手段】 本発明の方法は、その前面の活性シリコン層とその裏面のバルク・シリコン層との間に挿入された埋込み絶縁層を有する、SOI基板を準備するステップと、SOI基板の前面から埋込み絶縁層を貫通して延びる埋込みコンタクト・プラグを含む集積回路を、SOI基板の前記前面に形成するステップと、裏面エッチング・プロセスを実施してバルク・シリコン層内にトレンチを形成し、埋込みコンタクト・プラグの端部を埋込み絶縁層の裏表面に露出させるステップと、第1キャパシタ・プレートと、第2キャパシタ・プレートと、該第1及び第2キャパシタ・プレートの間に挿入されたキャパシタ誘電体層とを含むキャパシタをトレンチ内に形成するステップとを含み、第1キャパシタ・プレートは、埋込みコンタクト・プラグの露出した端部に接触するように形成される。

(もっと読む)

半導体集積回路及び半導体集積回路の設計方法

【課題】半導体集積回路の回路面積を小さくする。

【解決手段】被試験回路2の観測対象の複数の信号線TA1〜TA4上の観測点TP1〜TP4を複数の入力端子に接続し、複数の信号線TA1〜TA4を伝搬する値の、論理積、論理和、否定論理積、または否定論理和の何れかを演算し、複数の信号線TA1〜TA4の何れかを伝搬する値に応じた出力値を出力する論理回路(NOR回路3,NAND回路4)を設けることで、複数の観測点をEOR回路を用いて共用する半導体集積回路より回路面積を小さくできる。

(もっと読む)

静電気検出回路

【課題】本発明は、静電気検出回路を提供することを目的とする。

【解決手段】本発明の静電気検出回路は、電源線と接地線との間に直列に接続されているレジスター及びスイッチユニットを備え、前記電源線に静電気が存在する場合、前記スイッチユニットはオンされて、前記レジスターの両端に検出電圧が生じ、前記検出電圧は、静電気保護回路を動作させて静電気を除去するか、又は制御回路を動作させてデータを保存する。

(もっと読む)

121 - 130 / 9,686

[ Back to top ]