国際特許分類[H01L27/04]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 1つの共通基板内または上に形成された複数の半導体構成部品または他の固体構成部品からなる装置 (52,733) | 整流,発振,増幅またはスイッチングに特に適用される半導体構成部品を含むものであり,少なくとも1つの電位障壁または表面障壁を有するもの;少なくとも1つの電位障壁または表面障壁を有する集積化された受動回路素子を含むもの (38,321) | 基板が半導体本体であるもの (36,153)

国際特許分類[H01L27/04]の下位に属する分類

複数の個々の構成部品を反復しない形で含むもの (2,326)

1種類の半導体構成部品だけを含むもの (8,288)

複数の個々の構成部品を反復した形で含むもの (15,853)

国際特許分類[H01L27/04]に分類される特許

91 - 100 / 9,686

半導体装置

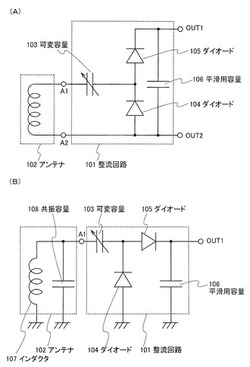

【課題】半導体素子が有する寄生容量や寄生インダクタンスによる電力の損失を抑えるこ

とが出来る、整流回路の提供を課題とする。

【解決手段】入力された交流電圧の振幅に従い、前段の回路と該整流回路の間におけるイ

ンピーダンスを整合または不整合にする。入力される交流電圧が規定の振幅以下である場

合は、インピーダンスを整合にし、該交流電圧をそのまま整流回路に印加する。逆に入力

される交流電圧が規定の振幅よりも大きい場合は、インピーダンスを不整合にし、反射に

より該交流電圧の振幅を小さくしてから整流回路に印加する。

(もっと読む)

半導体装置の製造方法

【課題】レーザを照射して不純物を活性化させる半導体装置の製造方法において、半導体基板の裏面に凹凸が形成されることを抑制することができる半導体装置の製造方法を提供する。

【解決手段】半導体基板3aを用意し、半導体基板3aの裏面から活性化層12、13を構成するための不純物をイオン注入するイオン注入工程を行う。その後、半導体基板3aの裏面から、第1レーザ18aと、第1レーザ18aよりエネルギーが低くされていると共に波長が長くされており、第1レーザ18aの照射スポットと少なくとも一部が重なる照射スポットとされた第2レーザ18bとを同時に照射しながら走査し、第1レーザ18aによって不純物を活性化させて活性化層12、13を形成する活性化工程を行う。

(もっと読む)

半導体装置

【課題】静電破壊による歩留まりの低下を防ぐことができる半導体装置。

【解決手段】複数の画素を選択するための信号を走査線に供給する走査線駆動回路が、上記信号を生成するシフトレジスタを有しており、上記シフトレジスタにおいて、複数のトランジスタのゲート電極として機能する一の導電膜を複数に分割し、上記分割された導電膜どうしを、分割された導電膜と異なる層に形成された導電膜により、電気的に接続する構成を有する。上記複数のトランジスタには、シフトレジスタの出力側のトランジスタが含まれるものとする。

(もっと読む)

スキャン・チェーン用動的クロック領域バイパス

【課題】スキャン・テスト回路およびスキャン・テスト回路を使用して試験を受けるさらなる回路を備える集積回路を提供すること。

【解決手段】スキャン・テスト回路は、それぞれ別個のクロック領域に関連した複数のサブチェーンを有する少なくとも1つのスキャン・チェーン、および1つまたは複数のサブチェーンを選択的にバイパスするように構成されたクロック領域バイパス回路を備える。スキャン・チェーンは、スキャン・シフト・モードの動作において、サブチェーンを全部よりは少なく含む直列シフト・レジスタを形成するように構成可能であり、サブチェーンの少なくとも残りの1つが、スキャン・シフト・モードにおいて直列シフト・レジスタの部分でないように、クロック領域バイパス回路によりバイパスされる。特定のクロック領域に関連するスキャン・チェーンの部分を選択的にバイパスすることにより、クロック領域バイパス回路は、スキャン・テスト期間の試験時間と電力消費を減らす役割を果たす。

(もっと読む)

半導体装置およびその試験方法

【課題】ワイヤボンディング時のストレスでボンディングパッド下の絶縁層のダメージを電気的に検出できる半導体装置および導入されたダメージを検出して良品、不良品を判定できる半導体装置の試験方法を提供すること。

【解決手段】酸化膜4上にポリシリコン5を配置し、このポリシリコン5にpnダイオード9を形成し、nカソード層6上に層間絶縁膜10を挟んで第1ボンディングパッド11を配置する。また、pアノード層7上に第2ボンディングパッド12を配設することで、層間絶縁膜10に導入されるダメージが層間絶縁膜10を貫通するか否かを電気的に検出できる半導体装置(パワーICなど)とすることができる。

(もっと読む)

半導体装置および半導体パッケージ

【課題】パッドが設けられた面の向きを変えても、パッドを基板に接続するボンディングワイヤが交差しない半導体装置を提供する。

【解決手段】複数のパッドを含む第1のパッド群と、第1のパッド群に平行に一列に配置された複数のパッドを含む第2のパッド群と、第1のパッド群を基準にして第2のパッド群とは反対側に設けられた複数のバッファ回路を含む第1のバッファ回路群と、第2のパッド群を基準にして第1のパッド群とは反対側に設けられた複数のバッファ回路を含む第2のバッファ回路群と、第1のパッド群の複数のパッドのそれぞれを第2のバッファ回路群の複数のバッファ回路のそれぞれに対応して接続する複数の第1の配線と、第2のパッド群の複数のパッドのそれぞれを第1のバッファ回路群の複数のバッファ回路のそれぞれに対応して接続する複数の第2の配線と、を有する。

(もっと読む)

リドライバIC、半導体装置、及びその製造方法

【課題】低損失で差動信号を伝送することができるリドライバIC、半導体装置、及びその製造方法を提供する。

【解決手段】本実施の形態に係る半導体装置は、差動信号が伝送される差動配線が形成された配線基板10と、配線基板10に搭載され、外部機器に対して差動信号を送受信するコネクタ11と、配線基板10に搭載され、コネクタ11から受信した差動信号を中継する受信系のリドライバIC21と、受信系のリドライバIC21と離間した位置において配線基板10に搭載され、コネクタ11に送信する差動信号を中継する送信系のリドライバIC20と、を備えるものである。

(もっと読む)

半導体集積回路

【課題】不具合の発生が抑制された半導体集積回路を提供する。

【解決手段】電圧レベルの高いHi信号、及び、該Hi信号よりも電圧レベルの低いLo信号が異なるタイミングで入力される第1入力端子と、Hi信号が常時入力される第2入力端子と、第1入力端子のHi信号によって第1動作状態、第1入力端子のLo信号によって第2動作状態に制御される素子と、を有する半導体集積回路であって、第2入力端子とグランドとの間にスイッチング素子が設けられており、該スイッチング素子は、第1入力端子にHi信号が入力されている時にOFF状態、第1入力端子にLo信号が入力されている時にON状態となる。

(もっと読む)

給電電圧の変動を吸収する電源構造を持つ集積回路

【課題】給電ユニット(エナジーハーベスティングデバイス)に改変を加えること無く、不安定な給電電圧、特に、低い給電電圧ででも正常に動作する、回路ユニットを含む集積回路を提供する。

【解決手段】本発明に係る集積回路は、外部電源に接続された第1の電源リングで囲まれた第1の回路ブロックと、第1の電源リングを介して前記外部電源に接続された第2の電源リングで囲まれた第2の回路ブロックとを含み、第1の回路ブロック内の半分以上が同期回路で構成され、第2の回路ブロック内の半分以上が非同期回路で構成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】固相拡散接合により、プロセス温度が低温化され、プロセス時間が短縮化され、かつフリップチップ構造の半導体装置提供する。

【解決手段】絶縁基板8と、絶縁基板8上に配置された信号配線電極12と、絶縁基板8上に若しくは絶縁基板8を貫通して配置されたパワー配線電極16と、絶縁基板8上にフリップチップに配置され、半導体基板26と、半導体基板26の表面上に配置されたソースパッド電極SPおよびゲートパッド電極GPと、半導体基板26の裏面上に配置されたドレインパッド電極36とを有する半導体デバイス10と、ゲートパッド電極GP上に配置されたゲートコネクタ18と、ソースパッド電極SP上に配置されたソースコネクタ20とを備え、ゲートコネクタ18とゲートパッド電極GPおよび信号配線電極12、ソースコネクタ20とソースパッド電極SPおよびパワー配線電極16は、固相拡散接合される半導体装置1。

(もっと読む)

91 - 100 / 9,686

[ Back to top ]