国際特許分類[H01L27/04]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 1つの共通基板内または上に形成された複数の半導体構成部品または他の固体構成部品からなる装置 (52,733) | 整流,発振,増幅またはスイッチングに特に適用される半導体構成部品を含むものであり,少なくとも1つの電位障壁または表面障壁を有するもの;少なくとも1つの電位障壁または表面障壁を有する集積化された受動回路素子を含むもの (38,321) | 基板が半導体本体であるもの (36,153)

国際特許分類[H01L27/04]の下位に属する分類

複数の個々の構成部品を反復しない形で含むもの (2,326)

1種類の半導体構成部品だけを含むもの (8,288)

複数の個々の構成部品を反復した形で含むもの (15,853)

国際特許分類[H01L27/04]に分類される特許

141 - 150 / 9,686

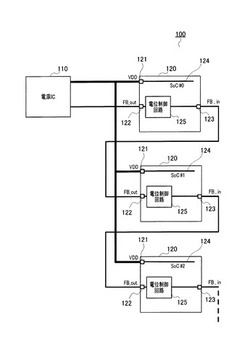

半導体集積回路、電子機器及びマルチチップ半導体パッケージ

【課題】比較的簡単な構成でありながらも動的で高分解能の電圧制御可能な半導体集積回路、電子機器及びマルチチップ半導体パッケージを提供すること。

【解決手段】電子機器100は、電源IC110と、電源IC110から出力される電源電圧Vsrcで動作するSoC#0〜2とを備える。SoC#0〜2は、三次元実装されたマルチチップ半導体パッケージに搭載される。SoC#0〜2は、第3の端子123から入力されるアナログ制御信号の電位と、内部配線124の電位とに基づいて、第2の端子122から出力するアナログ制御信号を生成する電位制御回路125と、電源フィードバック(FB)電圧入力端子である第2の端子122及び第3の端子123と、を備える。SoC#0〜2は、FB出力端子FB_out/FB入力端子FB_inをカスケード接続し、最終段のSoC#0のFB出力を電源IC110に接続している。

(もっと読む)

半導体装置、半導体ウェハ及び半導体装置の製造方法

【課題】ダイシングの際にクラック発生を抑制できる半導体装置を提供する。

【解決手段】半導体基板の上に形成された複数の配線層と、前記複数の配線層の間に配置されたビア層と、前記複数の配線層に形成された導電膜と、前記ビア層の上下の前記配線層の前記導電膜と接続するビアプラグV5とを有し、スクライブ領域31は、チップ領域の外周であって前記半導体基板の縁に接して位置し、前記スクライブ領域31は前記縁に接するパッド領域33を有し、前記パッド領域33は、前記複数の配線層の各々に、平面視において相互に重なって配置され、前記複数の配線層は、第1の配線層と第2の配線層を有し、前記第1の配線層の前記導電膜は、前記パッド領域33の全面に形成された第1の導電パターン55を有し、前記第2の配線層の前記導電膜は、前記パッド領域の一部に形成された第2の導電パターン50を有する。

(もっと読む)

半導体装置

【課題】バイアスに依存した抵抗値の変化をさらに低減できるようにした半導体装置を提供する。

【解決手段】N型シリコン層3と、N型シリコン層3上に形成されたP型拡散抵抗7と、P型拡散抵抗7上に形成されたシリコン酸化膜11と、シリコン酸化膜11を貫いてP型拡散抵抗7の一方の端部7aに接続され、一方の端部7aに高電位を印加するための高電位用電極15と、シリコン酸化膜11を貫いてP型拡散抵抗7の他方の端部7bに接続され、他方の端部7bに低電位を印加するための低電位用電極17と、を備える。高電位用電極15及び低電位用電極17はそれぞれシリコン酸化膜11上に延設されると共に、シリコン酸化膜11上において高電位用電極15と低電位用電極17との間にはスリット21が設けられている。このスリット21は、P型拡散抵抗7の一方の端部7aと他方の端部7bとの間の中間位置23よりも一方の端部7aに近い側に位置する。

(もっと読む)

半導体装置

【課題】

アバランシェ耐量の増大と、オン抵抗の低減とを兼ね備えた半導体装置を提供することである。

【解決手段】

実施形態の半導体装置は、第1半導体層を含む半導体基板と、前記半導体基板内に設けられた複数の第2半導体層と、前記半導体基板の一方の表面側に設けられた複数の第3半導体層と、前記第3半導体層の表面に選択的に形成された第4半導体層と、前記第4半導体層の表面側に設けられた制御電極と、前記第1半導体層の他方の表面に設けられた第6半導体層とを有するMOSと、前記半導体基板の一方の表面側に設けられた第5半導体層と、前記第1半導体層と、前記第2半導体層と、前記第6半導体層を含んで構成され、前記第5半導体層に接続するクランプ電極に接続された第1ダイオードと、前記制御電極に接続された第7半導体層を含んで構成され、前記第1ダイオードと逆直列になるように前記クランプ電極に接続された第2ダイオードとを有する。

(もっと読む)

半導体装置

【課題】所望のブレークダウン電圧が確保でき、大きな放電電流を流すことが可能なESD保護特性のすぐれたESD保護素子を実現する。

【解決手段】適切な不純物濃度のN+型埋め込み層2とP+型埋め込み層3でPN接合ダイオード35を形成する。P+型埋め込み層3はP+型引き出し層5と一体となりN−型エピタキシャル層4を貫通させアノード電極10と接続される。P+型埋め込み層3等で囲まれたN−型エピタキシャル層4にN+型拡散層7と該N+型拡散層7と接続され、これを取り囲むP+型拡散層6を形成する。N+型拡散層7、P+型拡散層6はカソード電極9に接続される。P+型拡散層6をエミッタ、N−型エピタキシャル層4をベース、P+型引き出し層5等をコレクタとする寄生PNPバイポーラトランジスタ38とPN接合ダイオード35でESD保護素子を構成する。

(もっと読む)

チャージポンプ及びこれを用いた電源装置

【課題】プリント配線基板上の実装面積削減やコスト削減を実現することのできるチャージポンプを提供する。

【解決手段】チャージポンプ100は、フライングキャパシタ120の充放電用スイッチとして、半導体装置110に集積化されたフローティングNMOSFET111及び112のボディダイオード111d及び112dを用いる。

(もっと読む)

半導体装置

【課題】半導体装置で発生する異常発熱をより確実に検出し得る構造を有する半導体装置を提供する。

【解決手段】半導体装置2は、半導体素子10と、一対の信号パッド12、14と、温度検出ダイオードD1〜D5と、を備える。温度検出ダイオードD1〜D5は、それぞれ、一対の信号パッド12、14間に並列に接続されている。そのため、一対の信号パッド12、14間に一定の電圧を印加すると、温度検出ダイオードD1〜D5のそれぞれにおいて、温度検出ダイオードD1〜D5の近傍の温度に応じた電流I1〜I5が流れる。従って、一対の信号パッド12、14間を流れる電流Iは、各温度検出ダイオードD1〜D5を流れた電流I1〜I5の和となる。

(もっと読む)

半導体装置及びそれを用いたSiPデバイス

【課題】高耐圧の能動素子を含む回路と低電圧で動作するロジック回路とが同一基板上に混載された半導体装置を低コストで実現する。

【解決手段】半導体装置が、ロジック回路50と、能動素子回路とを具備している。ロジック回路50は、半導体基板1に形成された半導体素子2を備えている。該能動素子回路は、半導体基板1の上方に形成された拡散絶縁膜7−1の上に形成された半導体層8−1、8−2を用いて形成されたトランジスタ21−1、21−2を備えている。この能動素子回路がロジック回路50により制御される。

(もっと読む)

半導体設計方法及び半導体設計装置

【課題】フリップフロップ追加による利益と、スキャンFFの段数増加による不利益と、を考慮に入れ、スキャンテスト回路の設計を行う半導体設計方法が、望まれる。

【解決手段】複数のスキャンFFから構成されるスキャンテスト回路の設計方法は、複数のスキャンFF間の遅延値を抽出することで、スキャンテスト回路の動作レート候補値を複数算出する第1の工程と、中継用フリップフロップの追加を仮定し、複数の動作レート候補値をそれぞれ使用して、スキャンテストの実施に必要な時間をスキャンシフト時間として算出し、スキャンシフト時間に基づき、中継用フリップフロップを追加することの効果が最も高い動作レート候補値を、中継用フリップフロップの追加後のスキャンテスト回路に適用する動作レートとして選択する第2の工程と、動作レートを満たすように、複数のスキャンFF間に中継用フリップフロップを追加する第3の工程と、を含んでいる。

(もっと読む)

半導体装置

【課題】配線間の影響を抑制することができる多層配線を有する半導体装置を実現する。

【解決手段】本発明の実施形態における半導体装置は、下層の配線層に第1の方向に沿って形成された信号配線11と、下層の配線層と絶縁膜を介して配置される上層の配線層に第1の方向と交差する第2の方向に沿って形成された基準電位配線13と、 上層の配線層に基準電位配線13に沿って近接して形成されたシールド線14a、14bと、を有し、信号配線11と基準電位配線13の交差部15cにおいて基準電位配線13とシールド線14a、14bとの距離が他の部分に比べてより狭くなっていることを特徴とする。

(もっと読む)

141 - 150 / 9,686

[ Back to top ]