国際特許分類[H01L27/105]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 1つの共通基板内または上に形成された複数の半導体構成部品または他の固体構成部品からなる装置 (52,733) | 整流,発振,増幅またはスイッチングに特に適用される半導体構成部品を含むものであり,少なくとも1つの電位障壁または表面障壁を有するもの;少なくとも1つの電位障壁または表面障壁を有する集積化された受動回路素子を含むもの (38,321) | 基板が半導体本体であるもの (36,153) | 複数の個々の構成部品を反復した形で含むもの (15,853) | 電界効果構成部品を含むもの (11,969)

国際特許分類[H01L27/105]の下位に属する分類

ダイナミックランダムアクセスメモリ構造 (2,482)

スタティックランダムアクセスメモリ構造 (855)

リードオンリーメモリ構造 (4,422)

国際特許分類[H01L27/105]に分類される特許

11 - 20 / 4,210

磁気抵抗効果素子、および磁気ランダムアクセスメモリ

Notice: Undefined index: from_cache in /mnt/www/gzt_ipc_list.php on line 285

半導体装置

Notice: Undefined index: from_cache in /mnt/www/gzt_ipc_list.php on line 285

磁気抵抗素子の製造方法

Notice: Undefined index: from_cache in /mnt/www/gzt_ipc_list.php on line 285

液体噴射ヘッド、液体噴射装置及び圧電素子

Notice: Undefined index: from_cache in /mnt/www/gzt_ipc_list.php on line 285

記憶素子、記憶装置

【課題】書き込みエラーを生じることなく、短い時間で書き込み動作を行うことができる記憶素子及び記憶装置を提供する。

【解決手段】情報に対応して磁化の向きが変化される記憶層14と、磁化の向きが固定された磁化固定層12と、上記記憶層14と上記磁化固定層12との間に配された非磁性体による中間層13と、垂直磁気異方性誘起層15とを含む層構造を有する記憶素子3を構成する。そして、上記記憶層14が、第1の強磁性層14aと第1の結合層14bと第2の強磁性層14cと第2の結合層14dと第3の強磁性層14eとが同順に積層されて、上記第1の強磁性層14aが上記中間層13に接し、上記第3の強磁性層14eが上記垂直磁気異方性誘起層15に接し、上記結合層14b,14dを介して隣接する上記強磁性層14a,14c,14eの磁化の向きが膜面に垂直な方向から傾斜している。

(もっと読む)

有機分子メモリおよび有機分子メモリ用有機分子

【課題】メモリ保持特性に優れた有機分子メモリを提供する。

【解決手段】実施の形態の有機分子メモリは、第1の導電層と、第2の導電層と、第1の導電層と第2の導電層との間に設けられ、分子軸に沿ってπ電子系が拡がっている分子骨格を持つ分子系において、(I)分子の最高被占軌道(HOMO)と最低空軌道(LUMO)のうちいずれか一方が分子軸にそって非局在化し、他方が分子軸に対して局在化している、(II)分子の最高被占軌道(HOMO)エネルギー準位が−5.75eV以上の値を持つ、を同時に満たす分子群より選ばれる有機分子を含む有機分子層と、を備える。

(もっと読む)

分子メモリ装置の製造方法

【課題】メモリ素子の状態が良好なクロスポイント構造の分子メモリ装置の製造方法を提供する。

【解決手段】実施形態に係る分子メモリ装置の製造方法は、第1方向に延びる複数本の第1配線を含む配線層を形成する工程と、前記配線層上に犠牲膜を形成する工程と、前記犠牲膜上に第2方向に延びる複数本の第1絶縁部材を形成する工程と、前記第1絶縁部材の側面上に前記第1配線とは異なる導電材料からなる第2配線を形成すると共に、前記犠牲膜における隣り合う前記第1絶縁部材間であって前記第2配線間の直下域に相当する部分を除去する工程と、隣り合う前記第1絶縁部材間であって前記第2配線間に複数本の第2絶縁部材を前記配線層に接するように形成する工程と、前記犠牲膜を除去することによりギャップを形成する工程と、前記ギャップ内に、前記第1配線及び前記第2配線のうちの一方に結合し他方には結合しない分子材料を形成する工程と、を備える。

(もっと読む)

メモリ用途のセレクタデバイス

【課題】本発明は、メモリ用途のセレクタデバイスに関する。

【解決手段】本発明に係るセレクタデバイスは、MIT素子およびこれに熱的に連動する分割ヒータを備えたメモリアレイ内のメモリ素子を選択するためのセレクタデバイスであって、MIT素子は、MIT材料構成要素とバリア構成要素とを有し、分割ヒータを用いて相転移温度より高い温度に加熱されることにより、高抵抗状態から低抵抗状態に切り換え可能であり、バリア構成要素は、高抵抗状態にあるMIT素子の抵抗値を大きくするように構成されたことを特徴とするものである。セレクタデバイス。

(もっと読む)

液体噴射ヘッド及び液体噴射装置並びに圧電素子

【課題】環境負荷が小さく、歪量が大きい液体噴射ヘッド、液体噴射装置及び圧電素子を提供する。

【解決手段】圧電体層70と圧電体層70に設けられた電極60,80とを具備する圧電素子300を備え、圧電体層70は、ビスマス、鉄、バリウム及びチタンを含みペロブスカイト構造を有する複合酸化物からなり、圧電体層70に駆動電圧Vaを印加したときの変位量をZmax、その後印加電圧を0Vにしたときの変位量をZ0としたとき、(Zmax−Z0)/Vaが70pm/V以上且つ比誘電率が700以下である。

(もっと読む)

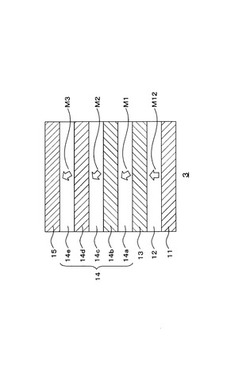

半導体装置及びその製造方法

【課題】半導体基板上の複数の半導体層のうちの1つを正確に選択する。

【解決手段】実施形態に係わる半導体装置は、第1乃至第3の半導体層12−1〜12−3と、第1乃至第3の半導体層12−1〜12−3のうちの1つを選択するレイヤー選択トランジスタ15(LST)とを備える。第1のノーマリーオン領域17−1は、第1の半導体層12−1内において第1乃至第3のゲート電極16−1〜16−3に隣接するチャネルをノーマリーオンチャネルにし、第2のノーマリーオン領域17−2は、第2の半導体層12−2内において第2乃至第4のゲート電極16−2〜16−4に隣接するチャネルをノーマリーオンチャネルにし、第3のノーマリーオン領域17−3は、第3の半導体層12−3内において第3乃至第5のゲート電極16−3〜16−5に隣接するチャネルをノーマリーオンチャネルにする。

(もっと読む)

11 - 20 / 4,210

[ Back to top ]